寄生电容的定义

寄生电容影响电路机理

消除寄生电容的方法

当你想到寄生虫时,你可能会想到生物学上的定义——一种生活在宿主身上或在宿主体内的有机体,从宿主身上吸取食物。从这个意义上说,寄生虫可能是巨大的麻烦或导致严重的健康问题。

当然,作为一个PCB设计人员,您可能知道另一种寄生虫—寄生电容。虽然您不必担心电路中的生物寄生,但了解如何消除寄生电容可以帮助提高PCB设计中的信号完整性和性能。

什么是寄生电容?

寄生电容是一种现象,即电路中的元件在物理上不是电容时表现得像电容。如果回顾一下电容的基础知识,就更容易理解寄生电容的概念。 电容器由被绝缘材料隔开的两个导电元件组成。当两个导体都受到差电位的驱动时,电荷就在它们之间积累起来。积聚的电荷用电容表示,公式为C = q/V。 物理电容器是根据上述原理构造的,目的是有意地在电路中储存电荷。然而,电容也可能存在于电路的元件之间,只要元件之间的距离符合形成电荷的要求。 电路中形成的非预期电容称为寄生电容。寄生电容可以在两个导体、衬垫、导体和相邻地平面之间,或任何两个满足电荷积聚标准的元素之间产生。当电路的各部分相互接近且电压水平不同时,寄生电容的可能性最大。

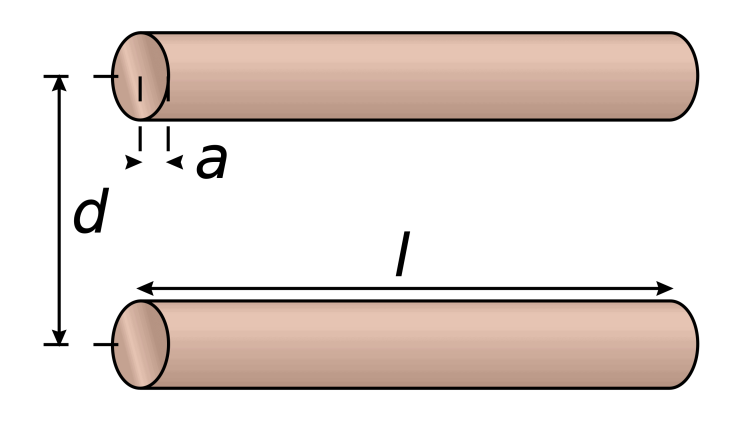

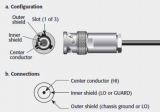

导体间寄生电容是面积与距离的关系

上图显示了电路中两个导体之间的电容是如何产生的。当导体被置于不同的电位水平时,所积聚的电荷由下式决定: C= (Ɛ×a) /d,其中Ɛ为导体之间绝缘体的介电常数。

寄生电容影响电路的机理?

在高频时,寄生电容会导致短路。

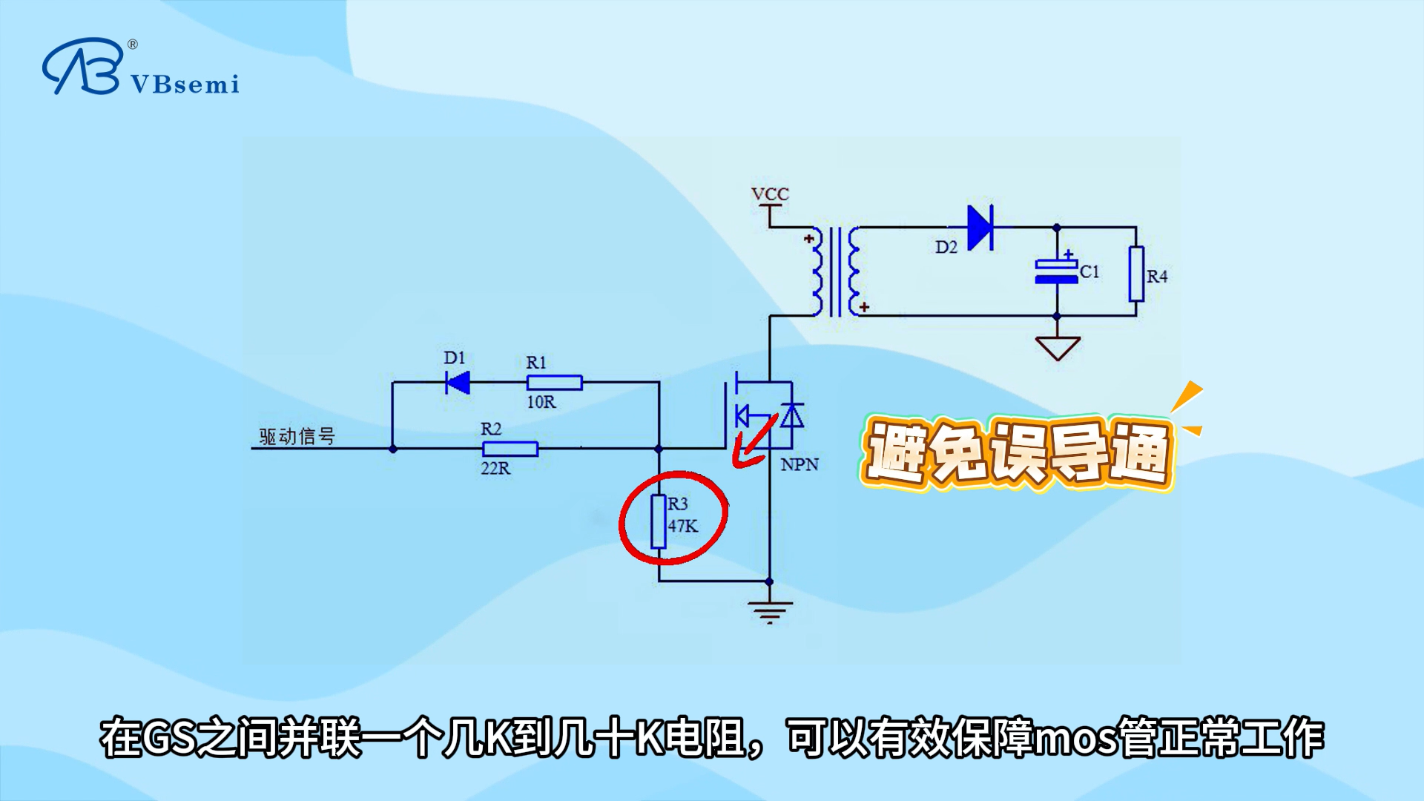

寄生电容很可能存在于电路中,对于低频设计,它不太可能造成重大的问题。然而,寄生电容在高速设计中可能就必须被重视。 随着频率的增加,电容的行为发生变化,最后,可能会形成一个短路的行为。当高速信号通过一个元件时,寄生电容也会产生同样的效果。 在放大器设计中,在输入和输出之间形成的寄生电容可能导致不必要的反馈。通常的开路电路在高频工作时变得导电,并在放大器电路中引起不必要的振荡或寄生振荡。 寄生电容对于两个相邻的导体来说是很麻烦的。当其中一个导体携带高频信号时,它会给另一个导体带来串扰。寄生电容越大,EMI噪声越大。 寄生电容不仅会产生干扰,还会影响信号本身的完整性。例如,寄生电容可以建立在导体和地平面之间。在高频时,两个元件都趋向于短路,并将改变导体上的信号。

消除寄生电容的方法?

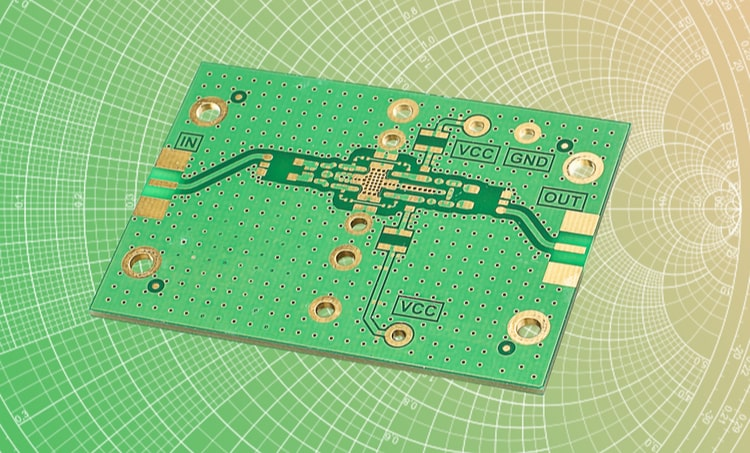

去除内地层,有助于降低寄生电容

考虑到在许多PCB设计中电路密度持续增加,消除寄生电容是不可能的。但是,您可以通过应用这些策略来减少它的影响。

01

增加导体之间的间隙

如果可能的话,在设计中使得布线之间保持尽量宽的间隙。这是因为,电容与导体之间的距离成反比。较宽的间隙将降低寄生电容和交叉耦合等影响。

02

适当的使用地平面

建议使用内层接地面,以减少杂散电感、EMI和散热,但请记住,它也可能增加寄生电容。在用地平面覆盖整个内层之前,需要考虑一下利弊。

03

减少过孔

在构建紧凑的PCB时,过孔是有用的,但过孔过多会引入显著的寄生电容。少用过孔,并尽量避免任何高速线上打过孔。

Cadence提供全套的PCB设计工具,仿真工具以确保PCB设计一次成功。

此外,我公司战略合作伙伴北京迪浩永辉技术有限公司推出了CMS Schematic Audit-原理图设计规则、规范性自动化分析软件;CMS DesignPlus-PCB以及芯片封装设计以及工艺规则自动化分析软件完全集成Cadence工具集,在设计软件中实现In-Design分析,软件具有高度可扩展性,使得用户结合自身产品形成特有的规则知识库可随时加入软件中,以促进设计效率的提高。

-

电容

+关注

关注

100文章

6525浏览量

160101

发布评论请先 登录

TH2839阻抗分析仪在LED驱动集成电路寄生参数测试分析中的应用

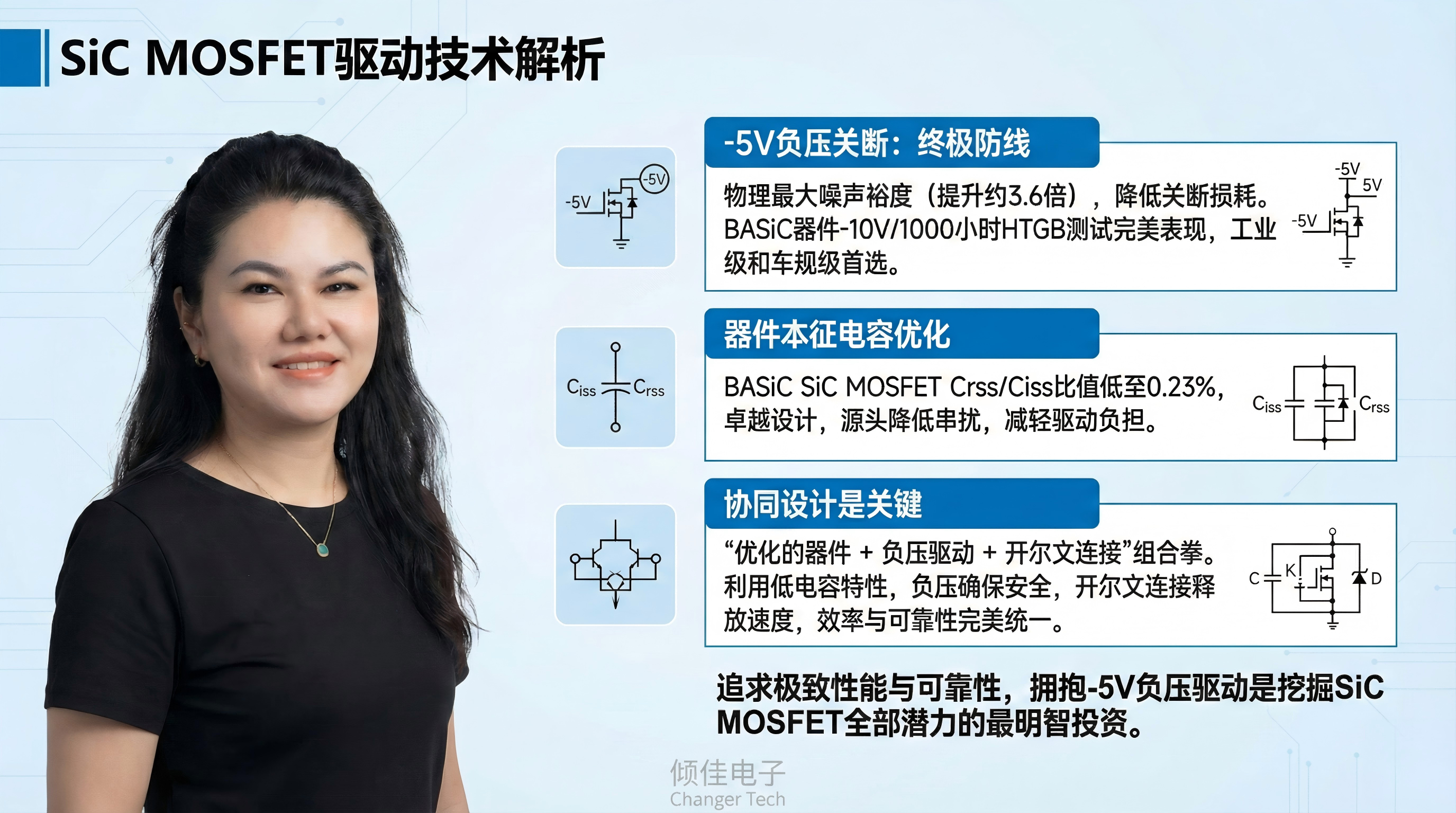

碳化硅MOSFET串扰抑制策略深度解析:负压关断与寄生电容分压的根本性优势

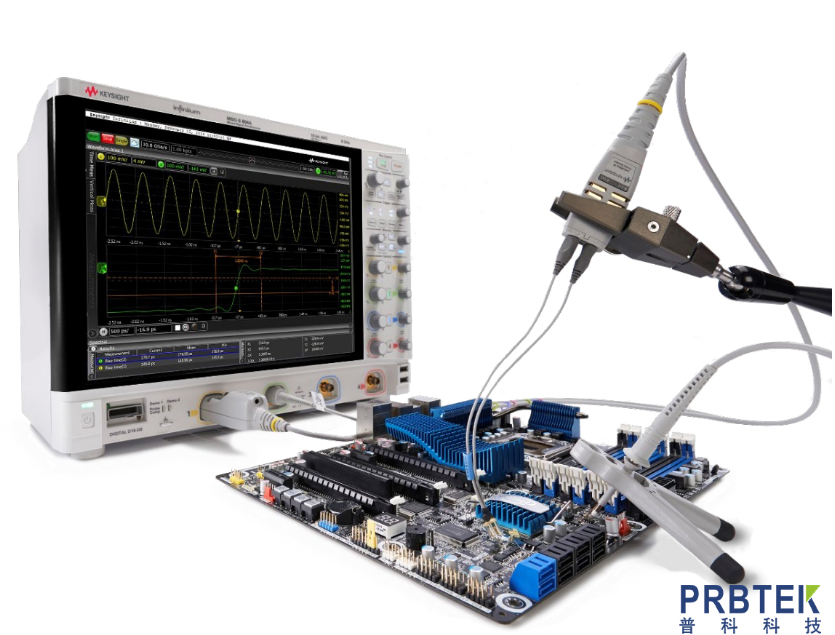

高速示波器时延校准实操:单边单信号法从准备到验证的全步骤指南

电源功率器件篇:线路寄生电感对开关器件的影响

KiCad-Parasitics:KiCad 寄生参数分析插件

示波器无源探头补偿调试全指南

逆变器寄生电容对永磁同步电机无传感器控制的影响

面向高电容连接的低电流I-V表征测试方案

【干货分享】电源功率器件篇:变压器寄生电容对高压充电机输出功率影响

LCR测试仪中LP(Parallel)与LS(Series)模式的区别

技术资讯 | 在高速设计中如何消除寄生电容?

技术资讯 | 在高速设计中如何消除寄生电容?

评论