本文介绍了时钟扩频技术的原理、分类,结合它在摄像头的具体应用案例,与传统EMI抑制手段的实际效果进行对比,突显时钟扩频技术在抑制时钟EMI上的优势。目前,时钟扩展频谱技术被广泛使用在图像采集、图像

2018-05-18 02:13:00 3137

3137

在多时钟设计中可能需要进行时钟的切换。由于时钟之间可能存在相位、频率等差异,直接切换时钟可能导致产生glitch。

2020-09-24 11:20:38 6410

6410

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期 T,则

2020-11-23 13:08:24 4644

4644

跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。

2020-11-27 11:11:39 6743

6743

信号回沟,即波形边缘的非单调性,是时钟的大忌,尤其是出现在信号的门限电平范围内时,由于容易导致误触发,更是凶险无比。所以当客户测试发现时钟信号回沟,抱着一心改板的沉痛心情找到高速先生时,高速先生

2020-11-26 09:58:01 10822

10822 今天我们将讨论时钟如何影响精密 ADC,涉及时钟抖动、时钟互调和时钟的最佳 PCB 布局实践。

2023-04-11 09:13:22 2034

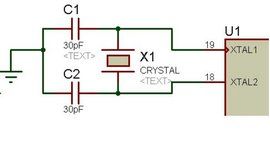

2034 上篇文章我们讲了时钟信号的几个重要参数,今天我们简单讲一下在设计中最常用到的几种时钟信号产生的方法,由于篇幅限制,我们不对具体的原理进行讲述,有兴趣的朋友可以在网上搜索相应的文章进行深入了解,另外

2019-06-05 04:20:28

PLL不仅被广泛用在通信系统中产生方便调节的不同频点的高频率本振信号(LO),还被广泛用在处理器、FPGA、通信器件中用于生成器件内部的高速时钟。USB接口芯片的时钟产生及内部PLLDDS生成任意频率

2019-06-06 04:20:03

了这些寄生信号。整合 BB 滤波器可最大限度地消除这些寄生信号。本文将探讨这些寄生信号是如何出现在调制器输出端的。图 1:OIP3 测量频谱分析仪截图在图 1 所示的频谱分析仪截图中,有两个 RF

2018-09-19 14:43:36

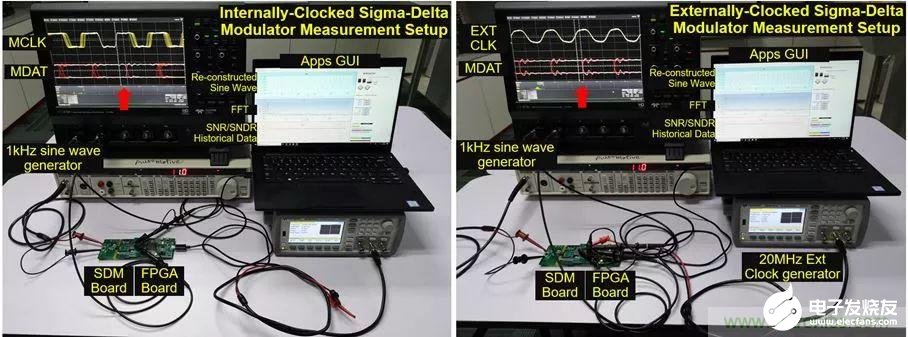

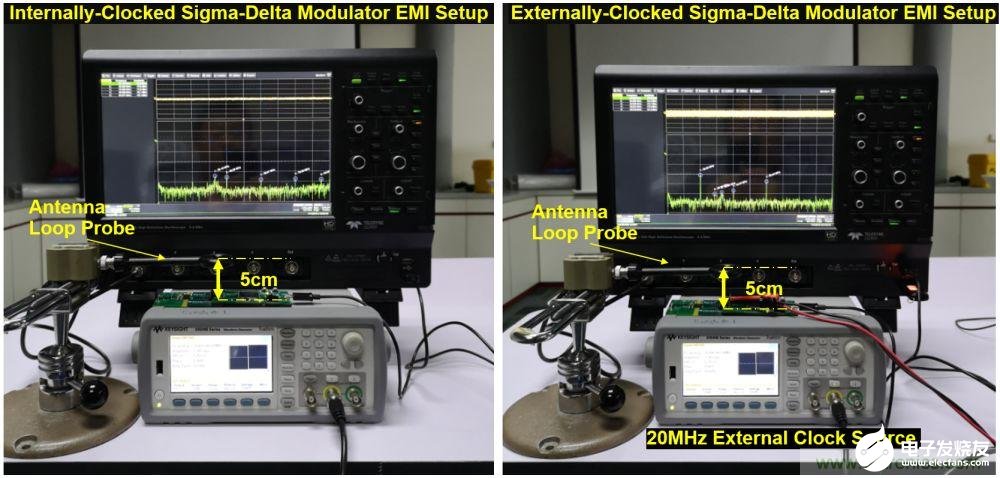

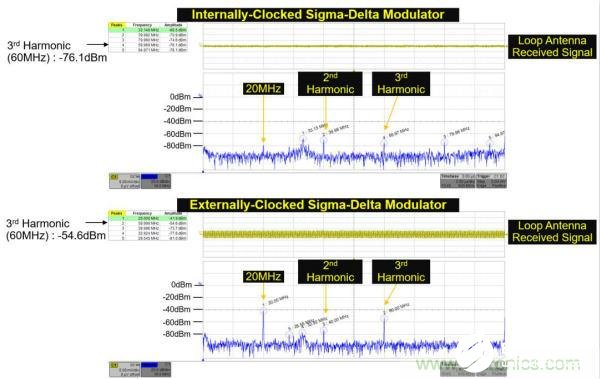

设置,用于测量两类Σ-Δ调制器的时钟信号的EMI从图6中示波器捕获的图像可以清楚看出,外时钟源产生的EMI要高得多,在时钟信号频率及其谐波处达到峰值。例如,对于60MHz的三次谐波,外时钟源产生的EMI比内时钟Σ-Δ调制器输出时钟信号的高20dB。

2020-10-21 16:12:12

速率时钟或数据将被破坏。(使用瞬态脉冲频率为100 kHz。)操作理论电路信息AD7400A隔离∑-Δ调制器将模拟输入信号转换为高速(10 MHz典型)的单位数据流;调制器的单位数据的时间平均值与输入

2020-09-25 17:55:01

什么是时钟脉冲?为什么CPU需要时钟?CPU的时钟信号是如何产生的?

2021-10-20 07:21:14

包括有源晶振、无源晶振、时钟产生器等。MCG 模块提供九种不同的工作模式,分别是:锁频环片内时钟模式( FEI),锁频环片外时钟模式(FEE),锁频环旁路片内时钟模式(FBI),锁频环旁路片外时钟模式

2015-02-10 15:39:48

(HSE,HSI,LSE,LSI)产生的过程比430简单许多,430的几个时钟源(XT1CLK,XT2CLK,VLOCLK,REFOCLK,DCOCLK,DLOCLKDIV)在产生时还有一些基础的配置。二、时钟源产生模块分析1、osc模块这一部分是外接了一个振荡器(可以是手表晶体振荡器、标.

2022-02-15 06:17:26

的基本分析开始,如图1所示。 图 1:Δ-Σ调制器内部框图 调制器根据调制器时钟运行,决定了输入的采样间隔。调制循环通过对输入采样和1位DAC之间的差分进行积分而开始。比较器根据积分器值确定下一个调制器

2019-08-12 04:45:06

我使用FPGA产生一个5MHz的时钟信号,0V-3.3V。为了测试产品的稳定性,需要在这个时钟信号的低电平位置叠加一个脉冲信号,此脉冲信号也是由FPGA产生,频率约为250Mhz。

我的问题是

2024-08-19 07:18:41

扩频时钟调制器DS1081L资料下载内容主要介绍了:DS1081L引脚功能DS1081L功能和特性DS1081L应用范围DS1081L内部方框图DS1081L极限参数DS1081L典型应用电路

2021-04-02 07:34:06

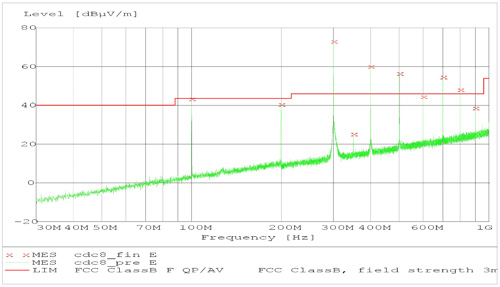

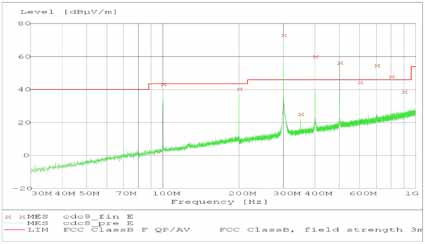

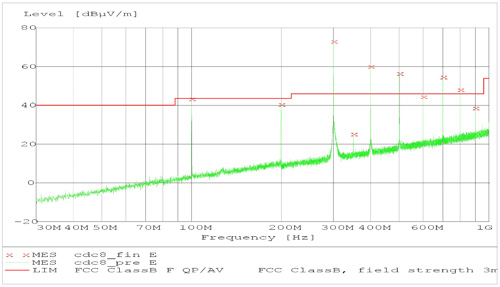

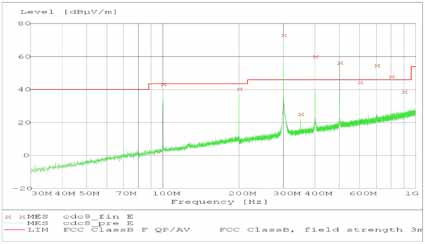

,EMI 可通过频谱分析仪测量,如图1 所示。图中,绿色信号存在一些超出红色 FCC 屏蔽的频率分量(300MHz、400MHz 和 500MHz 等)。 控制时钟引起 EMI 的一些方法都基于上述两种

2018-09-19 14:42:35

MS2400是瑞盟科技推出的一款二阶Σ-Δ调制器,集成片上数字隔离器,能将模拟输入信号转换为高速1位码流。调制器对输入信号连续采样,无需外部采样保持电路。模拟信号输入满量程为±320 mV,转换后

2021-10-12 12:14:32

存在于信号之间的寄生电感/电容,或者通过电源或接地连接的无用耦合,从而产生 EMI;或者2)直接通过电子/磁辐射,即辐射性 EMI。由于两个原因,时钟信号常归咎于 EMI。即使时钟低频率运行,较好的时钟

2022-11-23 06:43:42

我做的一个基于DSP的系统中,DSP做主处理器,控制着整个系统,包括信号处理,整体调度等;选择了一块Xilinx的FPGA做FIFO UART和系统的逻辑控制和译码。DSP的时钟输入为15MHz

2023-06-19 06:43:17

时钟产生和分发设计指南:在您设计时钟电路时是否仅仅因为某些方法在过去一直沿用,所以就采用它呢?或者您曾经使用过某个器件仅仅是因为其他设计中使用了它?这种现象在如

2009-09-06 09:01:45 0

0 应用软件根据BYPASS信号的值来决定是否使用PLL。如果使用PLL,那么它总是输出一个200MHz的时钟信号,并且联合系统分频器(SYSDIV)共同产生系统时钟。馈送到PWM模块的时钟由系

2009-11-07 14:01:59 14

14 16MHZ至134MHZ扩展频谱时钟调制器DS1083L是扩展频谱时钟调制器IC可降低时间数字电子设备的EMI

2010-04-09 15:19:22 18

18

SPWM调制方法对比分析

摘要:对比分析了三种正弦波脉宽调制(SPWM)控制方法,指出各自的优缺点及应用,给出了一些数学

2009-07-06 13:33:51 14120

14120

AD7400: 隔离式Σ-Δ调制器

AD7400*是一款二阶Σ-Δ调制器,采用ADI公司iCoupler®技术的片内数字隔离,能将模拟输入信号转换为高速的1比特数据流。AD7400采用5V电源供

2009-09-25 08:48:40 2505

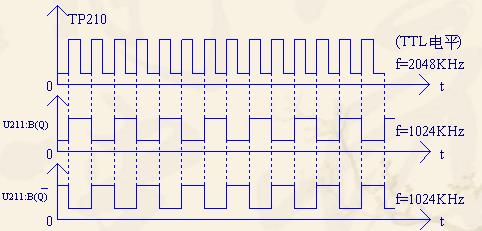

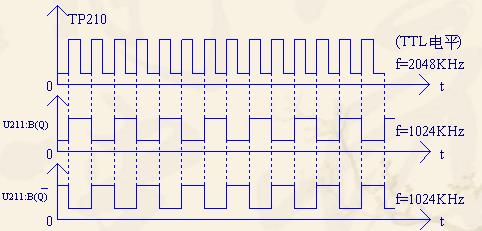

2505 2048KHz(2M)时钟信号产生电路

2009-10-11 10:20:02 3300

3300

控制板级时钟分配期间出现的EMI

今天,我们来谈谈所有电子系统都存在的一种常见问题——电磁干扰也即 EMI,并侧重讨论时钟的影响。

从广义来讲,EMI&n

2010-01-19 11:13:14 2234

2234

控制板级时钟分配期间出现的 EMI

今天,我们来谈谈所有电子系统都存在的一种常见问题——电磁干扰也即 EMI,并侧重讨论时钟的影响。

从广义来讲,EMI 是

2010-01-21 09:36:19 1092

1092

本文简要介绍了SSC扩频时钟的基本概念以及如何使用力科示波器进行信号的扩频时钟的测试。

2011-05-17 11:23:34 6000

6000

所谓门控时钟就是指连接到触发器时钟端的时钟来自于组合逻辑;凡是组合逻辑在布局布线之后肯定会产生毛刺,而如果采用这种有毛刺的信号来作为时钟使用的话将会出现功能上的错

2011-09-07 16:11:32 35

35 应用于高能效电子产品的首要高性能硅方案供应商安森美半导体(ON Semiconductor)推出新系列的有源时钟产生器集成电路(IC),管理时钟源的电磁干扰(EMI)及射频干扰(RFI),为所有依赖于时钟的

2011-10-18 09:11:24 921

921 基于AD9540产生多时钟输出

2011-11-25 00:02:00 31

31 基于片上偏差对芯片性能的影响,分析对比了时钟树设计与时钟网格设计,重点分析了时钟网格抗OCV影响的优点,并利用实际电路应用两种方法分别进行设计对比,通过结果分析,验证

2012-05-07 14:13:14 36

36 ASM3P2182A是一个多才多艺的扩频频率调制器专门为范围广泛的输入时钟频率从25兆赫到210兆赫。 ASM3P2182A可以产生EMI减少时钟从OSC或生成一个系统时钟。 ASM3P2182A

2017-04-06 10:24:19 7

7 SSCG是一种Active且低成本的解决EMI问题的方案,可以在保证时钟信号完整性的基础上应对更广频率范围内EMI问题。相比传统上使用Ferrite Beads和RF Chokes抑制EMI

2018-08-22 14:45:27 10026

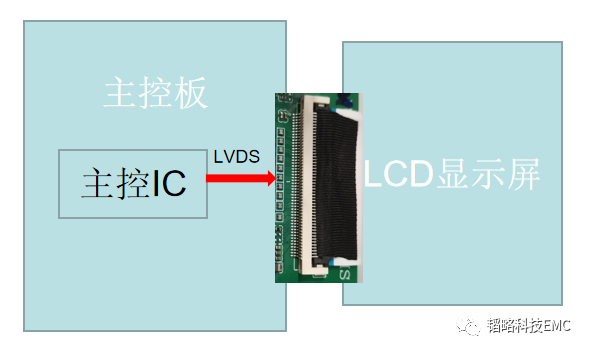

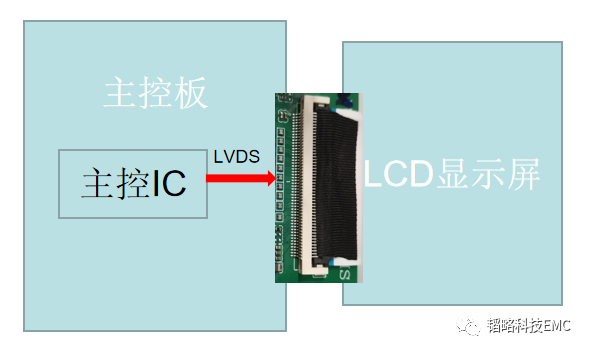

10026 对信号进行调制,将信号能量扩展到一个较宽的频率范围内,能有效的抑制系统的EMI问题。一、具体案列分析:客户的样机是工业类机器人,样机中带屏,屏的时钟取自主芯片。如上图,这是客户没有整改之前测试的实验

2018-11-06 14:53:48 1275

1275 首先,我们看一下时钟信号中最常见到的波形 - 矩形波(尤其是方波更常用)。在较低时钟频率的系统中我们看到的基本上都是以矩形波为主的时钟信号,因为电路基本上都是靠时钟的边沿(上升沿或下降沿)进行

2018-12-06 11:53:10 64395

64395

电子产品多功能化、高速化、小型化的发展,意味着对内部时钟频率的要求将越来越高。因为时钟信号是周期信号,所以在频域上的能量是集中在某个频率上的,这也就造成了时钟EMI测试超标的问题。

2019-02-02 16:25:00 6853

6853 内同步时钟的时钟信号是从驱动端直接发到接收端的。之前的博文提到,共同时钟系统时序裕量较小,频率无法继续提升的一个关键因素之一就是Tco,受限于工艺等因素,这个Tco很难做到太小,比如SDRAM的Tco max一般有5.4ns。

2019-06-05 14:59:45 1664

1664

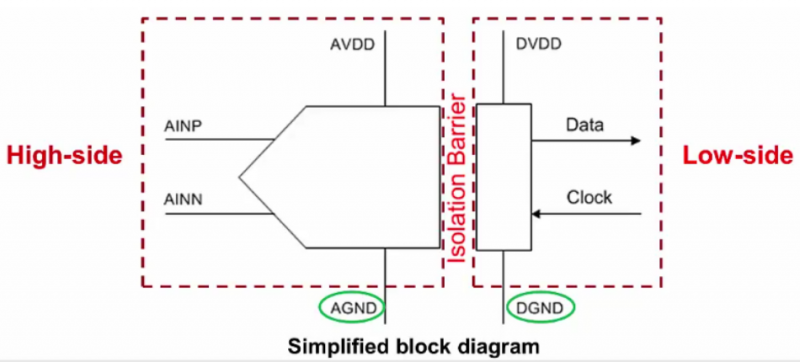

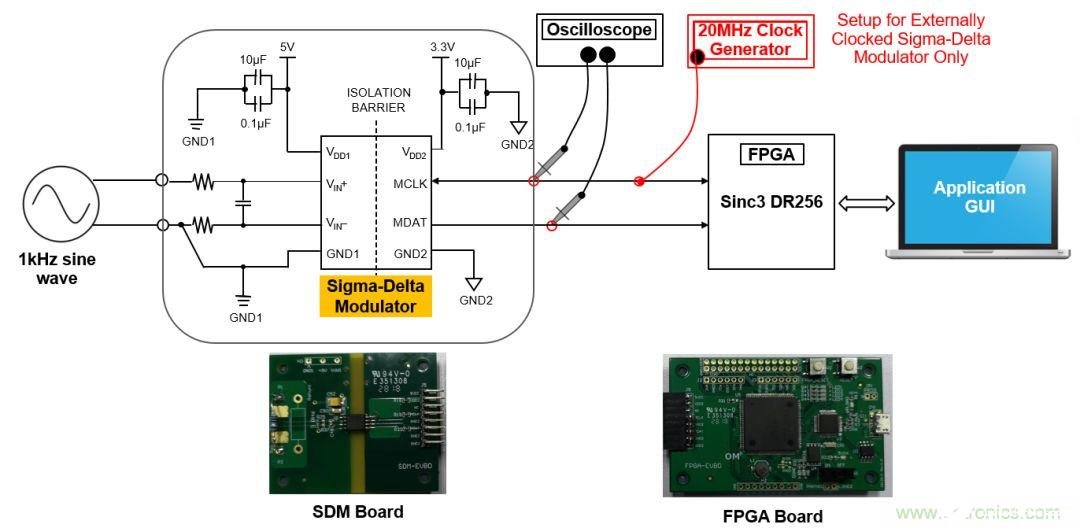

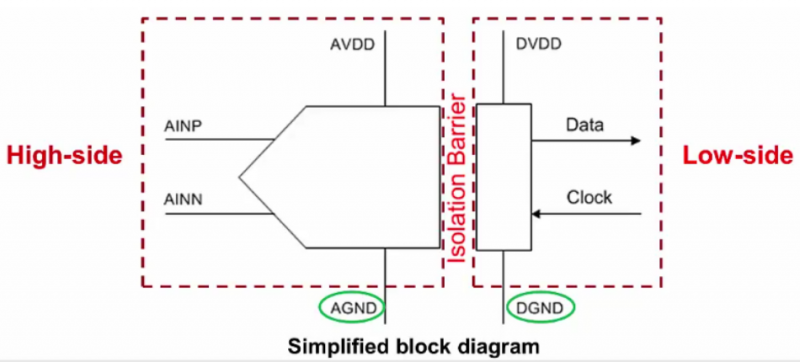

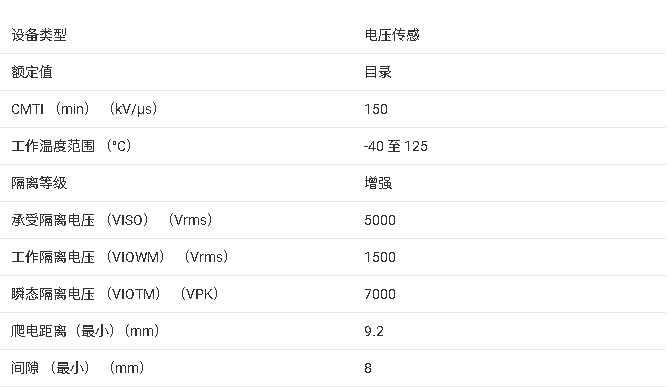

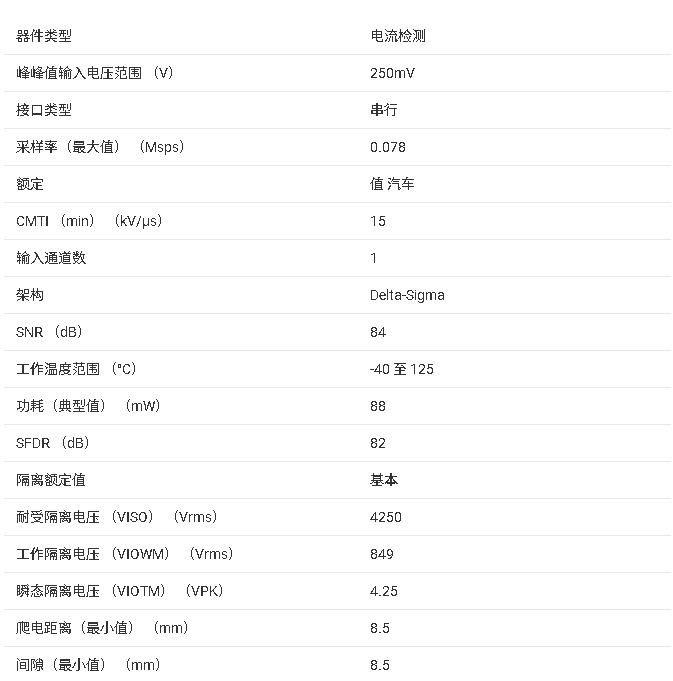

隔离的Σ-Δ调制器长期以来被证明可以在嘈杂的工业电机应用环境中提供非常高的精度和强劲的电流和电压感测能力。有两类隔离型Σ-Δ调制器:一种是在IC内部产生时钟信号;另一种是从外部时钟源接收时钟信号。

2019-07-27 09:22:29 1184

1184 隔离调制器是一种将模拟输入信号转换为由0和1组成的高速数字比特流,同时使用隔离层将输入和输出电路隔离开来的Δ-Σ调制器。该隔离层对电磁干扰有很强的抵抗力,电磁干扰通常称为EMI。干扰由外部源产生且会对电路产生负面影响。

2019-09-14 10:02:00 2441

2441

时钟树不仅可以做到高扇出,还可以做到让时钟信号到达各个触发器的时刻尽可能一致,也即保证时钟信号到达时钟域内不同触发器的时间差最小。

2020-03-08 17:37:00 9341

9341

SSDCI1108AF是减少电磁干扰(EMI)的时钟发生器。利用内调制器对振荡频率进行周期性的微调,可以使不必要的电磁干扰(EMI)峰值衰减。SSDCI1108AF接收来自基本晶体或外部基准的输入时钟,并锁定到该输入时钟,以传递1x调制时钟输出。

2020-04-17 08:00:00 14

14 。 不要随意将内部信号作为时钟,如门控时钟和分频时钟,而要使用CLKDLL或者DCM产生的时钟,或者可以通过建立时钟使能或者DCM产生不同的时钟信号。 FPGA尽量采取同步设计,也就是所有时钟都是同一个源头,如果使用两个没有相位关系的异步时钟,必须

2020-12-11 10:26:44 2426

2426 电子产品多功能化、高速化、小型化的发展,意味着对内部时钟频率的要求将越来越高。因为时钟信号是周期信号,所以在频域上的能量是集中在某个频率上的,这也就造成了时钟EMI测试超标的问题。

2020-11-11 10:33:28 6136

6136 时钟产生模块将选定的时钟源分频,产生多种不同的时钟频率供多个模块使用。例如:总线时钟、FlexBus时钟等。多功能时钟发生器MCG模块为MCU提供了多种时钟源选择,内部包含了一个锁频环和一个锁相环,分别对内部参考时钟信号和外部时钟参考信号进行倍频。

2020-11-12 16:59:41 12

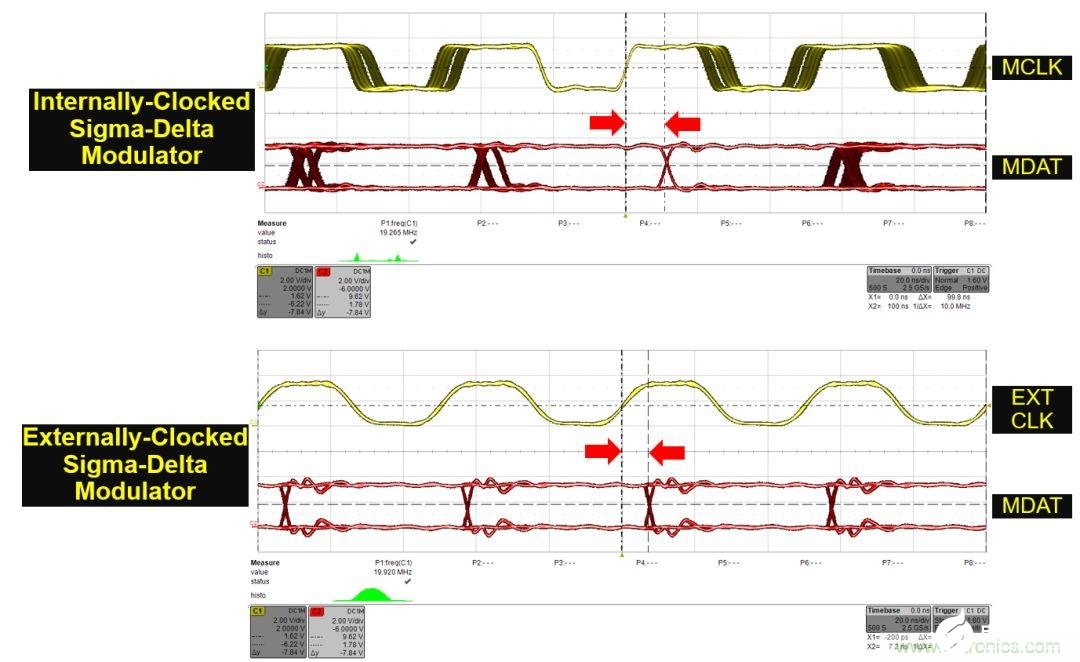

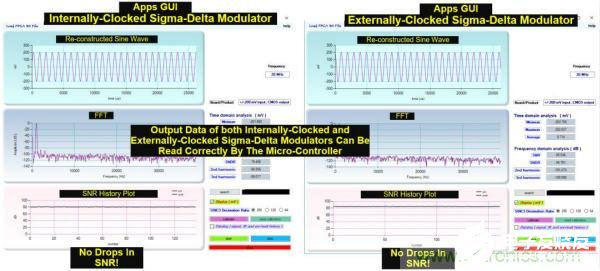

12 在本文中,将详细研究这两类隔离-调制器的输出数据信号完整性。并通过简单的电磁干扰(EMI)测试设置、对由这两类-调制器的高频时钟信号产生的EMI进行比较。 对输出数据信号完整性和时钟信号电磁干扰

2020-11-18 14:59:50 1450

1450 超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 时钟毛刺注入是现实环境中有效且常用的故障注入方法。时钟毛刺注入是通过在正常时钟周期中引入一段毛刺时钟,使得一个或多个触发器接受错误状忞而修改指令、破坏数据或状态,最终倢芯片内的秘密信息随着产生

2021-04-26 14:20:04 9

9 有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及

2021-05-10 16:51:39 4652

4652

PLL设计和时钟频率产生机理免费下载。

2021-06-07 14:36:43 22

22 stm32内部时钟有哪些时钟源 在STM32中,可以用内部时钟,也可以用外部时钟,在要求进度高的应用场合最好用外部晶体震荡器,内部时钟存在一定的精度误差。 内部时钟有2个时钟源可以选分别是HSI

2021-07-22 10:38:57 19057

19057 有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及

2021-09-23 16:39:54 3632

3632 门控时钟的设计初衷是实现FPGA的低功耗设计,本文从什么是门控时钟、门控时钟实现低功耗的原理、推荐的FPGA门控时钟实现这三个角度来分析门控时钟。 一、什么是门控时钟 门控时钟技术(gating

2021-09-23 16:44:47 15514

15514

时钟发生器用于产生时钟,并提供给CPU和外部硬件设备。UPD78F0527有如下三种系统时钟。(1)主系统时钟①通过连接一个振荡器到X1和X2,该振荡电路产生fx=1到20MHZ的时钟;②使用内部

2021-10-28 13:36:18 10

10 振荡器 产生内部时钟 SMCLK 子系统时钟时钟系统配置寄存器DCO控制寄存器 DCOCTL1、DCOx 频率选择 8种频率2、MODx DAC调制器设定 微调DCO 的输出频率基本时钟系统控制寄存器 BCSCTL1 BCSCTL2BCSCTL11、XT2OFF :XT2高速晶振开关

2021-11-19 21:06:06 18

18 信号-SOC-IN OSC-OUT悬空HSI:8MHz RC产生 做系统时钟或2分频后PLL输入相对HSE优点为启动时间短 置“1”,输出时钟释放系统复位1 HSIAL[7:0]位...

2021-12-02 13:36:06 0

0 信号-SOC-IN OSC-OUT悬空HSI:8MHz RC产生 做系统时钟或2分频后PLL输入相对HSE优点为启动时间短 置“1”,输出时钟释放系统复位1 HSIAL[7:0]位...

2021-12-22 18:59:46 0

0 如果用单独的时钟信号板,一般采用什么样的接口,来保证时钟信号的传输受到的影响小?

2022-09-16 08:58:49 3405

3405

本章的主要内容: 分析时钟驱动器、时钟信号的特殊布线 改进时钟信号分配的特殊电路

2022-09-20 14:55:40 0

0 的扇出型缓冲器,是一种将一路时钟源信号通过频率复制生成多路时钟信号的器件,通常时钟缓冲器还兼具有时钟分配,格式转换和电平转换的功能。 对于需要多路时钟信号的电子系统来说,时钟源加时钟缓冲器的方案可以有效降低系统成本,简化电路设计,为系统多个组件提供多路参

2022-10-18 18:36:54 30571

30571

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题。内部逻辑(组合逻辑)产生的时钟容易出现毛刺,影响设计的功能实现;组合逻辑固有的延时也容易导致时序问题。

2022-10-26 09:04:51 1877

1877 控制板级时钟分配期间出现的 EMI

2022-11-07 08:07:32 0

0 隔离放大器的输入级由一个驱动输入放大器-ΔΣ调制器的输入放大器组成。输入放大器的增益由内部精度电阻器进行固定和设置,ΔΣ调制器则使用内部参考电压和时钟发生器来将模拟输入信号转换为数字位流。

2023-02-10 15:12:49 1593

1593 RF DAC的无杂散动态范围受到严重的数字do主开关的限制,这会干扰模拟输出信号。介绍了一种扩频时钟发生器(SSCG)的设计、布局和仿真。SSCG调制用于切换DAC数字块的时钟频率,以减少DAC

2023-02-14 16:43:56 0

0 时钟电路是一种电路,它可以产生定期的时钟信号,用于控制电子设备的运行。

它的特点是可以产生定期的时钟信号,可以控制电子设备的运行,可以提高电子设备的精度和可靠性。时钟电路的应用非常广泛,它可

2023-02-20 18:16:38 9334

9334 系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 5281

5281 理想值附近的一个范围内,从而造成相邻的时钟边沿存在偏差。在时序分析时,时钟抖动是一个重要的因素。多种因素会导致时钟抖动,包括PLL回路噪声、电源纹波、热噪声以及信号之间的串扰等。

2023-06-09 09:40:50 3109

3109

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及

2023-08-23 16:10:01 1376

1376 芯片为什么要时钟信号 芯片是现代电子设备的核心组成部分,广泛应用于计算机、手机、电视等各个领域。芯片内部有着复杂的电子元件和电路结构,这些元件和电路结构需要进行同步操作,以实现正确的工作。因此,芯片

2023-09-01 15:38:11 3031

3031 一定的影响。因此,为了抑制时钟电路产生的电磁辐射,需要采取一些措施来降低其产生的电磁辐射水平。 一、由于时钟电路产生的电磁辐射的频率高,因此采用电源滤波器是比较常见的手段。电源滤波器可以减少电源电压中的高频

2023-09-12 17:06:49 1523

1523 件、计算机、数字电路和通讯协议等设备的信号。它的主要作用是进行时序控制,使数据传输和处理的时序保持一致。时钟信号一般由计时器产生,其具有一定的周期性、稳定性和精度。 时钟信号的主要信号参数包括周期、频率、精度和占空比等,

2023-09-15 16:28:12 4353

4353 ,CPU/Clock 作为芯片中的核心,是需要时钟信号的。 那么,什么是时钟信号? 时钟信号,是指芯片中的一个定时信号,用来指导芯片的工作节奏、同步各个部件的工作状态。简单来说,时钟信号是一种规律性的振荡信号,控制着芯片内各种部

2023-09-15 16:28:14 4268

4268 时钟信号怎么产生的 时钟信号是一种重要的信号,它在电子设备中广泛应用。时钟信号的产生与传输是现代电子设备中不可或缺的基础技术之一。时钟信号的精确性和准确性是现代电子设备能够实现高速计算等复杂操作

2023-09-15 16:28:22 3630

3630 是数据信号(SDA)。SCL信号是在IIC通信中非常重要的一个信号,它确定了数据的传输速率以及同步时序。 IIC时钟信号的产生需要硬件支持,一般通过外部晶振或者内部时钟源产生。在IIC总线使用过程中,时钟信号的频率很重要,必须要与所有设备的时钟频率保持一致。一般来说,为了保证

2023-09-19 17:16:02 3252

3252 方法来使不同步的时钟信号同步。下面我们就来详细讲解这些方法。 1. 时钟缓冲器同步法 时钟缓冲器同步法是指通过一个时钟缓冲器来同步两个不同步的时钟信号。其原理是将一个时钟信号通过一个缓冲器反转,产生一个相反的信号,

2023-10-18 15:23:48 2931

2931 可以说是计算机运行的重要组成部分之一。 时钟芯片的工作原理: 时钟芯片是通过一系列简单的电路来实现的,它内部包含一个晶体振荡器,用来产生一个稳定的基准信号。这个基准信号通过分频器分成不同频率的信号输出到不同的电

2023-10-25 15:02:33 8943

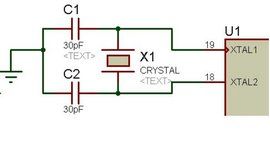

8943 。 单片机要实现数据处理和执行程序,需要一个时钟信号来引导CPU的运行。单片机可以使用片内时钟振荡方式和外部时钟方式两种方式来产生时钟信号,这两种方式具体有什么区别呢? 1. 片内时钟振荡方式 片内时钟振荡方式是指单片

2023-10-25 15:02:36 2187

2187 它可以被用来同步各种电子设备的操作。 产生时钟信号的器件主要有晶振、石英谐振器、电容器、电感、晶体管等。其中,晶振和石英谐振器是最常用的两种器件。 晶振是一种由压电晶体制成的振荡器。当施加电场时,晶体会振动产

2023-10-25 15:07:45 2236

2236 如何用时钟振荡器产生稳定的100hz或1hz的时钟信号? 时钟信号是电子系统中至关重要的组成部分,用于同步各种信号和操作。它需要稳定、准确、可靠地工作,以确保系统性能。时钟信号的产生可以通过许多

2023-10-25 15:07:55 2951

2951 什么是时钟电路?什么是脉冲?时钟电路是如何生成脉冲的? 时钟电路是一种电路,它产生的周期性的信号被用作计算机系统的基准。时钟电路产生的信号被称为时钟脉冲或时钟信号。在计算机系统中,时钟信号用于同步

2023-10-25 15:14:17 3577

3577 时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26:56 1541

1541 时钟电路是指用于产生稳定、精确的时间基准信号的电路。这种电路通常采用晶体振荡器或者其他稳定的振荡器作为时钟源,产生固定频率的信号。时钟信号被广泛应用于数字系统、通信系统、计算机系统等各种电子设备中,用于同步和控制各种操作和数据传输。

2023-11-17 09:50:08 4358

4358 如何有效解决LVDS时钟EMI问题

2023-11-23 09:04:46 1825

1825

什么是时钟信号?数字电路的时钟信号是怎么产生呢? 时钟信号,也称为时钟脉冲,是用于同步数字电路中所有操作的基本信号。它提供了一个参考频率,使得所有电路元件都能按照同样的节奏进行工作。时钟信号是一个

2024-01-25 15:40:52 15223

15223 芯片为什么要时钟信号 时钟芯片的作用是什么? 时钟信号在芯片中起着非常重要的作用。它是芯片的“心脏”,相当于人体的心脏,用于同步和控制芯片中的各个功能模块之间的操作。时钟信号可以提供一个稳定的时间

2024-01-29 18:11:31 8060

8060 SPICE是一种用于模拟和分析电子电路的计算机程序。在SPICE仿真中,产生时钟信号是许多电路设计和模拟任务中的关键步骤。

2024-02-06 14:22:01 2627

2627 电子发烧友网站提供《AMC1333M10具有10MHz内部时钟的±1V 输入、增强型隔离式Δ-Σ精密调制器数据表.pdf》资料免费下载

2024-08-16 11:18:09 0

0 时钟抖动(Clock Jitter)是时钟信号领域中的一个重要概念,它指的是时钟信号时间与理想事件时间的偏差。这种偏差不仅影响数字电路的时序性能,还可能对系统的稳定性和可靠性造成不利影响。以下是对时钟抖动工作原理的详细阐述,内容将围绕其定义、类型、产生原因、影响及应对措施等方面展开。

2024-08-19 17:58:11 5343

5343 电子发烧友网站提供《隔离式调制器与MCU之间的数字接口的时钟边沿延迟补偿.pdf》资料免费下载

2024-09-06 11:18:05 0

0 在数字电路设计中,时钟信号扮演着至关重要的角色。理想的时钟信号是一串无限连续的脉冲序列,除了电平要求外,其边沿应非常陡峭,有些系统还要求时钟具有50%的占空比。从电磁兼容性(EMC)的角度来看,理想

2024-09-13 14:18:06 1134

1134 电子发烧友网站提供《从晶体振荡器产生时钟信号.pdf》资料免费下载

2024-09-18 14:32:55 0

0 一前言随着信息技术和半导体技术的快速发展,电子产品的类型和功能模块日益多样化,对此要求的传输速率也日益提高。其中时钟频率的不断提升,同时也带来了更多的EMI时钟问题。时钟EMI问题的处理还受到了很多

2025-03-11 11:34:02 1108

1108

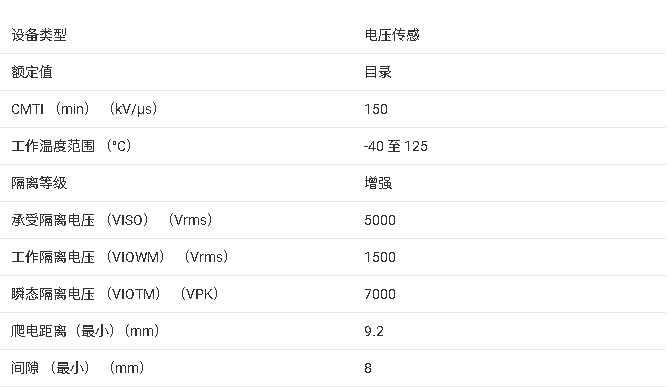

该AMC0386是一款精密的电流隔离三角积分 (ΔΣ) 调制器,具有高压、高阻抗输入和外部时钟。输入设计为直接连接到高压信号源。

隔离栅将系统中在不同共模电压电平下运行的部分分开。隔离栅具有很强的抗磁干扰能力,并经认证可提供高达 5kVRMS (60s) 的增强隔离。

2025-10-23 13:55:41 432

432

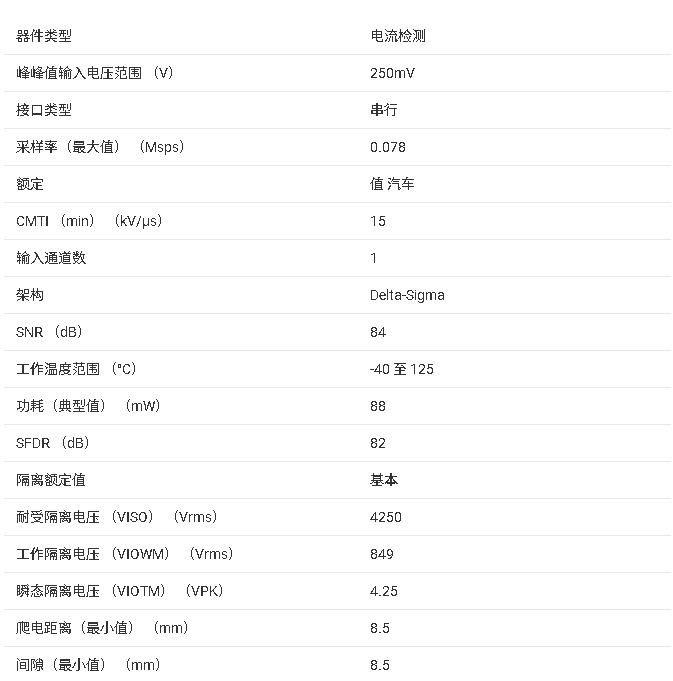

AMC1204-Q1 是一款 1 位数字输出、隔离式 Δ-Σ 调制器,时钟频率高达 20 MHz。调制器输出的数字隔离由二氧化硅(SiO ~2~ )屏障,具有很强的抗磁干扰能力。该屏障经认证可提供

2025-11-17 10:59:50 446

446

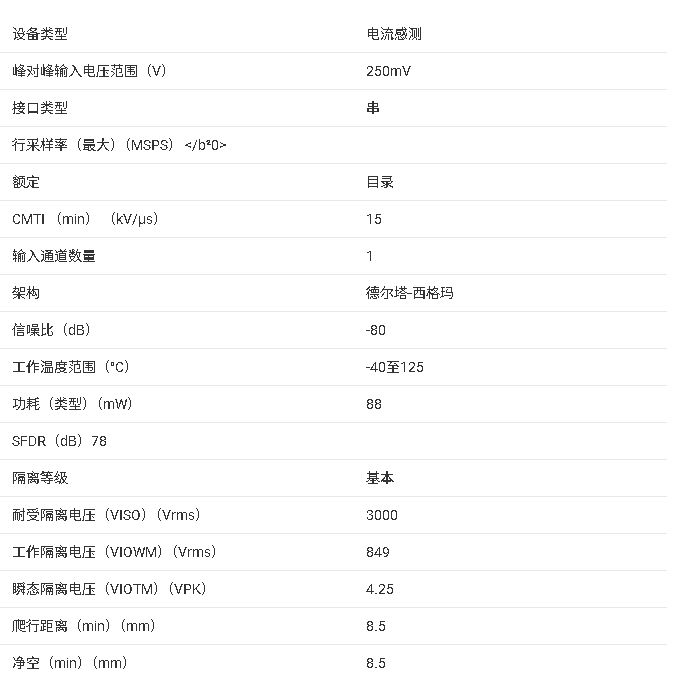

AMC1204和AMC1204B为1位数字输出,隔离δσ(ΔΣ)调制器,时钟频率最高可达20 MHz。调制器输出的数字隔离由二氧化硅(SiO)提供 ~2~ )屏障,具有高度的磁干扰能力。该屏障已经

2025-11-19 11:22:28 1176

1176

在现代高速数字系统中,时钟信号的完整性直接影响着系统的性能和稳定性。时钟缓冲器作为时钟树设计的核心组件,承担着信号分配、噪声隔离和时序优化的关键任务。随着5G通信、AI芯片和数据中心等领域的快速发展

2025-12-16 15:57:19 259

259

电子发烧友App

电子发烧友App

评论