本文转载自:韬略科技EMC微信公众号

一. 前言

随着电子技术的发展,我们的生活中充满着形形色色的电子产品,LCD显示屏便是其中之一,被广泛应用在手机,电脑,仪表等产品上,目前主流的LCD显示接口为RGB,LVDS,mipi和HDMI。今天跟大家分享的案例为某LCD仪表的LVDS时钟EMI辐射超标问题处理,一起来看看吧。

二. 案例背景

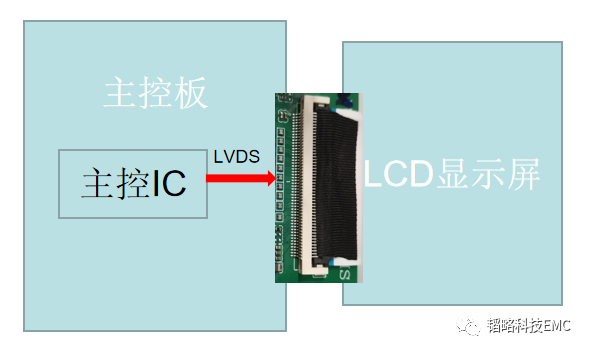

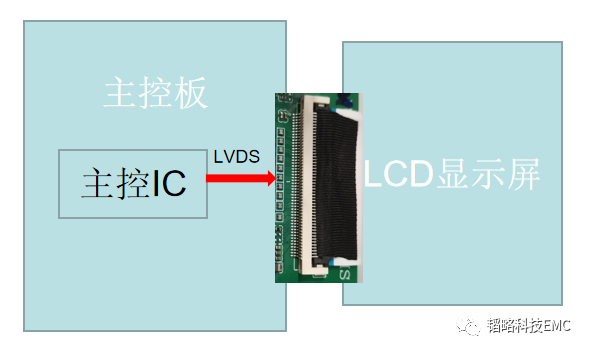

本次项目为某车载仪表,客户反馈存在时钟辐射超标问题。电路的架构比较简单,主要由两部分组成,主控电路板和显示屏,主控芯片输出LVDS信号,通过FPC排线驱动LCD显示屏,简单的电路架构如下图:

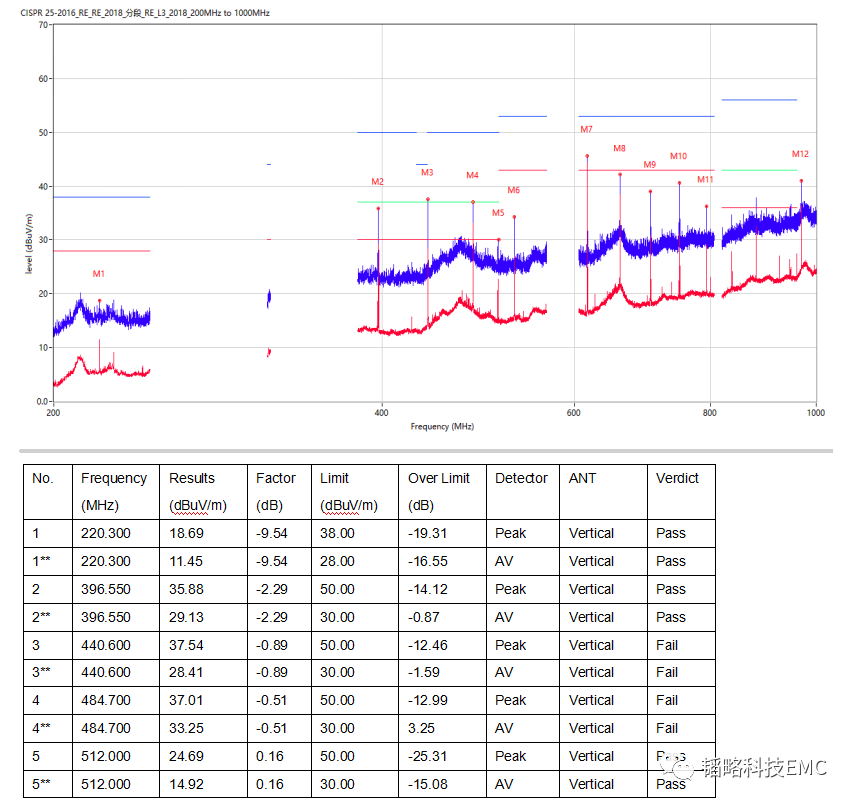

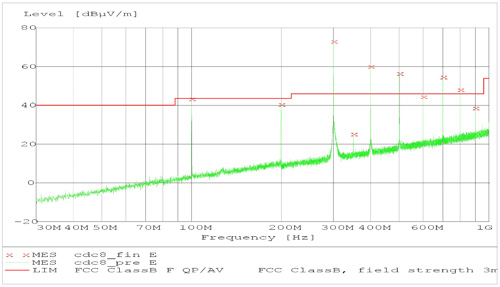

整改前200MHz-1G频段测试数据如下:

由数据可以看出,主板上存在44MHz的时钟倍频,主芯片IC的晶振为24MHz,通过频谱仪可以找到时钟辐射源头为LVDS信号。

三. 整改过程与措施

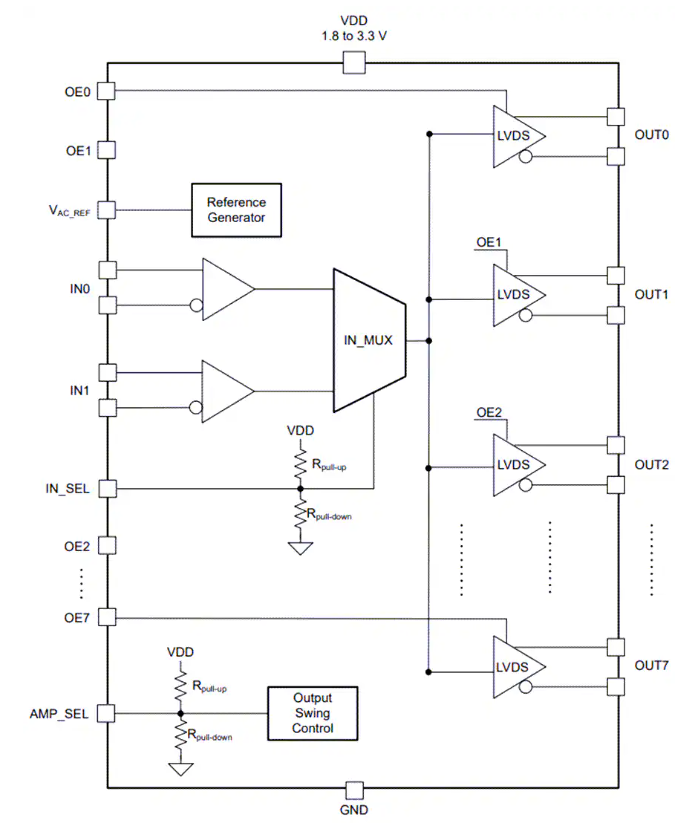

整改措施1--时钟展频

对于高频时钟辐射问题,考虑时钟展频处理是最有效便捷的方式,可以实现直接在时钟源头处降低噪声强度。目前常见的展频方式可分为软件展频和硬件展频,软件展频需要看芯片是否支持,硬件展频是通过对芯片主时钟进行展频处理后传输给芯片,之后芯片输出的时钟信号都为展频后时钟。

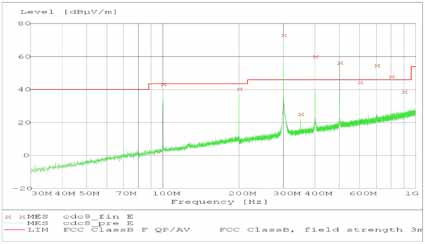

对主IC进行展频处理,时钟频率24MHz,展频宽度±0.25%,效果如下图:

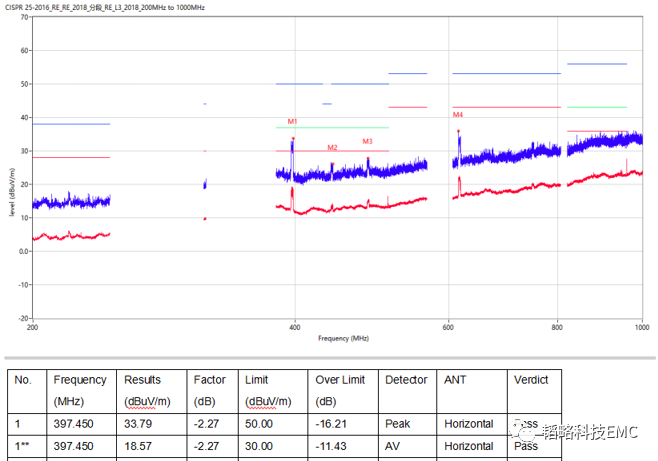

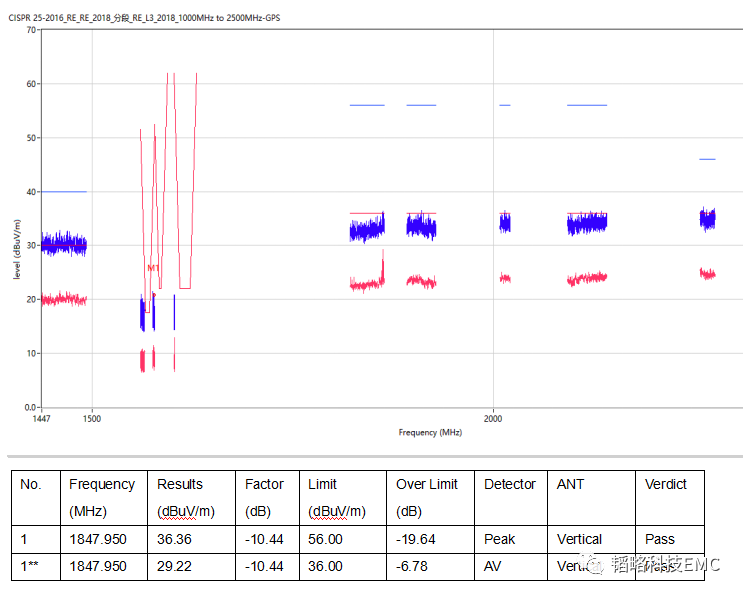

通过数据对比,可以发现,时钟单支展频后EMI有明显改善。继续测试其他频段,发现高频1G-2.5GHz频段1848MHz频点余量不够,数据如下:

排查:由于显示屏排线为普通排线,作为主要的数据传输路径,怀疑排线成为主要辐射路径,拔掉后1848MHz频点下降明显,数据如下:

整改措施2--数据线屏蔽处理

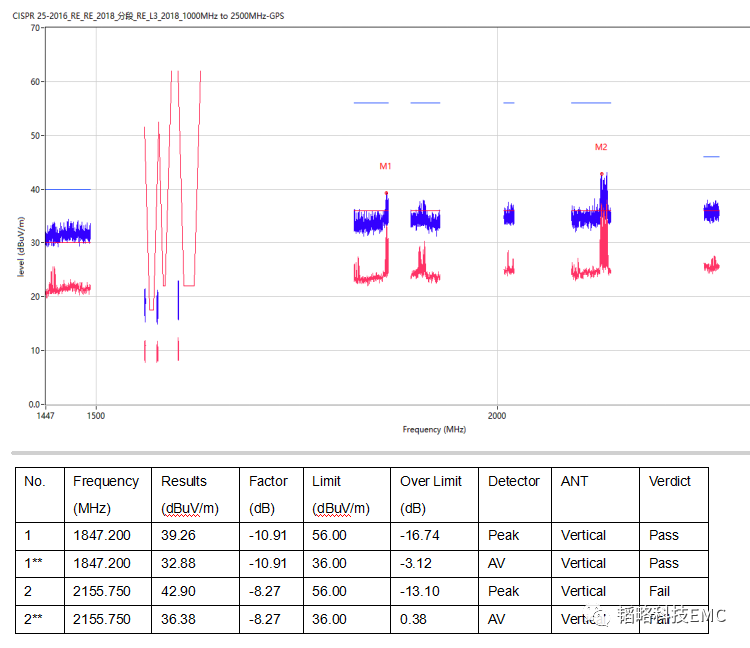

(1)对排线做屏蔽处理,用导电布包排线,不做接地处理,数据如下:

对比数据,发现1848MHz频点下降了3dB,但却造成了2156MHz频点超标,继续完善屏蔽措施,一般屏蔽都需要做两端接地处理。

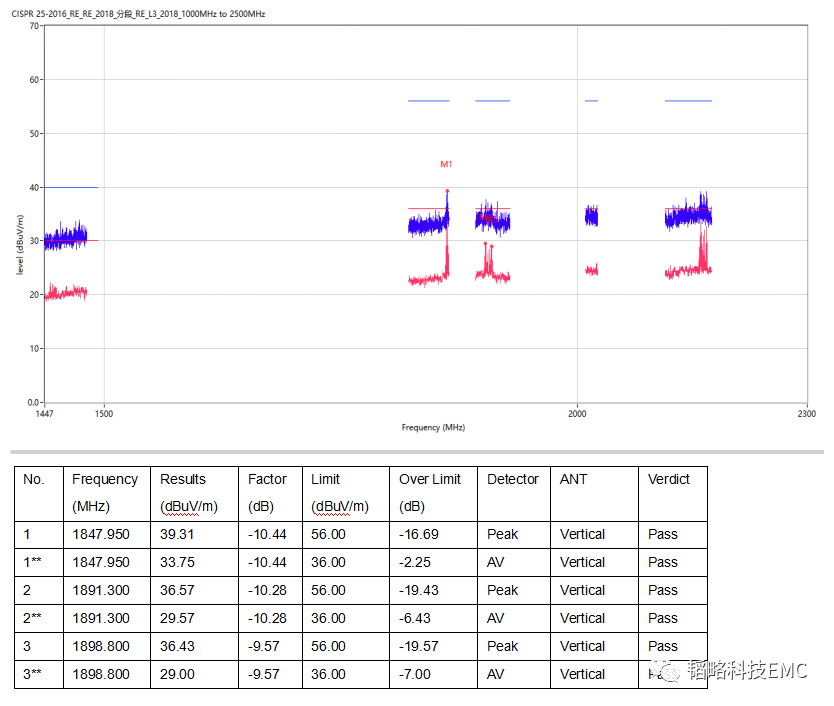

(2)排线屏蔽+接地处理,数据如下:

通过屏蔽接地处理之后,数据多了一些余量,考虑到屏蔽排线成本,继续尝试其他方案。

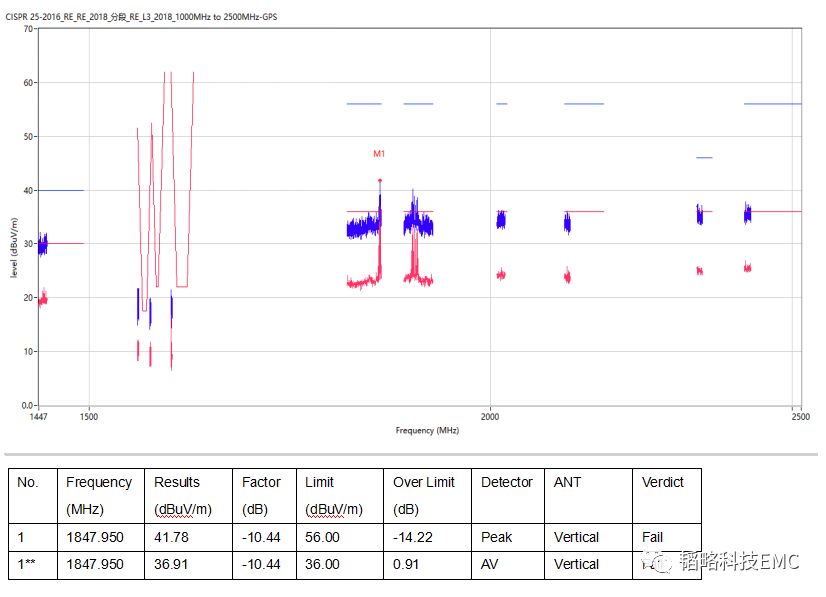

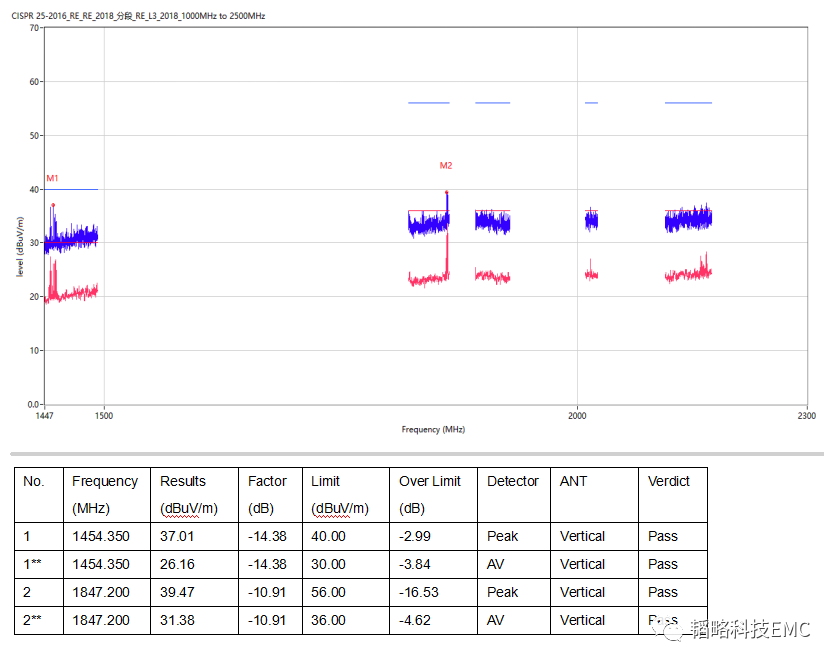

整改措施3--不加屏蔽,在LVDS 信号线对之间加5pF小电容滤波,数据如下:

通过在LVDS信号线对之间加小电容做差模滤波,1848MHz频点已经有4个dB余量。

四. 总结

为了应对越来越严苛的EMC标准,我们可谓是绞尽脑汁,既要考虑成本,又要兼顾方案的有效性与可实施性。本文针对LVDS信号驱动的LCD显示屏的EMI问题验证了两个有效的方案,其一是展频+排线屏蔽,另一种是展频+小电容滤波,希望对各位有一点帮助,对于LVDS时钟辐射问题是否有其他有效的方案呢?欢迎大牛留言讨论。

审核编辑 黄宇

-

emi

+关注

关注

54文章

3864浏览量

134083 -

时钟

+关注

关注

11文章

1953浏览量

134532 -

lvds

+关注

关注

2文章

1216浏览量

69115

发布评论请先 登录

LVDS用法:LVDS RX 时钟选择 LVDS的PLL的复位信号的处理

如何调整LVDS时钟频率和时序?

控制板级时钟分配期间出现的EMI

控制板级时钟分配期间出现的 EMI

通过使用展频IC解决EMI时钟问题

有效控制EMI设计的规则盘点

怎样解决LVDS时钟的EMI问题呢?

LVDS中的时钟脉冲信号是干什么的?

LMK时钟family LVDS输出交流耦合设计注意事项

HACD1204QN型低抖动LVDS时钟缓冲器

HACD1208QN型低抖动LVDS时钟缓冲器

HACD1216QN型低抖动LVDS时钟缓冲器

HDMI时钟EMI问题的高效解决方案

LMK1D1208P LVDS时钟缓冲器技术解析

如何有效解决LVDS时钟EMI问题

如何有效解决LVDS时钟EMI问题

评论