如果用单独的时钟信号板,一般采用什么样的接口,来保证时钟信号的传输受到的影响小?

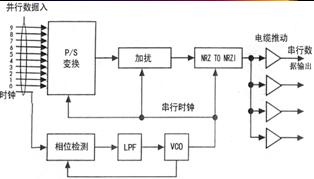

时钟信号越短,传输线效应越小。采用单独的时钟信号板,会增加信号布线长度。而且单板的接地供电也是问题。如果要长距离传输,建议采用差分信号。LVDS信号可以满足驱动能力要求,不过如果时钟不是太快,没有必要。

27M,SDRAM时钟线(80M-90M),这些时钟线二三次谐波刚好在 VHF 波段,从接收端高频窜入后干扰很大。除了缩短线长以外,还有那些好办法?

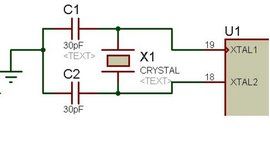

如果是三次谐波大、二次谐波小,可能因为信号占空比为50%。因为这种情况下,信号没有偶次谐波,这时需要修改一下信号占空比。此外,对于如果是单向的时钟信号,一般采用源端串联匹配。这样可以抑制二次反射,但不会影响时钟沿速率。源端匹配值,可以采用下图公式得到。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SDRAM

+关注

关注

7文章

449浏览量

57287 -

接口

+关注

关注

33文章

9446浏览量

156145 -

时钟信号

+关注

关注

4文章

495浏览量

29696

发布评论请先 登录

相关推荐

热点推荐

CSI2接口时钟信号的疑问?

DM8127 中ISS中的CSI接口模块,是串口传输数据

数据包中有Sof Eof等帧头信息,CSI接口能够直接传输给VP

VP是需要HS、VS、PCLK、这几路

发表于 06-22 00:49

APB接口协议的读写传输及工作流程简析

UART、I2C等。一般SoC都是通过它们的寄存器进行访问。APB每次传输至少需要两个周期,所有信号的转换仅在时钟的上升沿发生以便能够轻松地将APB外设集成到其他设计中。APB还包括用于扩展APB

发表于 04-07 10:18

基于双音频信号传输的PC通信接口电路

基于双音频信号传输的PC通信接口电路摘要 在PC 远程控制与检测系统中,电话线是最常用的一种传输介质。文章介绍了PC 通过电话线利用双音频信号

发表于 06-09 15:10

•44次下载

时钟信号和脉冲信号有区别吗?

件、计算机、数字电路和通讯协议等设备的信号。它的主要作用是进行时序控制,使数据传输和处理的时序保持一致。时钟信号一般由计时器产生,其具有一定的周期性、稳定性和精度。

LVDS中的时钟脉冲信号是干什么的?

LVDS中的时钟脉冲信号是干什么的? LVDS(Low Voltage Differential Signaling)中的时钟脉冲信号(Clock)是用于同步数据

芯片为什么要时钟信号 时钟芯片的作用是什么?

基准,使得整个芯片能够以协调一致的方式进行工作。 时钟信号的重要性主要表现在以下几个方面: 1. 同步功能:芯片内部的各个模块需要以同步的方式进行操作,以确保数据的准确传输和处理。时钟

SDI接口的基本概念及传输信号类型

SDI(Serial Digital Interface,串行数字接口)是一种用于传输数字视频信号的接口标准。它广泛应用于广播、电影制作、后期制作等领域。 一、SDI

时钟信号传输与接口

时钟信号传输与接口

评论