FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。6 LX9 FPGA就可以实现开源的“J Core”处理器?

如果你了解Hitachi SuperH系列32位精简指令集(RISC)微处理器,那么对于“J Core”就不会那么陌生了。“J Core”是SuperH处理器架构的开源版本,是由开源处理器协会(OPF)实现的,采用VHDL语言,执...

2017-02-08 739

具有单电源管理IC的Powering Xilinx Zynq 7000 系列 SoC/FPGA 评估模块

这项基于 TPS65218 的参考设计是一种紧凑型集成电源解决方案,适用于 Xilinx® Zynq® 7010 SoC/FPGA(属于 Zynq® 7000 产品系列)。此设计将 TPS65218 展示为一体式 PMIC,用于提供为 Zynq® 7010 SoC/FPGA 供电所...

2017-02-08 583

这个套件让Power8服务器硬件加速更简单

在CAPI规范问世之前,使用FPGA来做硬件加速的过程很费劲。它是把FPGA做到一块PCIe板卡里,FPGA通过CPU的PCIe控制器访问主机内存空间。因为所有的CPU线程看到的都是单一虚拟地址空间,CPU不能直接...

2017-02-08 485

7010 SoC 优化的汽车级ADAS电源设计

TIDA-00389 设计是一种经过优化的电源解决方案,适用于 Xilinx® Zynq® 7010 FPGA/SoC(属于 Zynq® 7000 产品系列)。它面向 ADAS 应用,在这些应用中客户选择使用 FPGA 代替多核 DSP 或 MPU。此设计使用单一...

2017-02-08 536

面向 Xilinx Zynq FPGA 应用的多输出、多路降压 20W 电源参考设计

PMP9335 专为使用 TPS84A20 和 TPS84320 的 Xilinx Zynq FPGA 应用而设计。此设计使用外部计时器将开关频率同步到 300 kHz。它还采用受控的加电和断电序列。 特性 专为 Xilinx Zynq FPGA 应用而设计 采用 TPS8...

2017-02-08 433

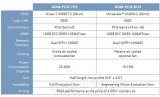

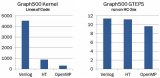

惊呆!Xilinx FPGA加速让DRC大数据分析软件“GraphFind”性能提升9倍

DRC(DRC Computer Corporation)是一家专门定制应用加速解决方案的公司,帮客户降低成本的同时提升系统性能。自主研发了基于FPGA(可编程门阵列)可配置协处理器,运行复杂的数据分析应用要比...

2017-02-08 722

Xilinx扩展SmartConnect技术 为16nm UltraScale+器件实现20%

Vivado Design Suite 2016.1现提供SmartConnect 技术支持,能解决高性能数百万系统逻辑单元设计中的系统互联瓶颈问题 赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布推出Vivado® Design Suite2016.1 的 HLx版本。...

2017-02-08 712

一个用于FPGA的微型的RISC(精简指令集)处理器

昨天讨论了使用FPGA的一些引脚调试I2C串行协议,并介绍了在基于FPGA的设计中使用赛灵思PicoBlaze微控制器。(查看仅使用两个I/O引脚,I2C通信协议和一个数字示波器调试你的FPGA设计)PicoBlaze微控...

2017-02-08 569

如何在芯片的PL上构建软核处理器?

到目前为止,我们已经在之前的文章中聊过Zynq SOC内部的 PS和PL,以及在Zynq SoC PS部分的ARM Cortex-A9处理器上运行的操作系统。但是有一个领域我们还没有去探索过,那就是在芯片的PL上构建软核处...

2017-02-08 1520

UltraScale架构DDR4 SDRAM接口的秘密

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 Adrian Cosoroaba和Terry Magee在本月MemCon上给出了关于DDR4 SDRAM接口的详细展示,该演示应用于赛灵思UltraScale All Programmable FPGA上。接口设计将DDR SDR...

2017-02-08 1213

Adam Taylor玩转MicroZed系列55:在Zynq SoC上运行Linux操作系统

如果在我们的虚拟机上已经安装好了SDK,我们就得使用Linux操作系统来建立我们自己的应用程序。这通常需要对 Zynq SoC的硬件重新进行定义。 首先,我们要做的就是确保将VIVADO设计套件以及SD...

2017-02-08 698

Adam Taylor玩转MicroZed系列54:在Zynq SoC上玩转PetaLinux

正如我上周所讲,Petalinux是Xilinx针对Zynq SoC提供的Linux官方版本。为了攫取该版本最大资源,我们需要创建自己的版本。这就需要我们在Linux环境下进行开发。现在,并不是所有人都在Linux系统环...

2017-02-08 404

基于ZEDBoard构建图像处理通路(Block Ram版本)

注:本博文的工程文件位于: 对于集FPGA和ARM于一体的Zynq系列平台来说,图像处理是Zynq平台主要的应用方向之一。图像采集部分是图像处理系统的重要组成部分,它通过图像传感器将外部的图...

2017-02-08 764

Clock Skew , Clock uncertainly 和 Period

Intel 4790K的主频是4.0GHz,高通801的单核频率可达2.5GHz,A8处理器在1.2GHz,MSP430可以工作在几十MHz……这里的频率的意思都是类似的,这些处理器的频率都是厂商给定的。但是对于FPGA的工作频率而...

2017-02-08 1227

【FPGA中国好教程】手把手教你在Zynq SoC上面实现千兆以太网I/O

赛灵思最新的技术提示会为您提供在所有系列的Zynq SoCs上实现嵌入式千兆以太网接口一些基础知识。该技术提示也适用于在Zynq SoC可编程逻辑中实例化额外的Gbps以太网接口(如果您需要,可以实...

2017-02-08 1913

视频编码方案之间的比较(HEVC,H.264,MPEG2等)

Jens-Rainer Ohm等人在文献《Comparison of the Coding Efficiency of Video Coding Standards—Including High Efficiency Video Coding (HEVC)》中对比了几种视频编码方案。编码方案包括:HEVC,H.264,MPEG4,H.263,MPEG2。在此我...

2017-02-08 1503

机器视觉之ICP算法和RANSAC算法

临时研究了下机器视觉两个基本算法的算法原理 ,可能有理解错误的地方,希望发现了告诉我一下 主要是了解思想,就不写具体的计算公式之类的了 (一) ICP算法(Iterative Closest Point迭代最近...

2017-02-08 1330

7000 Development Board Work Booting Linux on the ZYBO

本文主要是详细讲解zybo硬件系统搭建,u-boot,linux-kernel移植,linaro文件系统移植。过程中需要生成的文件有system.bit,fsbl.elf,u-boot.elf,devicetree.dtb,uImage(zImage和uImage区别请看),linaro文件系...

2017-02-08 1088

OFFSET约束的写法(OFFSET IN和OFFSET OUT)

1. OFFSET约束的写法 Offset 约束定义了外部时钟pad和与之相关的输入、输出pad之间的相对关系。这是一个基础的时序约束。Offset定义的是外部之间的关系,不能用在内部信号上。 OFFSET约束写起来还...

2017-02-08 2888

Xilinx Vivado的使用详细介绍(3):使用IP核

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直...

2017-02-08 3190

Xilinx Vivado的使用详细介绍(2):综合、实现、管脚分配、时钟设置、烧写

前面一篇介绍了从新建工程一直到编写代码进行行为仿真,这篇继续进行介绍。 修改器件型号 新建工程时选择过器件型号,如果新建好工程后需要修改型号,可以选择菜单Tools - Project Settings。...

2017-02-08 6021

Xilinx Vivado的使用详细介绍(1):创建工程、编写代码、行为仿真、Testbench

新建工程 打开Vivado软件,直接在欢迎界面点击Create New Project,或在开始菜单中选择File - New Project即可新建工程。 点击Next 输入工程名称和路径。 选择RTL Project,勾选Do not specify......(这样可以跳...

2017-02-08 2715

《基于FPGA的数字信号处理》(第2版)试读章节

采用高级语言如C、C++、Matlab对系统建模是ESL设计理念的特征之一,将其称之为高层次综合。高层次综合跨越硬件领域和软件领域。对硬件工程师而言,它可以使硬件工程师工作在有别于传统R...

2017-02-08 494

数据中心用FPGA加速卡来了!基于Xilinx Kintex系列UltraScale架构FPGA

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 近期在New Orleans举办SC14会议(超级计算机会议),在此次会议上Xilinx发布的关于SDAccel开发环境的公告中提到了三个关键的组件,其中之一就是...

2017-02-08 964

“我们能相信HLS吗?”这篇博文在LinkedIn社交网站的多个群组中引发了有深刻见

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 我上篇博文我们能相信HLS吗?Brian Bailey想知道,也许你也想知道,在LinkedIn网站各种FPGA相关的群组中引发了非比寻常的关注和讨论。 这是Lin...

2017-02-08 481

高级语言(HLL)标准扩展大大简化基于FPGA加速器的应用程序的开发

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 在New Orleans举办的超级计算机大会(SC14)上,Convey Computer公司介绍了很多关于HLL(高级语言)的标准扩展和利用FPGA实现加速的应用等内容。Convey公...

2017-02-08 682

直击关于Xilinx UltraScale架构、Virtex和Kintex UltraScale架构FPGA 和最新的Vivado开发工具

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 上周出版的最新一期的Xcell Journal杂志中刊载了由Nick Mehta主笔的一篇文章(Productivity Skyrockets with Xilinxs UltraScale Architecture)(Xilinx UltraScale 架构...

2017-02-08 1136

Adam Taylor玩转MicroZed系列60:Zynq与PicoBlaze第五章:控制CCD(一种图像传感器)

作者:Adam Taylor 在上一篇博客中我们已经知道了如何动态更新PicoBlaze的运行程序,现在我们要学习一个完成的设计应用。一个非常相关的应用就是驱动CCD(电荷耦合元件)图像传感器,因为在这...

2017-02-08 325

嵌入式视觉系统的构建模块

在本文中我们将会介绍嵌入式视觉系统的高级元素;如何简便快捷地使用软件 API 和 IP 库构建嵌入式视觉系统,如何把算法开发的增值部分添加到图像处理链中。...

2017-02-08 2120

Modelsim编译Xilinx器件库的另一种方法

以前在用modelsim对Xilinx进行器件库编译时,我用的比较多的是直接在ISE中编译器件库,感觉很方便简单,就是编译时间有点长。自从前段时间,在自己电脑装MathType,360杀毒软件将它视为木马。...

2017-02-08 516

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |