FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。基于FPGA的实时视频处理平台方案讨论及设计

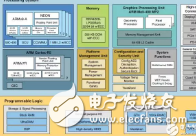

为了能够实时地采集、处理、显示视频,设计并实现了一种基于双PowerPC硬核架构的实时视频处理平台;用硬件实现视频的预处理算法,并以用户IP核的形式添加到硬件系统中,上层...

2017-11-22 3999

基于FPGA 的雷达信号采集系统设计

近年来,雷达在军用和民用领域都获得了巨大的发展。雷达信号处理系统是雷达的关键模块,对雷达定位精度起着决定性作用。FPGA 以其众多的优点,在雷达信号处理系统中被广泛使用。本文探...

2017-11-22 5115

基于Xilinx FPGA SOPC的TFT-LCD 控制器设计与实现

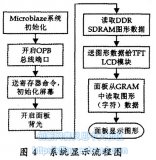

根据TFT-LCD的工作原理,采用Xilinx公司的Microblaze微处理器软核,提出了一种基于嵌入式FPGA SOPC平台的TFT-LCD控制器方案.并验证了该方案的可行性。该控制器为进一步在嵌入式FPGA 片上系统进行图...

2017-11-22 2911

Xilinx DDR2 IP 核控制器设计方案介绍与实现

提出一种便于用户操作并能快速运用到产品的DDR2控制器IP核的FPGA实现,使用户不需要了解DDR2的原理和操作方式的情况下,依然可以通过IP核控制DDR2。简单介绍了DDR2的特点和操作原理,并对DD...

2017-11-22 5862

不同场景的FPGA外围电路的上电时序分析与设计

提出了由于FPGA容量的攀升和配置时间的加长,采用常规设计会导致系统功能失效的观点。通过详细描述Xilinx FPGA各种配置方式及其在电路设计中的优缺点,深入分析了FPGA上电时的配置步骤和工...

2017-11-22 8400

FPGA查找表实现原理分析

查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。 目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM。 当用户通过原理图或HDL语言描述了一个逻辑电路以后,...

2017-11-22 14632

Xilinx全局时钟的使用和DCM模块的使用

在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配树结构 针对...

2017-11-22 12505

面向可重构系统的一种功耗相关硬件任务调度算法设计

可重构系统是指以软件改变硬件结构以实现具体应用的计算平台,一般由非柔性但可编程的处理器和柔性的以程序控制重构的数字逻辑器件构成。目前国内外的可重构系统研究中,采用的可重构...

2017-11-22 1106

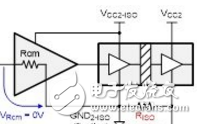

RS-485隔离式数字接口

本文重点讨论符合RS-485标准(目前仍是业内最主要的数据传输标准)的隔离式数字接口,并将提出RS-485共模电压范围(CMVR)的定义,解释应怎样隔离收发器的讯号和供电通路与本地控制器电路,才能使...

2017-11-21 3237

构建可启动的系统镜像的过程

当利用petalinux工程构建并测试完一个Linux系统后,下一步就是产生可以部署在现场的启动镜像。该过程可以通过petalinux-pakage命令简单地完成。产生Zynq启动镜像,本小节只针对Zynq系列器件。如果是...

2017-11-21 1369

xilinx vivado zynq pldma设计及应用block design操作说明

这个设计是根据avnet的PL dma带宽测试程序修改过来的,只使用了其中的HP0一个PLDMA。分为两个部分进行设计,第一部分是关于vivado中的block design部分,就是通过ip进行设计。第二部分是PLDMA的源码部...

2017-11-21 9860

Vivado 学习之编写IP核并通过AXI协议与ARM通信

最近发现了一块好玩的板子,PYNQ 这块板子最大的特点就是可以将所写的IP核封装成Python库的形式,然后通过在板载的xlinux系统下用户可以选择通过Jupiter编辑器实时的编写Python脚本,然后Pytho...

2017-11-21 11278

FPGA中组合逻辑和时序逻辑的区别

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出...

2017-11-20 9206

采用软件定义无线电开发RFID测试平台

"FPGA的优势加上实时信号处理功能,有助于提高测试速度。 同时,FPGA编程的灵活性可以快速响应新协议的测试需求。"- Chun Zhang, Institute of Microelectronics, Tsinghua University 挑战: 错综复杂的UHF技术...

2017-11-18 1256

针对高速数据转换器的最新高速JESD204B标准带来了验证挑战

JESD204B是最新的12.5 Gb/s高速、高分辨率数据转换器串行接口标准。转换器制造商的相关产品已进入市场,并且支持JESD204B标准的产品预计会在不久的将来大量面世。JESD204B接口的主要价值在于,它...

2017-11-18 3570

基于FPGA的DDR3多端口读写存储管理的设计与实现

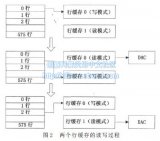

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR3读写操作...

2017-11-18 7907

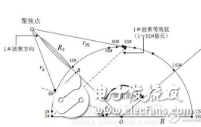

成像声纳中多波束形成的FPGA工程实现

本文提出了一种计算方法简单、计算量小、所需存储量小的近场聚焦多波束形成的高速FPGA实现方法,用于成像声纳中高精度、高覆盖、高波束数的多波束形成。本方法基于180阵元均匀半圆阵,...

2017-11-18 2823

使用NI LabVIEW FPGA创建高速控制系统以用于MEMS微快门测试

詹姆斯韦伯太空望远镜(JWST)是NASA的下一代大型望远镜。它比前辈哈勃太空望远镜更具雄心,NASA将把它布置在离地球约100公里远的稳定拉格朗日点上。该望远镜将是NASA理解宇宙和研究大爆炸理论...

2017-11-18 1310

无线应用平台选择的几个关键考量因素

随着无线数据传输量呈爆炸性成长,数字讯号处理技术和无线电设备在提升效能方面都面临巨大的压力。目前全球的重点都聚焦在4G LTE,而且在世界各地均有大规模部署,而业界也已展开5G网络...

2017-11-18 1147

用ZYNQ MPSoC玩DOOM!

通过这篇有趣的教程,熟悉运行在赛灵思 Zynq UltraScale+ MPSoC 上的 Xen 管理程序。 赛灵思和 DornerWorks 的系统软件团队在赛灵思的 Zynq® Ultrascale+™ MPSoC 上启动 Xen Project 管理程序时,我们发现可通...

2017-11-18 3054

机器学习综述——机器学习理论基础与发展脉络

计算机科学,特别是人工智能的研究者一般公认Simon对学习的论述:“如果一个系统能够通过执行某个过程改进它的性能,这就是学习。”这是一个相当广泛的说明, 其要点是“系统”, 它涵盖了...

2017-11-18 8257

如何用PMIC快速、轻松且划算的为FPGA供电

如果你是一名研究现场可编程门阵列 (FPGA) 的工程师,你就应该知道这些器件的高效运行需要优化的电源序列。使用离散组件来满足这些特定的电源需求通常需要一个额外的离散排序器或微控制...

2017-11-18 2154

使用NI LabVIEW FPGA与智能DAQ的自动高电压电击测试

前款手动系统即透过平行通讯埠同步执行 12 个模块,仅可测试 1 种 HV 电击器,且测试 12 组仪器需耗时 135 分钟。新的自动化系统可透过 FPGA 数位 I/O 通讯功能,非同步执行 12 个模块,并于 48...

2017-11-18 1721

Vivado使用误区与进阶——在Vivado中实现ECO功能

关于Tcl在Vivado中的应用文章从Tcl的基本语法和在Vivado中的应用展开,介绍了如何扩展甚至是定制FPGA设计实现流程后,引出了一个更细节的应用场景:如何利用Tcl在已完成布局布线的设计上对网...

2017-11-18 5818

采用LabVIEW FPGA改善视网膜疾病的治疗

"采用LabVIEW FPGA进行编程使得我们能够调整每一个脉冲的定时和功率,满足我们对于高速度和高精度的双重要求。"—— Michael Wiltberger, OptiMedica Corporation 挑战: 开发一个高精度的能够自动根据已经...

2017-11-18 926

利用LabVIEW FPGA模块构建灵活的发动机仿真器

"利用LabVIEW FPGA模块在NI PXI-7831R可重配置I/O板卡的FPGA上编程,不但使我们的系统性能超过了规格要求,还节省了90%的硬件搭建成本。"—— Matthew Viele, National Instruments 挑战: 开发一款发动机仿真器...

2017-11-18 2002

FPGA Fanout-Fanin(扇入扇出)资料解析

在谈到多扇出问题之前,先了解几个相关的信息,也可以当成是名词解释。 扇入、扇出系数 扇入系数是指门电路允许的输入端数目。一般门电路的扇入系数为1—5,最多不超过8。扇出系数是指...

2017-11-18 17862

利用中间件可将Zynq SoC转变为动态再分配处理平台

过去三十多年来,FPGA 技术已从最初带有少量寄存器的可编程逻辑阵列演变为如今我们所看到的高级集成式系统器件。大约在十多年前,各大厂商首次开始在他们的FPGA器件中采用8位、16位和32位...

2017-11-18 1089

让硬件设计轻松自如

工程设计项目中最令人振奋的时刻之一就是第一次将硬件移到实验室准备开始集成测试的时候。开发过程中的这个阶段通常需要很长时间,也会对所有的项目工程师造成很大的压力。不过,现有...

2017-11-18 721

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |