FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。FPGA上电后IO的默认状态

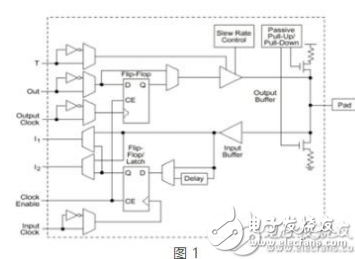

在进行FPGA硬件设计时,引脚分配是非常重要的一个环节,特别是在硬件电路上需要与其他芯片通行的引脚。Xilinx FPGA从上电之后到正常工作整个过程中各个阶段引脚的状态,会对硬件设计、引脚...

2017-11-28 16940

一站式FPGA基础设施服务详情-FPGA加速云服务器亮相华为欧洲生态大会

在欧洲举行的2017 华为欧洲生态大会(HUAWEI ECO-CONNECT EUROPE,HCE)上,华为云FPGA加速云服务器(FACS)惊艳亮相,获得广泛关注,完整的基础设施服务及其两款FP1实例,成为本次大会的一大亮点。...

2017-11-28 1085

嵌入式工程师需知道的实用算法

伴随着人工智能、物联网时代的到来,数据应用变得频繁起来,数据安全应该如何保护?软件加密算法都有哪些,这些算法在哪些方面得到了应用?慢慢读下去,你会发现围绕在我们身边的“小...

2017-11-27 2196

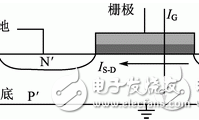

FPGA的功耗概念分析与低功耗设计研究

芯片对功耗的苛刻要求源于产品对功耗的要求。集成电路的迅速发展以及人们对消费类电子产品——特别是便携式(移动)电子产品—的需求日新月异,使得设计者对电池供电的系统已不能只考...

2017-11-26 6272

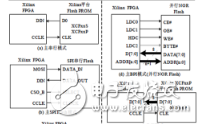

基于FPGA和高速A/D转换芯片ADC08D1500的相关系统设计

为同时完成4 个Stokes 矢量参数的相关测量,反演海面风场,提出了新型数字相关器的设计方法。结合高速数字相关器在数字极化辐射计中的应用,介绍了高速数据采样和相关处理系统。通过两片...

2017-11-26 6443

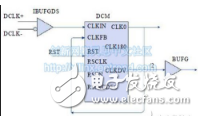

Xilinx FPGA电路配置

FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟...

2017-11-26 9020

Virtex-5推动超宽带通信和测距的发展

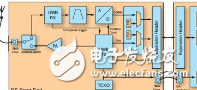

自2002年美国联邦通信委员会授权可以无执照使用超宽带(UWB)无线电技术以来,大多数采用该技术的商业应用(如无线USB),都是基于用于高数据速率传输的频域调制技术(如OFDM)。UWB这种成熟的技术...

2017-11-25 1457

可重构技术分析及动态可重构系统设计

基于SRAM的FPGA的问世标志着现代可重构技术的开端,并极大地推动了其发展。可编程FPGA可以根据不同算法设计合理的硬件结构,以达到提高执行效率的目的。动态可重构FPGA可以在程序运行中动...

2017-11-25 14541

赛灵思PicoBlaze微控制器软核介绍

PicoBlaze是由Xilinx公司的Ken Chapman设计并维护的一款8bit的微控制器软核,可以嵌入到Cool Runner II、 Virtex-E,Virtex-II(Pro) 和 Spartan3(E)的CPLD以及FPGA中。...

2017-11-25 2034

基于FPGA的出租车计价器的设计

FPGA(Field Programmable Gate Array,现场可编程门阵列)是一种高密度可编程逻辑器件,它支持系统可编程,通过写入不同的配置数据就可以实现不同的逻辑功能。使用FPGA来设计电子系统,具有设计周期...

2017-11-25 13678

赛灵思的目标设计平台的介绍

2009年2月Virtex®-6和Spartan®-6系列的隆重发布,标志着赛灵思公司致力于提高FPGA设计效率和增强FPGA易用性的崭新平台方法的开端。与半导体领域内的领先公司所采用的许多平台设计方法相同,赛...

2017-11-25 1861

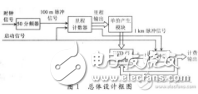

一种新型调频连续波高度表

本文介绍了一种新型调频连续波高度表,主要创新点在于:采用了FPGA/单片机的硬件 平台,通用性强,并具备现场软件升级能力;通过软件算法实现了高度搜索、高度跟踪、STC、AGC等功能,改变...

2017-11-25 5225

实现低功耗FPGA电子系统优化技巧与方法

本文首先与实测系统功耗进行对比,验证了Xilinx公司ISE软件包中FPGA功耗估算工具XPower的准确性。然后对FPGA设计中影响系统功耗的几个相互关联的参数进行取样,通过软件估算不同样点下的系统...

2017-11-25 2362

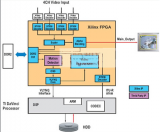

用FPGA构建智能监控视频新型系统架构

全视频帧速率下的高分辨率(HD)安全监控处理系统对处理器件的要求越来越高,单芯片DSP处理已经无法适应,多芯片、多核或者CPU+DSP的方式虽然在某些情况下能够满足需求,但其在PCB成本、系...

2017-11-25 1406

ASIC和FPGA设计优势和流程比较

ASIC 和 FPGA 具有不同的价值主张,选择其中之一之前,一定要对其进行仔细评估。2种技术的比较信息非常丰富。这里介绍了ASIC和FPGA的优势与劣势。...

2017-11-25 4881

设计PLD/FPGA时常用的时钟类型

无沦是用离散逻辑、可编程逻辑,还是用全定制硅器件实现的任何数字设计,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压或制造工艺的偏差情况下将导致错...

2017-11-25 5049

MicroBlaze性能详解

MicroBlaze是一个高度灵活可以配置的软核。你可以根据你设计的需要,对MicroBlaze进行裁减,用最少的资源完成设计的需要。 MicroBlaze的基本特性: 32个32位的通用寄存器 32位指令,3个操作数和两...

2017-11-25 9026

经验分享:如何选购FPGA开发板

FPGA技术当今已成为每一为电子工程师的必修课,在各个领域中都有广泛的应用.使得FPGA开发板的需求也大量的增加.大家可能出于不同的应用目的都需要购买FPGA 开发板。然而大多数人对...

2017-11-25 6087

利用FPGA开发板进行ASIC原型开发的技巧

ASIC设计在尺寸和复杂性上不断增加,现代FPGA的容量和性能的新进展意味着这些设计中的2/3能够使用单个FPGA进行建模。然而,这些设计中仍然保留有1/3(那就是说,所有ASIC设计中的1/9)要求一个基...

2017-11-25 1321

有效的利用FPGA的资源之管脚分配

在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自...

2017-11-25 3233

FPGA设计的基本原则、技巧与时序电路设计

FPGA设计的基本原则 面积与速度折衷原则 面积和速度是ASIC芯片设计中一对相互制约、影响成本和性能的指标,贯穿FPGA设计的始终。在FPGA设计中,面积是指一个设计消耗的FPGA内 部逻辑资源的数...

2017-11-25 1481

图像自适应分段线性拉伸算法的FPGA设计

由于红外图像的成像机理以及红外成像自身的原因,红外图像有对比度低、图像较模糊、噪声大等特点。因此抑止噪声,提高图像信噪比,以及调整红外图像对比度,以利于后续图像分析、目标...

2017-11-25 1482

软硬件协同设计机遇与挑战分析

软硬件协同设计是指对系统中的软硬件部分使用统一的描述和工具进行集成开发,可完成全系统的设计验证并跨越软硬件界面进行系统优化,软硬件协同设计是嵌入式技术发展的一大趋势,本P...

2017-11-25 978

基于赛灵思FPGA的快速9/7整形离散小波变换系统设计

CCSDS图像数据压缩标准中采用9/7整形离散小波变换为核心算法,该算法结构简单,易于硬件设计实现。文中基于FPGA设计实现了9/7整数离散小波变换系统,设计中使用内部RAM存储方式,减小了...

2017-11-25 828

采用Xilinx ML507评估平台的APU增强型FPGA设计

我们在此提供详细信息,说明Missing Link电子公司的工程师是如何为我们的示例设计生成必要文件的,以及如何使用这些文件在Xilinx ML507评估平台(其中包含一个Xilinx Virtex-5 XC5VFX70T器件)上复制...

2018-07-22 1514

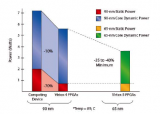

Virtex-5 FPGA的低功耗设计实现方案解析

VirtexTM-5系列产品的推出,使得Xilinx公司再一次成为向FPGA客户提供新技术和能力的主导力量。过渡至65纳米工艺的FPGA具备采用更小尺寸工艺所带来的传统优势:低成本、高性能和更强的逻辑能力...

2018-07-22 2080

视频监控系统新结构必须具备可扩展性

视频监控系统在火车站、机场、银行、娱场、乐商场甚至家庭的安保方面都是一种关键设备。随着安全风险的日益增大,在各种应用场合对已发事件进行视频监控和记录的需求都在逐步上升,这...

2017-11-25 2645

基于FPGA动态部分可重构技术在软件无线电中的应用的详细分析

本文介绍了将现场可编程门阵列(FPGA)专用硬件处理器集成到软件通信体系结构">软件通信体系结构(SCA)中的机制,实现了动态部分可重构技术在软件无线电(SDR)硬件平台中的应用,有效地...

2017-11-25 3191

采用FPGA+DSP+ARM的架构作为实时信息处理平台的详细分析

在飞控组件测试时,由于被测系统与上位机有一定距离,如果直接把遥测并行数据传送到上位机,将会出现数据信号的衰减和信号延时问题,有可能使信号时序错位,从而达不到系统测试的要求...

2017-11-25 13924

基于FPGA的多时钟片上网络虚拟直通路由器设计

网络拓扑:在设计中,选择Mesh拓扑结构。Mesh结构拥有最小的面积开销以及低功耗的特点。此外,Mesh的线性区的节点数量规模大以及通道较宽。同时,Mesh也能很好地映射到FPGA下的底层路由结构...

2018-07-22 2606

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |