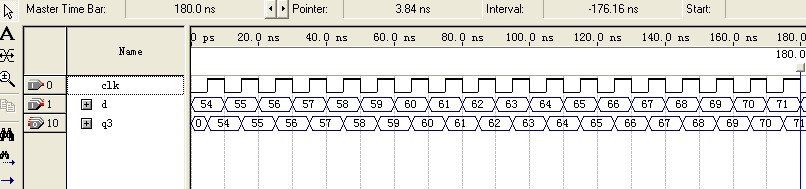

阻塞与非阻塞赋值 首先从名字上理解,阻塞赋值即赋值没完成,后边的语句将无法执行,非阻塞刚好与其相反,即赋值完不完成并不阻碍后续程序的执行,所以我们常说非阻塞赋值的对象并未立马得到新值,如果从时序来看

2017-09-19 18:32:43 11967

11967 来源:《Verilog数字系统设计(夏宇闻)》 阻塞和非阻塞赋值的语言结构是Verilog 语言中最难理解概念之一。甚至有些很有经验的Verilog 设计工程师也不能完全正确地理解:何时使用非阻塞

2021-08-17 16:18:17 6000

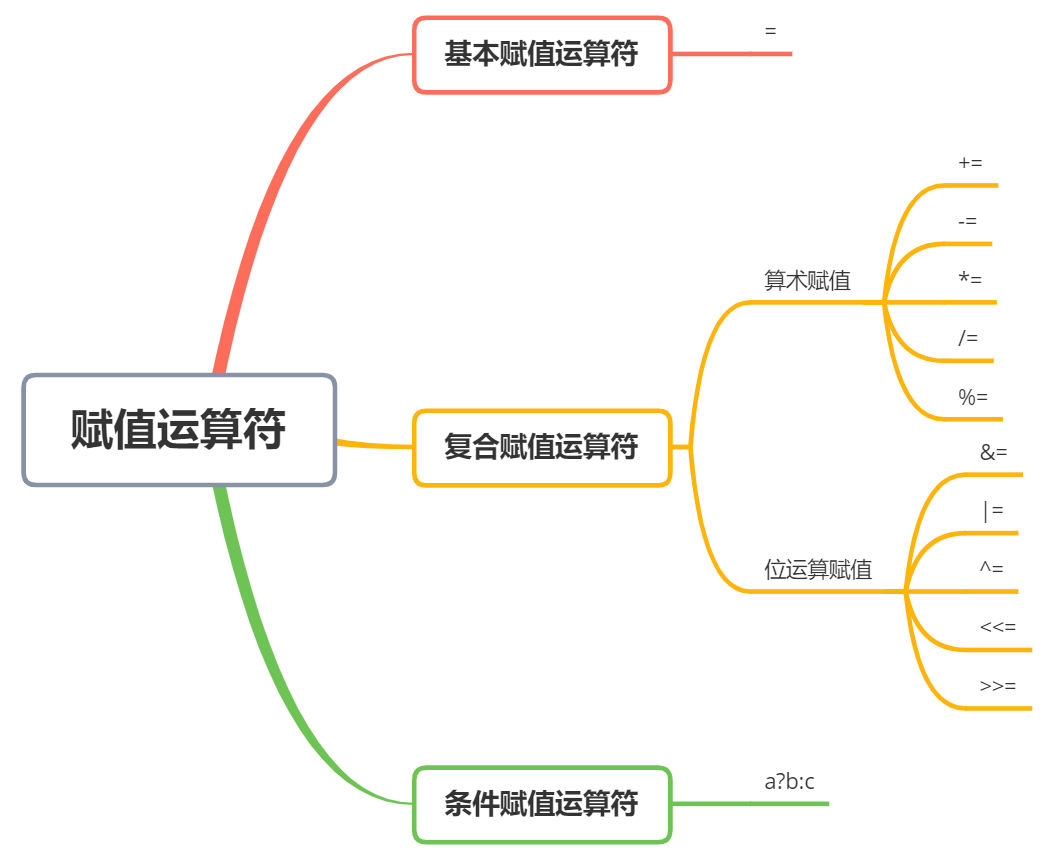

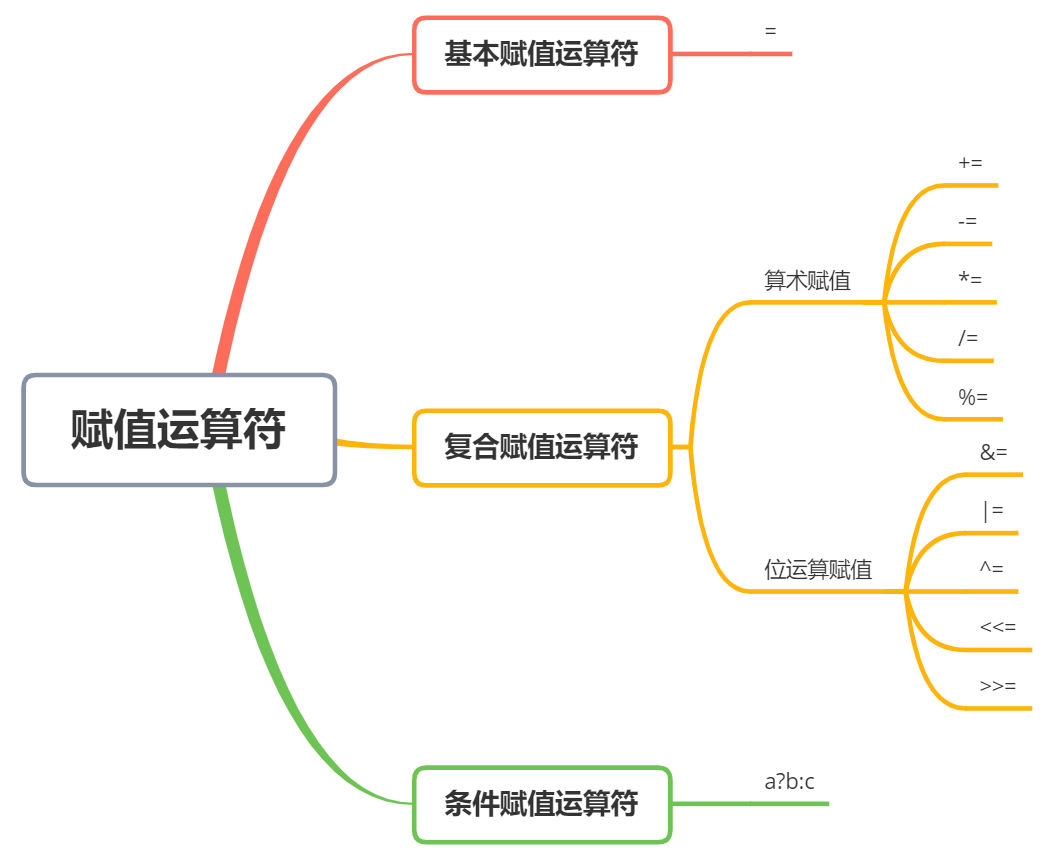

6000 在C语言中,赋值运算符用于将一个值赋给变量。

2023-08-18 16:38:13 837

837

阻塞赋值左式延时实验的设计,适合新手学习参考

2023-09-22 07:12:59

本文通过Verilog事件处理机制,详细讨论了阻塞与非阻塞赋值的区别、联系及其应用示例。

2021-05-10 06:59:23

//处理按键标志位always @(posedge sys_clk or negedge sys_rst_n) begin if(!sys_rst_n) key_flag[1:0]

2019-05-15 23:20:39

里面,因为硬件资源获得的同时往往伴随着一个中断。 注意:驱动程序需要提供阻塞(等待队列,中断)和非阻塞方式(轮询,异步通知)访问设备。 休眠(被阻塞)的进程处于一个特殊的不可执行状态。这点非常重要,否则

2018-07-09 08:19:59

里面,因为硬件资源获得的同时往往伴随着一个中断。 注意:驱动程序需要提供阻塞(等待队列,中断)和非阻塞方式(轮询,异步通知)访问设备。 休眠(被阻塞)的进程处于一个特殊的不可执行状态。这点非常重要,否则

2018-07-04 07:23:24

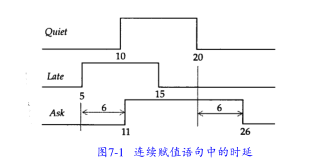

语句的执行,延迟后才执行赋值,这种赋值语句是不可综合的,在需要综合的模块设计中不可使用这种风格的代码。 非阻塞赋值操作符用小于等于号(即

2018-07-03 10:23:19

语句的执行,延迟后才执行赋值,这种赋值语句是不可综合的,在需要综合的模块设计中不可使用这种风格的代码。 非阻塞赋值操作符用小于等于号(即

2018-07-09 05:08:55

各位大师:请教一个问题。always @(posedge clk or posedge rst)if (rst) y1

2016-01-09 13:51:59

本帖最后由 eehome 于 2013-1-5 10:05 编辑

非阻塞赋值容易错语法点讨论请教下大家!我发现光盘里的例程有一段是这样子的:always @(dac_sta

2012-12-22 09:53:14

嗨!我不明白非阻塞分配是如何按顺序或并行执行的?永远@(posedge clk)开始x = 2;y = x;结束VS永远@(posedge clk)叉子x = 2;y = x;加入VS赋值x = 2

2019-04-22 10:02:08

非阻塞式如何读取矩阵按键?

2022-01-17 08:17:56

非阻塞模式LCD多级菜单的设计及其应用

2012-08-18 15:34:00

1,在阻塞赋值中,说是前边赋值阻塞后边赋值,但是看波形明明是同时变化,这是为什么?2,在if ,else if, else语句中说是顺序执行,是时钟跳一个周期判断一次吗,还是同时判断,如果是同时判断为什么说是顺序执行?3,是组合逻辑中用=,非组合逻辑中用

2019-05-29 01:09:27

Verilog的两个误区:使用Reg类 型还是Net类型:Reg类 型只在过程块中被赋值;而Net类型则在过 程块外面被赋值或者驱动.阻塞赋值和非阻塞赋值:Verilog中竞争发生的条件:两个或多个

2019-03-26 08:00:00

Verilog阻塞和非阻塞原理分析在Verilog语言最难弄明白的结构中“非阻塞赋值”要算一个。甚至是一些很有经验的工程师也不完全明白“非阻塞赋值”在仿真器(符合IEEE标准的)里是怎样被设定执行

2009-11-23 12:02:57

Verilog中阻塞赋值与非阻塞赋值的区别

2020-12-30 06:22:29

[table][tr][td] Verilog中有两种为变量赋值的方法。一种叫做连续赋值,另一种叫做过程赋值。过程赋值又分为阻塞赋值和非阻塞赋值。阻塞性赋值使用“=”为变量赋值,在赋值结束前不可以进行其他操作,在赋值结束之后继续后面的操作。这个过程就好像阻断了程序的运行。非阻塞赋值使用“

2018-07-03 03:06:04

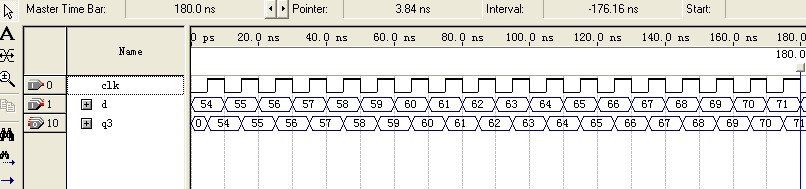

图一图二图三图四最近写了一个16位二级流水线加法器,并进行了一下仿真。发现在always块中采用阻塞赋值(=)和非阻塞赋值(

2016-09-09 09:18:13

时,dreg还是变成了areg这样不就是延时3个时钟周期了吗?为什么不是这样呢?另外,阻塞型赋值语句,规定是,顺序执行语句,每种状态一个接一个执行,非阻塞型赋值语句,规定是,并行赋值语句,当执行语句时同事计算

2017-09-20 15:10:01

`阻塞与非阻塞赋值首先从名字上理解,阻塞赋值即赋值没完成,后边的语句将无法执行,非阻塞刚好与其相反,即赋值完不完成并不阻碍后续程序的执行,所以我们常说非阻塞赋值的对象并未立马得到新值,如果从时序来看

2017-04-05 09:53:11

一般情况下串口通信中read()函数都是阻塞的。当然也可以通过设置文件等方法把串口设为非阻塞的。这里就有一个问题,当串口设置为阻塞状况下,如果读不到数据程序应该挂起。这种所谓的读不到数据是指读不到

2011-07-14 15:57:26

刚学verilog,试了一下非阻塞赋值,代码如下, 很简单module test(clk,in,out);input clk;input in;output reg out;always @(posedge clk)out

2012-10-30 09:20:14

这个是非阻塞赋值,b的值为0,仿真结果也是0module TOP(input clk,input rst,output reg b );reg a,c;always@(posedge clk or negedge rst)beginif(~rst)begina

2015-09-13 15:55:05

语句完成执行;• 非阻塞性过程赋值:对目标的赋值是非阻塞的(因为时延),但可预定在将来某个时间发生。阻塞性过程赋值用操作符“=”完成,例如下面的实例:always@ (A or B or Cin

2018-09-26 09:16:55

阻塞赋值与非阻塞赋值原理分析实验目的:掌握阻塞赋值与非阻塞赋值的区别实验平台:无实验原理:阻塞赋值,操作符为“=”,“阻塞”是指在进程语句(initial和always)中,当前的赋值语句阻断了其后

2016-12-25 01:51:24

资源则挂起进程。直到满足可操作的条件后再进行操作。被挂起的进程进入休眠状态,被从调度器的运行队列移走,直到等待的条件被满足。非阻塞—进程在不能进行设备操作时并不挂起,会放弃或者不断的查询,直到可以进行

2015-10-30 21:57:46

:1) 在赋值时刻开始时,计算非阻塞赋值RHS表达式。2) 在赋值时刻结束时,更新非阻塞赋值LHS表达式。 这段代码在posedge clk到来时,计算所有的RHS(Right Hand Side)的值

2016-11-03 20:26:38

的赋值语句会阻断其后语句的正常执行,也就是说后面的语句必须等到当前的赋值语句执行完毕才能执行。而且阻塞赋值可以看成是一步完成的,即:计算等号右边的值并同时赋给左边变量。非阻塞赋值,操作符为“

2020-02-24 20:09:13

阻塞与非阻塞作者:小黑同学一、 概述1、阻塞赋值对应的电路往往与触发沿没有关系,只与电平的变化有关系。阻塞赋值符号“=”。2、非阻塞赋值对应的电路结构往往与边沿触发有关系,只有在触发沿时才有可能发生赋值的情况。非阻塞赋值符号“

2020-04-24 14:49:45

立即学习>>梦翼师兄FPGA培训(纯视频),手把手带你入门FPGA写在前面的话开发过程中,我们用的最多的恐怕就是赋值语句了,我们常用的赋值方式有两种:阻塞赋值和非阻塞赋值。梦翼师兄刚开始

2019-12-22 14:21:37

,主要通过简单的例子对比了Verilog语法中阻塞赋值和非阻塞赋值的区别,通过证明非阻塞赋值多种赋值顺序生产电路的唯一性,与非阻塞赋值多种赋值书序生成电路的不确定性,来展示使用非阻塞赋对设计可预测性

2015-09-24 14:02:15

设计③ 如何给端口选择正确的数据类型④ Verilog语言中latch的产生⑤ 组合逻辑反馈环⑥ 阻塞赋值与非阻塞赋值的不同⑦ FPGA的灵魂状态机⑧ 代码风格的重要性[hide][/hide]

2016-08-17 05:56:55

什么是Verilog HDL阻塞赋值?主要应用在哪些方面?

2019-08-02 06:22:43

如果我们要处理的情况符合下面的几种之一,我们可以考虑一下使用非阻塞的方式来处理并发的情况。有多线程的情况要处理,但是很少出现并发冲突的,比如以读取为主的涉及到的并发逻辑非常复杂,希望可以减低并发代码

2021-08-24 08:11:32

@ (posedge GlobalClk)RegC = RegB;由于过程性赋值立即发生,即没有任何时延,所以根据首先执行哪一条always语句,RegC取不同的值,这就产生了竞争。书上说使用非阻塞性赋值可以避免产生竞争状态,为什么??求助...

2013-11-07 10:16:34

我打开这个串口的时候没有设置非阻塞的标志,应该是默认阻塞的吧,但是上位机不向串口发送东西,也就是read没有读到东西的时候下面的printf还是会一直打印。我理解的阻塞就是程序一直等待在阻塞的地方,是不是我理解的有问题

2017-03-15 16:51:06

完成时刻,即把 RHS 赋值给 LHS 的时刻,它才允许别的赋值语句的执行。非阻塞赋值操作符用小于等于号 (即

2013-10-28 15:44:13

同步与异步,阻塞与非阻塞的区别

2021-01-26 06:12:37

)中,\"<=\"作为非阻塞赋值的一部分。

verilog中,一个语法结构不可能同时允许“表达式”和“语句”,

如果某处可以出现表达式,那么就不允许出现语句;

如果

2023-08-08 09:32:07

使用Select实现非阻塞网络编程

2021-03-30 07:34:03

用的verilog hdl。always块里的每个赋值语句间,有延迟的吗?如果有延迟是多大?还有非阻塞语句是并行执行的还是说在always块结束的时候再一句一句执行?之前一直搞C语言,到这里好多东西不习惯

2018-05-15 15:07:37

Verilog HDL语言中存在两种赋值语言:● 非阻塞型赋值语句● 阻塞型赋值语句1. 非阻塞型语句以赋值操作符“

2015-03-22 10:23:44

使用 _IT 函数转移到一个非阻塞系统。只是将传输命令从 HAL_I2C_Master_Transmit 更改为 HAL_I2C_Master_Transmit_IT 突然将我所有的结果变成了屏幕上的乱码,而不是像我以前那样漂亮的文本。我需要做什么才能从阻塞 I2C 命令变为非阻塞 I2C 命令?

2023-02-06 06:00:18

阻塞和非阻塞语句作为verilog HDL语言的最大难点之一,一直困扰着FPGA设计者,即使是一个颇富经验的设计工程师,也很容易在这个点上犯下一些不必要的错误。阻塞和非阻塞可以说是血脉相连,但是又有着本质的差别

2011-03-15 10:57:34 6892

6892 本文通过Verilog事件处理机制,详细讨论了阻塞与非阻塞赋值的区别、联系及其应用示例。由本文可知,阻塞与非阻塞赋值灵活多变,底层实现也差异甚大。因而在数字电路设计时,依据

2011-08-28 17:59:19 574

574

VerilogHDL 中,有两种过程赋值方式,即阻塞赋值(blocking)和非阻塞赋值(nonblocking)。阻塞赋值执行时,RHS(righthandstatement)估值与更新LHS(lefthandstatement)值一次执行完成,计算完毕,立即更新。

2012-05-23 09:55:51 1192

1192

这是一个很好的学习阻塞和非阻塞的资料,对于FPGA的学习有很大帮助。

2016-04-22 11:00:45 11

11 学verilog 一个月了,在开发板上面写了很多代码,但是始终对一些问题理解的不够透彻,这里我们来写几个例子仿真出阻塞和非阻塞的区别

2017-02-11 03:23:12 1193

1193 在一开始学到阻塞和非阻塞的时候,所被告知的两者的区别就在于阻塞是串行的,非阻塞是并行的。但是虽然知道这个不同点,有些时候还是很难真正区分用两者电路的区别,下载资料内以一个简单的串行流水线寄存器为例进行了分析。

2017-09-16 09:34:07 4

4 设计背景: 阻塞 (=)和非阻塞(=)一直是在我们FPGA中讨论的问题,资深的学者都是讨论的是赋值应该发生在上升下降沿还是在哪里,我们在仿真中看的可能是上升下降是准确的,但是在时间电路中这就

2018-05-31 11:40:14 6357

6357

本文档的主要内容详细介绍的是PHP中传值赋值和引用赋值的详细资料详解。

2019-03-06 17:04:32 5

5 对于VerilogHDL语言中,经常在always模块中,面临两种赋值方式:阻塞赋值和非阻塞赋值。对于初学者,往往非常迷惑这两种赋值方式的用法,本章节主要介绍这两种文章的用法。其实,有时候概念稍微不清楚,Bug就会找到我们,下面一文扫清阻塞赋值和非阻塞赋值所有的障碍。

2020-01-30 17:41:00 20974

20974 1、阻塞赋值操作符用等号(即 = )表示。“阻塞”是指在进程语句(initial和always)中,当前的赋值语句阻断了其后的语句,也就是说后面的语句必须等到当前的赋值语句执行完毕才能执行。而且阻塞赋值可以看成是一步完成的,即:计算等号右边的值并同时赋给左边变量。

2020-04-25 08:00:00 0

0 阻塞赋值对应的电路往往与触发沿没有关系,只与输入电平的变化有关系。非阻塞赋值对应的电路结构往往与触发沿有关系,只有在触发沿时才有可能发生赋值的情况。

2020-06-17 11:57:41 10885

10885

如何区分VerilogHDL语言连续赋值与过程赋值方式

2020-07-20 09:16:29 6117

6117

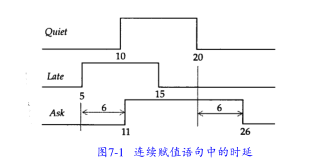

数据流模型化 本章讲述Verilog HDL语言中连续赋值的特征。连续赋值用于数据流行为建模;相反,过程赋值用于(下章的主题)顺序行为建模。组合逻辑电路的行为最好使用连续赋值语句建模。 7.1 连续

2021-03-05 15:38:21 3646

3646

下面给出一个基于阻塞赋值和非阻塞赋值的多级触发器级联实例,要求将输入数据延迟 3 个时钟周期再输出,并给出对应的 RTL 级结构图和仿真结果。 (1)基于 D触发器的阻塞赋值语句代码如下

2021-05-08 14:47:05 1799

1799

阻塞赋值和非阻塞赋值的可综合性 Blocking Assignment阻塞赋值和NonBlocking Assignment非阻塞赋值,原本是软件进程管理的术语。由于Verilog团队是从C语言发展

2021-05-12 09:45:09 2398

2398

在Verilog中有两种类型的赋值语句:阻塞赋值语句(“=”)和非阻塞赋值语句(“=”)。正确地使用这两种赋值语句对于Verilog的设计和仿真非常重要。 Verilog语言中讲的阻塞赋值

2021-12-02 18:24:36 5005

5005

由于赋值语句有阻塞赋值和非阻塞赋值两类,建议读者使用阻塞赋值语句“=”,原因将在“阻塞赋值和非阻塞赋值”中(现在还没有写)进行说明。

2022-03-15 10:40:20 1669

1669 Verilog HDL的赋值语句分为阻塞赋值和非阻塞赋值两种。阻塞赋值是指在当前赋值完成前阻塞其他类型的赋值任务,阻塞赋值由=来完成;非阻塞赋值在赋值的同时,其他非阻塞赋值可以同时被执行,非阻塞赋值由《=来完成。

2022-03-15 13:53:08 2524

2524 如例6.1所述,在多个“Always” 进程中使用阻塞赋值。程序块“Always”在时钟的正边缘触发,综合器推断时序逻辑。如前所述,所有阻塞赋值都在活动队列中进行计算和更新。读者请参阅之前分享的分层事件队列一文。

2022-09-06 09:44:02 3304

3304 今天我们把数组复习一下,数组是怎么用的,怎么对它进行定义,怎么对它进行赋值,然后把字符型数组大概说一下。

2022-12-08 08:55:19 592

592 阻塞赋值操作符用等号(即 = )表示。“阻塞”是指在进程语句(initial和always)中,当前的赋值语句阻断了其后的语句,也就是说后面的语句必须等到当前的赋值语句执行完毕才能执行。

2022-12-19 16:49:28 4607

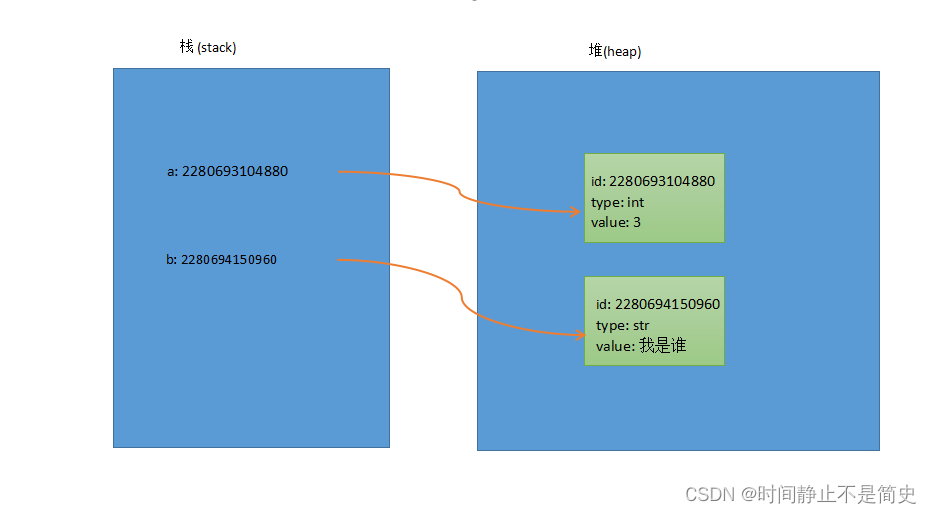

4607 1. 变量的声明和赋值 变量的声明和赋值:用于将一个变量绑定到一个对象上,格式: 变量 名 = 表达式 注意: 同Java一样, 变量在使用前必须先被初始化(先被赋值)! 最简单的表达式就是字面

2023-03-05 17:11:26 985

985

使用逻辑门和连续赋值对电路建模,是相对详细的描述硬件的方法。使用过程块可以从更高层次的角度描述一个系统,称作行为级建模(behavirol modeling)。 1. 过程赋值 阻塞赋值和非阻塞赋值

2023-03-17 21:50:05 368

368 当元素的数据类型和数组界限(最低和最高的可能的数组索引)相匹配时,能够将一个完整数组赋值给另一个数组。如果是这样,在赋值符后指定数组的标识符。下面的赋值是有效的:

2023-04-10 11:46:59 555

555 对于VerilogHDL语言中,经常在always模块中,面临两种赋值方式:阻塞赋值和非阻塞赋值。对于初学者,往往非常迷惑这两种赋值方式的用法,本章节主要介绍这两种文章的用法。其实,有时候概念稍微不清楚,Bug就会找到我们,下面一文扫清阻塞赋值和非阻塞赋值所有的障碍。

2023-06-01 09:21:57 514

514 阻塞通信(Blocking Communication):当进行阻塞通信时,调用者在发起一个I/O操作后会被阻塞,直到该操作完成返回才能继续执行后续代码。

2023-06-15 17:32:21 3580

3580 可通过赋值运算,可以将一个表达式的值分配给一个变量。赋值表达式的左侧为变量,右侧为表达式的值。

2023-06-19 10:57:16 3654

3654 关于阻塞函数和非阻塞函数在CAN和LIN相关的开发库里,不可避免的会出现“收”和“发”的函数。如何快速有效的处理数据,是开发中重要的事项。

2022-07-05 14:38:43 691

691

今天给大家普及一下阻塞赋值和非阻塞赋值的相关知识

2023-07-07 14:15:12 1237

1237

”=“阻塞赋值与”<=“非阻塞赋值是verilog语言中的两种不同的赋值方式,下面将对两种赋值方式进行比较。方便进行理解和使用。

2023-09-12 09:06:15 587

587

阻塞 IO 模型 在Linux ,默认情况下所有的 socket 都是阻塞的,一个典型的读操作流程如图所示。 阻塞和非阻塞的概念描述的是用户线程调用内核 IO 操作的方式:阻塞是指 IO 操作需要

2023-10-08 17:16:51 426

426

阻塞就是外部有阻塞干扰信号的时候,设备还可以正常运行。一般分为带内阻塞和带外阻塞,由于直放站都是做宽带设备,一般只提带外阻塞。

2023-10-10 11:22:37 546

546 并赋值可以通过使用PL/SQL语句块或使用SQL*Plus工具来实现。下面将详细介绍这两种方法以及它们的具体用法。 使用PL/SQL语句块定义和赋值变量: 在Oracle SQL中,PL/SQL是一种过程化语言,允许在代码中定义和使用变量。下面是一个示例的PL/SQL语句块,展示了如何定义和赋值一

2023-12-06 10:46:32 553

553 Verilog是一种硬件描述语言,用于设计和模拟数字电路。在Verilog中,同步和异步是用来描述数据传输和信号处理的两种不同方式,而阻塞赋值和非阻塞赋值是两种不同的赋值方式。本文将详细解释

2024-02-22 15:33:04 202

202

电子发烧友App

电子发烧友App

评论