为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2013-06-21 15:40:41 19922

19922

ZedBoard开发板上的OLED使用的是SPI协议,并且只支持写,不支持读,因此控制OLED就是在SCLK的时钟下,通过SDIN进行命令和数据的传输。##系统采用可软硬件协同设计的Zynq器件,定制硬件IP核,采用传统ARM程序设计方法设计OLED驱动程序和测试程序,实现了实时显示。

2014-09-04 16:16:03 17312

17312 本文主要介绍基于zynq的IIC的驱动架构,通过代码编写来深入了解IIC驱动的内容和机制。 1. IIC驱动架构 IIC驱动包含两部分:IIC总线驱动和设备驱动。总线驱动是对硬件设备适配器端的实现

2020-11-30 15:45:16 5253

5253 目前 i.MXRT1xxx 系列主要分为 i.MX RT10xx 和 i.MXRT11xx 两大分支。这两个分支的时钟系统设计是有一些差异的,不过总体来说,架构差别不大,我们以如下 i.MXRT1170 的时钟架构为例来具体介绍。

2022-07-08 17:05:47 1359

1359 FPGA 芯片整体架构如下所示,大体按照时钟域划分的,即根据不同的工艺、器件速度和对应的时钟进行划分。

2022-10-20 09:58:03 2723

2723 。Ultrascale+采用16ns,有3个系列:Artix,Kintex,Virtex。不仅是工艺制程方面,在其他方面也存在较大改进,如时钟资源与架构,本文将重点介绍Ultrascale的时钟资源与架构,Ultrascale+和Ultrascale大体上相似。

2025-04-24 11:29:01 2264

2264

你是否曾好奇过,手机、电脑甚至智能手表的时间为何能精准同步?这背后离不开两类关键元器件的协作:时钟芯片和晶振。尽管它们都与时间信号相关,但功能定位和技术原理却截然不同。本文将深入解析两者的区别,帮助

2025-12-16 15:58:04 3876

3876

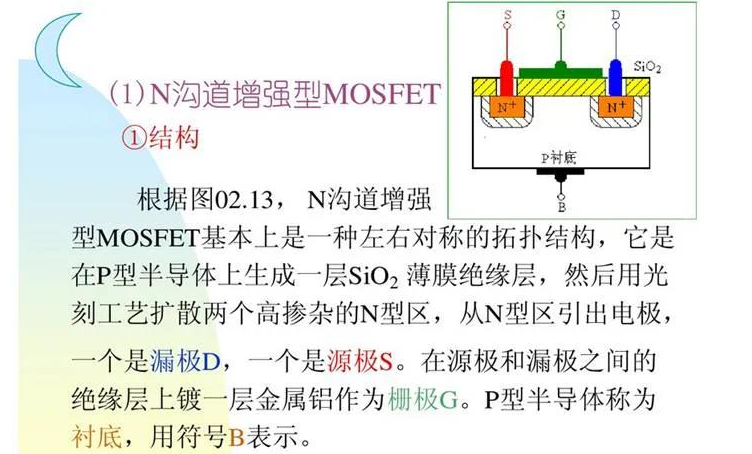

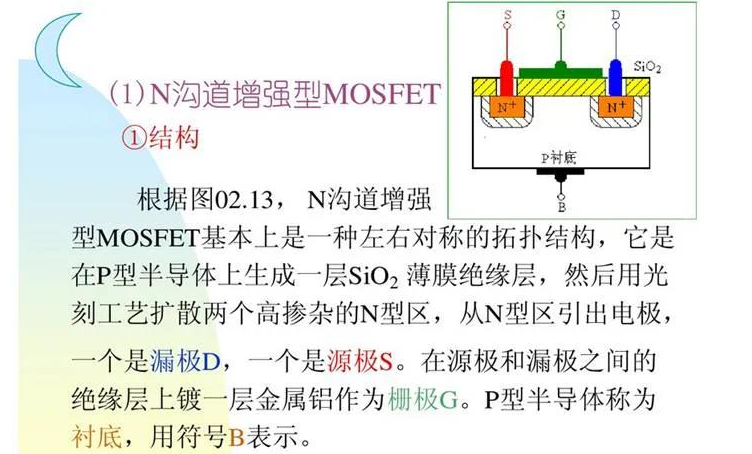

基本上就是这样理解的。无论 MOSFET 功率开关处于集成状态或外置状态,它们的根本性质并不会发生变化,所以并不需要对它们进行区别对待,而驱动它们的原理当然也是完全一样的。 要想驱动 MOSFET,首先需要对 MOSFET 的元件特性有个基本的了解,

2021-02-01 16:15:51 9629

9629

ZYNQ Ultrascale XCZU9EG这款芯片怎么看能支持的时钟范围是多少?本人已经翻过该芯片的datasheet,但是不知道具体在哪个地方来看能够支持的时钟范围,希望有经验的人指点一下,一般这种芯片应当从哪些地方来看支持的最大时钟~感谢!!

2019-11-01 22:45:03

ZYNQ架构双核ARM Cortex-A9 处理器:ARM Cortex-A9 是一个应用级的处理器,能运行完整的像Linux 这样的...

2022-01-25 06:13:33

为什么时钟转发到zynq的外部pmod有DC偏移和低幅度?注:同样的设计可以使用三个名为Spartan6 lx9的Xilinx fpgas,Spartan 3入门套件和Zedboard。所以我在代码

2020-03-27 10:26:22

本文主要对嵌入式开发平台Zynq芯片的发展历史、基础架构和应用等方面的知识进行了介绍,其中有博主自己的**理解与认识**,不是千篇一律的datasheet翻译。感兴趣的小伙伴可以点进来看看!

2021-11-08 06:13:30

,我不得不使用Bus2IP_Clk作为我的verilog设计的clk输入。这和我的zynq板的时钟频率一样吗?问候以上来自于谷歌翻译以下为原文Hi, I am using zynq zc702

2019-03-04 13:02:20

首先,我们需要先理解比较重要的几个概念。时钟周期时钟周期也叫振荡周期或晶振周期,即晶振的单位时间发出的脉冲数,一般有外部的晶振产生,如12MHz=12×10的6次方,即每秒发出12000000个脉冲

2022-02-24 07:16:48

转时钟抖动的理解

2016-10-05 12:08:25

处于正常工作的状态)。比如51单片机使用典型的12MHz晶振作为时钟源,则外设如IO口、定时器、串口等设备的驱动时钟速率便已经是固定的,用户无法将此时钟速率更改,除非更换晶振。解析STM32的时钟树[hide][/hide]

2011-10-21 14:36:05

你好,我使用的是zc706评估板。我正在尝试将我的主板与RF卡连接,我有以下问题。我试图在一个引脚上驱动一个时钟,但它似乎没有工作。 Ι用示波器测量输出引脚。 Fyi,我将zynq处理系统的主时钟

2019-09-26 08:16:13

您好:

我想咨询AD9681是否可以被zynq-7020的PL端驱动(zynq7020的性能是否足够)。我们需要做卫星的探测载荷,由于卫星能源控制严格,我们需要低功耗、多通道(至少8个)、高采样率

2023-12-04 08:18:57

AUTOSAR架构深度解析本文转载于:AUTOSAR架构深度解析AUTOSAR的分层式设计,用于支持完整的软件和硬件模块的独立性(Independence),中间RTE(Runtime Environment)作为虚拟功能...

2021-07-28 07:02:13

AUTOSAR架构深度解析本文转载于:AUTOSAR架构深度解析目录AUTOSAR架构深度解析AUTOSAR分层结构及应用软件层功能应用软件层虚拟功能总线VFB及运行环境RTE基础软件层(BSW)层

2021-07-28 07:40:15

Arm架构之Arm内核解析

2020-12-29 08:01:57

ESP32-C3,ESP-IDF版本4.3.2

使用I2C驱动OLED(驱动芯片SSD1306),开机正常驱动显示,持续刷新屏幕,运行一段时间后,总是会出现如下错误:

(1629509

2024-06-19 07:06:05

LPC1768时钟解析:

2016-12-29 17:41:01

在RCC——APB1PERIPH1描述中有个时钟是PWR时钟,PDF上说的是电源接口时钟。这个怎么理解、、、请教大侠们

2019-08-19 22:15:22

雷龙发展是专门做SD NAND的厂商,目前我们已经和很多MCU平台(包括ST、TI等)配合量产过。在这里简单的跟大家交流一下SD NAND这个东西,SD NAND的架构简单理解如下: SD NAND

2021-12-08 08:25:11

终于是又要开始了arm-linux了,隔了段时间没搞还真又忘记了。先从安装arm-linux-gcc-4.3.2开始吧 也不知道这个工具链是不是适合arm926ejs的,先用下看吧 找了几个版本

2018-07-03 06:53:50

你好,我在Win10中使用vivado 2016.2 for zynq7020。我的时钟方案是zynq PS FCLK_CLK0-->时钟向导IP输入(Primitive PLL)的输入。合成

2018-11-05 11:40:53

持PS+PL的架构,灵活使用PL。Zynq上的存储器接口也很丰富,包括DDR控制器,Quad-SPI控制器、Nand/NOR/SRAM控制器等。通用IO(GPIO)在Zynq上,我们可以通过MIO引出最多54个

2015-07-07 20:22:49

2.中断及时钟的理解及知识1.时钟基础2.中断(1)中断简介(2)中断步骤1.时钟基础 这里主要介绍系统时钟。 先放图,但在使用外部时钟时无法运行。分机时钟通过时钟使能引脚提供,路由到MMCM,通过

2019-04-09 09:12:26

关于Zynq的理论部分,文大部分截图摘抄自《zynqbook》ZYNQ架构双核ARM Cortex-A9 处理器:ARM Cortex-A9 是一个应用级的处理器,能运行完整的像Linux 这样

2021-07-23 10:11:25

架构的分析和自己的理解。在讨论单片机内存管理之前,我想先说一下关于计算机的内存是如何管理的。根据《C++ Primer Plus(第6版)》这本书中所讲,C++(就内存管理方式而言类似C)有3种管理...

2022-01-20 06:13:46

关于异步时钟域的理解的问题: 这里面的count[25]、和count[14]和count[1]算是多时钟域吧?大侠帮解决下我的心结呀,我这样的理解对吗?

2012-02-27 15:50:12

AUTOSAR架构深度解析本文转载于:AUTOSAR架构深度解析AUTOSAR的分层式设计,用于支持完整的软件和硬件模块的独立性(Independence),中间RTE(Runtime

2021-07-23 08:34:18

STM32F103学习笔记四时钟系统本文简述了自己学习时钟系统的一些框架,参照风水月1. 单片机中时钟系统的理解1.1 概述时钟是单片机的脉搏,是单片机的驱动源用任何一个外设都必须打开相应的时钟不使

2021-08-12 08:06:09

在配置ZYNQ的一些外设的时钟时,在Clock Configuration中无法修改时钟频率的解决比如,在这里,想修改QSPI的时钟频率,发现是无法修改的。如下图而能修改时钟频率的情况如下图:造成

2022-01-18 23:08:24

本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2021-04-07 06:30:45

秒(100 Mhz)关闭和打开一个LED,我这样做是为了验证如何更改ZYNQ的时钟频率使用vivado的约束。这是我放在.xdc文件中生成不同的时钟频率set_property PACKAGE_PIN

2020-04-01 08:46:16

【追踪嫌犯的利器】定位技术原理解析(4)

2020-05-04 12:20:20

对STM32时钟树的理解

2021-08-02 10:28:20

ARM处理器是一个32位元精简指令集(RISC)处理器架构,其广泛地使用在许多嵌入式系统设计。ARM全称为Acorn RISC Machine。ARM处理器本身是32位设计,但也配备16位指令集

2017-12-04 10:31:40

【阅读这篇文章,你能了解到什么】1. 从事嵌入式开发12年的我,对架构设计的理解;2. 对嵌入式系统中的架构设计要刻意训练;3. 嵌入式系统开发过程中的一些小技巧;4. 一个用于智能家居项目

2021-11-08 08:23:33

`手机通信原理解析:第 1 章 无线通信原理第2 章 移动通信系统第3 章 移动通信系统的多址接入技术第4 章 移动通信系统的语音编码第5 章 GSM移动通信系统的数字

2011-12-14 14:31:20

没用过zynq今天在看解析是发现汽车的CID上有用这个,不知道zynq有什么优势?

2024-04-23 15:01:58

关于linux UART驱动和tty架构的理解

2019-07-03 09:55:47

(Second Stage Boot Loader, SSBL),对于linux操行系统而言,这个阶段运行的就是uboot。5 SD卡启动文件解析 接下来我们可以通过用于zynq运行linux的SD卡来

2019-04-16 06:56:32

问题想必是每一个初次使用AXI HP总线的开发者希望评估到的。那么,本实例就搭了一个很基本的架构出来,使用100MHz的AXI HP总线时钟频率(可更改),任意开关每个独立的AXI HP读或写通道,以评估

2019-11-28 10:11:38

大家好,我想在我的测试板上使用FPGA中唯一的时钟。(FPGA是zynq ultrascale +,时钟来自quad228(GTH收发器)的clk0。)我尝试了各种各样的东西,比如

2020-04-30 08:16:16

【锂知道】锂电池基本原理解析:充电及放电机制电池充电最重要的就是这三步:第一步:判断电压

2021-09-15 06:47:08

理解不同类型的时钟抖动

抖动定义为信号距离其理想位置的偏离。本文将重点研究时钟抖动,并探讨下面几种类型的时钟抖动:相邻周期抖动、周期抖动、时间间隔误

2010-01-06 11:48:11 2094

2094

电动汽车动力转向技术原理解析

电动汽车配置的动力转向系统必须符合电驱动、高效利用能源的要求。目前,电动汽车使用的动力转向系统主要有

2010-03-17 15:18:56 2289

2289 虚拟存储器部件原理解析

2010-04-15 14:25:20 3560

3560 本文是对IGBT驱动的一些概念的理解

2012-10-24 14:46:02 5599

5599

触摸屏的应用与工作原理解析

2017-02-08 02:13:17 38

38 深入解析ARM Cortex-A12架构

2017-01-14 12:31:49 21

21 浅谈数字总线的时钟架构

2017-01-17 19:54:24 12

12 本文主要介绍对zynq内部结构的理解,具体的跟随小编一起来了解一下吧。

2018-07-13 07:10:00 6385

6385

在所有Zynq All Programmable SoC 的内部, 你都会发现一个双核的ARM Cortex -A9 MPCore处理器,而且Zynq SoC中的这两个处理器中都设有ARM NEON SIMD架构扩展集。

2017-02-10 12:15:11 3188

3188

基于抽象文法的通用程序理解架构研究_罗玉玲

2017-03-17 09:53:48 0

0 在对zynq进行Linux驱动开发时,除了需要针对zynq内ARM自带的控制器适配驱动外,还需要对zynq PL部分的IP核进行驱动开发。对于ARM来说,zynq PL部分的IP核就是一段地址空间

2018-06-30 15:10:00 10289

10289 ARM新锐Cortex_A7核心架构解析

2017-09-28 10:10:02 11

11 采用Z7020实现的高性能马达控制可以又小地减少振动和电磁干扰。Zynq-7000软件/硬件架构可以通过适当的设计分区来提供足够的灵活性,从而有效地实现复杂的功能。

2018-05-24 15:12:00 6859

6859

PYNQ全称为Python Productivity for Zynq,即在原有Zynq架构的基础上,添加了对python的支持。Zynq是赛灵思公司推出的行业第一个可扩展处理平台系列,在芯片

2018-07-14 09:05:00 9314

9314

WEBENCH® 时钟架构

2018-08-02 01:03:00 4361

4361 了解新的UltraScale ASIC时钟架构:如何使用它,它带来的好处以及从现有设计迁移的容易程度。

另请参阅如何使用时钟向导配置时钟网络。

2018-11-29 06:40:00 4238

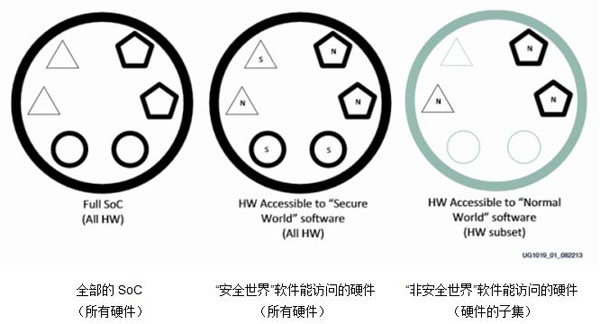

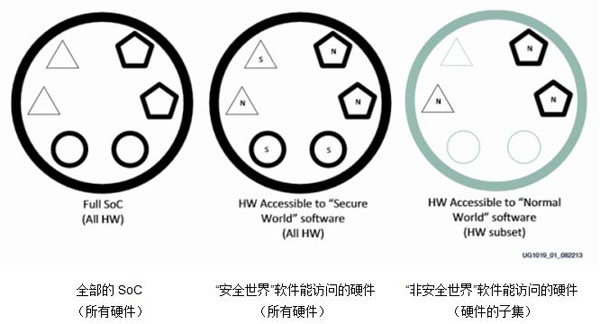

4238 现在,你可以通过阅读“对Xilinx Zynq-7000 All Programmable SoC中的ARM TrustZone架构进行编程”这本新鲜出炉的用户手册,来理解怎样更好的使用Zynq

2019-08-01 08:28:16 4127

4127

基于ZYNQ实现复杂嵌入式系统非常便利,其应用领域也越来越广泛,本文来从对ZYNQ芯片架构的理解来谈谈个人体会。

2020-09-05 11:44:57 5653

5653

引言:本文我们介绍区域时钟资源。区域时钟网络是独立于全局时钟的时钟网络。不像全局时钟,一个区域时钟信号(BUFR)的跨度被限制在一个时钟区域,一个I/O时钟信号驱动一个单一的Bank。这些网络对于源

2021-03-22 09:47:30 6215

6215

支持非常高频率的信号。了解全局时钟的信号路径可以扩展对各种全局时钟资源的理解。全局时钟资源和网络由以下路径和组件组成: 时钟树和网络:GCLK 时钟区域 全局时钟缓冲器 1. 时钟树和网络:GCLK 7系列FPGA时钟树设计用于低偏差和低功

2021-03-22 10:09:58 14973

14973

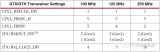

引言:本文我们介绍GTX/GTH收发器时钟架构应用,该文内容对进行PCIe和XAUI开发的FPGA逻辑设计人员具有实际参考价值,具体介绍: PCIe参考时钟设计 XAUI参考时钟设计 1.PCIe

2021-03-29 14:53:47 8384

8384

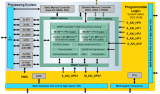

[导读] 基于ZYNQ实现复杂嵌入式系统非常便利,其应用领域也越来越广泛,本文来从对ZYNQ芯片架构的理解来谈谈个人体会。 俯瞰zynq ZYNQ主要由两大部分组成: 处理系统PS

2021-04-02 17:13:54 3501

3501

基于 ZYNQ 实现复杂嵌入式系统非常便利,其应用领域也越来越广泛,本文来从对 ZYNQ 芯片架构的理解来谈谈个人体会。

2021-04-28 10:18:06 5745

5745

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及

2021-05-10 16:51:39 4652

4652

解析MSP430系统时钟资源

2021-09-26 11:39:09 1

1 RTX51tiny 复杂应用---时钟、温度显示、按键解析

2021-11-21 13:06:03 27

27 ZYNQ架构

2021-11-30 18:51:04 13

13 [导读] 基于ZYNQ实现复杂嵌入式系统非常便利,其应用领域也越来越广泛,本文来从对ZYNQ芯片架构的理解来谈谈个人体会。俯瞰zynqZYNQ主要由两大部分组成:处理系统PS(Proce...

2021-12-01 18:06:10 0

0 探究USB协议架构及驱动架构

2022-01-25 16:35:27 1

1 基于ZYNQ实现复杂嵌入式系统非常便利,其应用领域也越来越广泛,本文来从对ZYNQ芯片架构的理解来谈谈个人体会。

2022-01-26 18:03:16 0

0 Processor is ready. Configure programable logic.在新专栏 Rapid TCP/IP on Zynq 中,将围绕 Xilinx Zynq 系列芯片,从 SDK 驱动,PS-...

2022-02-07 10:59:19 1

1 因为在S6或者其他7系列的FPGA中,是有一套非常成熟的FPGA加载机制(Xilinx有很详细的指导手册),但是来到Zynq时代,这个方式变了。为什么呢?因为现在zynq上有ARM了,所有的加载工作实际上可以借由ARM来实现

2022-05-09 10:53:02 4441

4441 ZYNQ处理系统端PS所有的外设都连接在AMBA(Advanced Microcontroller Bus Architecture)总线,而基于FPGA设计的IP则可以通过AXI接口挂载在AMBA总线上,从而实现内部各组件的互联互通。这里涉及到两个概念:

2022-08-15 09:42:24 2915

2915 [导读] 基于ZYNQ实现复杂嵌入式系统非常便利,其应用领域也越来越广泛,本文来从对ZYNQ芯片架构的理解来谈谈个人体会。

2022-10-11 09:06:27 1465

1465 ASPICE 和26262中ASPICE 和26262中的软件架构解析的软件架构解析

2022-10-25 11:53:34 1292

1292 史密斯圆图和阻抗匹配原理解析

2022-11-02 20:16:23 2716

2716 什么是晶振 晶振工作原理解析

2022-12-30 17:13:57 5330

5330

时钟API的使用 对于一般的驱动开发(非clock驱动),我们只需要在dts中配置时钟,然后在驱动调用通用的时钟API接口即可。 1、设备树中配置时钟 mmc0: mmc0 @0x12345678

2023-09-27 14:30:49 1253

1253 clock驱动实例 clock驱动在时钟子系统中属于provider,provider是时钟的提供者,即具体的clock驱动。 clock驱动在Linux刚启动的时候就要完成,比 initcall

2023-09-27 14:39:35 1963

1963

随着软件定义汽车与中央式电子电器架构的提出,以及自动驾驶技术应用、人机交互模式改变与网联化的需求,对网络架构的时钟系统提出了更高的要求与挑战。本次会议,北汇信息将从以下几点为大家带来关于网络架构的时钟系统的主题分享。车载应用演变车载时间系统需求时钟系统设计时间系统验证

2022-11-02 15:52:09 3

3 NVIDIA Blackwell数据手册与NVIDIA Blackwell 架构技术解析

2025-03-20 17:19:09 2004

2004 五大电磁频谱管理系统:原理、架构与应用全景解析

2025-09-26 10:21:20 405

405

电子发烧友App

电子发烧友App

评论