声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

asic

+关注

关注

34文章

1269浏览量

124053 -

赛灵思

+关注

关注

33文章

1797浏览量

133148 -

时钟

+关注

关注

11文章

1953浏览量

134543

发布评论请先 登录

相关推荐

热点推荐

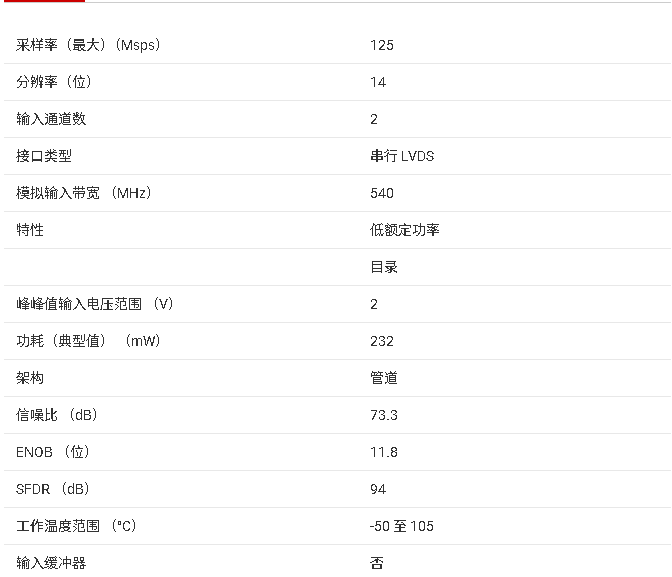

ADC3244E 具有扩展温度范围的双通道 14 位 125MSPS 模数转换器技术手册

该ADC3244E是一款高线性度、超低功耗、双通道、14位、25MSPS至125MSPS模数转换器(ADC)。该器件专为支持具有大动态范围要求的高输入频率信号而设计。输入时钟分频器为系统时钟架构设计提供了更大的灵活性,SYSREF输入可实现完整的系统同步。

璞致电子 UltraScale+ RFSoC 架构下的软件无线电旗舰开发平台

璞致电子 PZ-ZU49DR-KFB 开发板基于 Xilinx ZYNQ UltraScale+ RFSoC XCZU49DR 主控制器,以 "ARM+FPGA 异构架构" 为

AI芯片,需要ASIC

引擎。数据显示,中国AI芯片市场规模预计将从2024年的1425亿元迅猛增长至2029年的1.34万亿元,其中,ASIC架构产品将在国内市场占据主导地位。 AI ASIC是专为人工智能算法打造的专用集成电路。其核心特征在于,

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 异构架构下的智能边缘计算标杆

璞致电子推出PZ-ZU15EG-KFB异构计算开发板,搭载Xilinx ZYNQ UltraScale+ XCZU15EG芯片,整合四核ARM Cortex-A53、双核Cortex-R5F

AMD FPGA异步模式与同步模式的对比

本文讲述了AMD UltraScale /UltraScale+ FPGA 原生模式下,异步模式与同步模式的对比及其对时钟设置的影响。

FCO-L差分振荡器搭建时钟架构,全面剖析光模块与PCIe Gen6的时钟设计思路

随着通信速率进入100G、200G乃至400G时代,系统对时钟源的抖动容限和温漂性能提出更高要求。FCom富士晶振推出的FCO-L系列差分晶体振荡器具备50fs级别的超低相位抖动、宽温高稳等特点,成为光模块、PCIe Gen6平台和新一代数据中心的关键定时解决方案。

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

。Ultrascale+采用16ns,有3个系列:Artix,Kintex,Virtex。不仅是工艺制程方面,在其他方面也存在较大改进,如时钟资源与架构,本文将重点介绍Ultrascale

AD9253对时钟抖动的要求怎么样,应该选择怎样的时钟架构?

1:这款芯片支持连续采样、沿触发和外触发工作方式

2:时钟必须使用时钟芯片配置才行?使用有源晶振是否可以?

3:这款芯片对时钟抖动的要求怎么样,应该选择怎样的时钟架构?

发表于 04-15 06:43

CPLD 与 ASIC 的比较

在数字电子领域,CPLD和ASIC是两种广泛使用的集成电路技术。它们各自有着独特的优势和局限性,适用于不同的应用场景。 1. 定义与基本原理 1.1 CPLD(复杂可编程逻辑器件) CPLD是一种

微服务容器化部署好处多吗?

微服务容器化部署好处有很多,包括环境一致性、资源高效利用、快速部署与启动、隔离性与安全性、版本控制与回滚以及持续集成与持续部署。这些优势助力应用可靠稳定运行,提升开发运维效率,是现代软件架构的优质选择。UU云小编认为微服务容器化部署好处

ASIC和GPU的原理和优势

本文介绍了ASIC和GPU两种能够用于AI计算的半导体芯片各自的原理和优势。 ASIC和GPU是什么 ASIC和GPU,都是用于计算功能的半导体芯片。因为都可以用于AI计算,所以也被称为“AI

Verilog 与 ASIC 设计的关系 Verilog 代码优化技巧

Verilog与ASIC设计的关系 Verilog作为一种硬件描述语言(HDL),在ASIC设计中扮演着至关重要的角色。ASIC(Application Specific Integrated

新UltraScale ASIC时钟架构的使用及好处

新UltraScale ASIC时钟架构的使用及好处

评论