First Input First Output的缩写,先入先出队列,这是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。

FIFO(First Input First Output),即先进先出队列。在超市购物之后会提着我们满满的购物车来到收银台排在结账队伍的最后,眼睁睁地看着前面的客户一个个离开。这就是一种先进先出机制,先排队的客户先行结账离开。

fifo算法原理

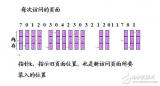

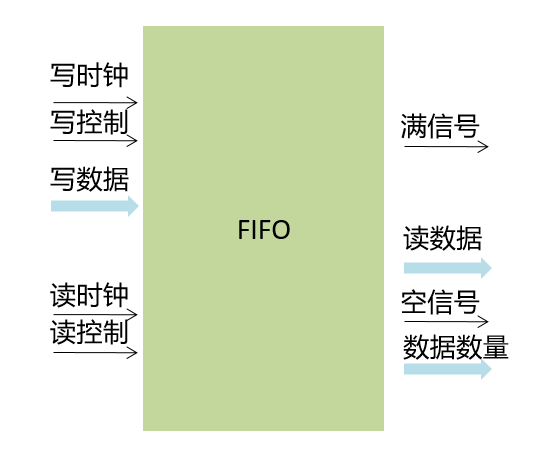

在计算机中,先入先出队列是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令(指令就是计算机在响应用户操作的程序代码,对用户而言是透明的)。如图1所示,当CPU在某一时段来不及响应所有的指令时,指令就会被安排在FIFO队列中,比如0号指令先进入队列,接着是1号指令、2号指令……当CPU完成当前指令以后就会从队列中取出0号指令先行执行,此时1号指令就会接替0号指令的位置,同样,2号指令、3号指令……都会向前挪一个位置,这样解释大家清楚了吧?

图1 先进先出队列

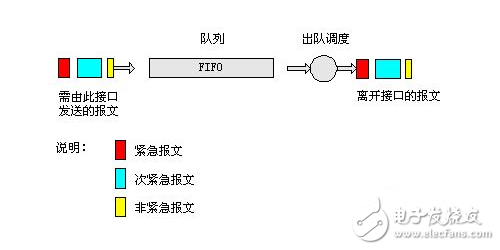

FIFO是队列机制中最简单的,每个接口上都存在FIFO队列,表面上看FIFO队列并没有提供什么QoS(Quality of Service,服务质量)保证,甚至很多人认为FIFO严格意义上不算做一种队列技术,实则不然,FIFO是其它队列的基础,FIFO也会影响到衡量QoS的关键指标:报文的丢弃、延时、抖动。既然只有一个队列,自然不需要考虑如何对报文进行复杂的流量分类,也不用考虑下一个报文怎么拿、拿多少的问题,而且因为按顺序取报文,FIFO无需对报文重新排序。简化了这些实现其实也就提高了对报文时延的保证。

FIFO关心的就是队列长度问题,队列长度会影响到时延、抖动、丢包率。因为队列长度是有限的,有可能被填满,这就涉及到该机制的丢弃原则。常见的一个丢弃原则叫做Tail Drop机制。简单地说就是该队列如果已经满了,那么后续进入的报文被丢弃,而没有什么机制来保证后续的报文可以挤掉已经在队列内的报文。在这种机制中,如果定义了较长的队列长度,那么队列不容易填满,被丢弃的报文也就少了,但是队列长度太长了会出现时延的问题,一般情况下时延的增加会导致抖动也增加。如果定义了较短的队列,时延的问题可以得到解决,但是发生Tail Drop的报文就变多了。

先进先出(FIFO)置换算法

这是最早出现的置换算法。该算法总是淘汰最先进入内存的页面,即选择在内存中驻留时间最久的页面予以淘汰。该算法实现简单,只需把一个进程已调入内存的页面,按先后次序链接成一个队列,并设置一个指针,称为替换指针,使它总是指向最老的页面。但该算法与进程实际运行的规律不相适应,因为在进程中,有些页面经常被访问,比如,含有全局变量、常用函数、例程等的页面,FIFO 算法并不能保证这些页面不被淘汰。

这里,我们只需要设置一个先进先出队列就可以。最先进入内存的页面最早被转换出去。

例如:假定系统为某进程分配了三个物理块,并考虑有以下的页面号引用串:

7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,7,0,1

结果为:

7

7 0

7 0 1

0 1 2

1 2 0

2 0 3

2 3 0

3 0 4

0 4 2

4 2 3

2 3 0

2 0 3

0 3 2

3 2 1

3 1 2

1 2 0

2 0 1

0 1 7

1 7 0

7 0 1

先进先出(FIFO)置换算法模拟源代码

[java] view plain copy/**

* 先进先出转换算法

* @author Administrator

*

*/

public class FIFO {

/**

* 内存块的个数

*/

public static final int N = 3;

/**

* 内存块数组

*/

Object[] array = new Object[N];

private int size;

/**

* 内存是非空为否

* @return

*/

public boolean isEmpty() {

if(0 == size)

return true;

else

return false;

}

public/**

* 内存是非空满

* @return

*/ boolean isFulled() {

if(size 》= N)

return true;

else

return false;

}

/**

* 元素(页框)的个数

* @return

*/

public int size() {

return size;

}

/**

* 查找元素o在数组中的位置

* @param o

* @return

*/

public int indexOfElement(Object o) {

for(int i=0; i《N; i++) {

if(o == array[i]) {

return i;

}

}

return -1;

}

/*public void push(Object o) {

Node p = new Node(o);

//Node p2 = head;

p.next = head;

head = p;

}*/

/**

* 页面转换

* @param obj

*/

public Object trans(Object obj){

Object e = null;

int t = 0;

if(indexOfElement(obj) != -1) {

t = indexOfElement(obj);

for(int i=t; i《size-1; i++) {

array[i] = array[i+1];

}

array[size-1] = obj;

} else {

if(!isFulled()){

array[size] = obj;

size ++;

} else {

for(int i=0; i《size-1; i++) {

array[i] = array[i+1];

}

array[size-1] = obj;

}

}

if( -1 == t) {

return null;

} else {

return array[t];

}

}

/**

* 输出内存区中的各数据

*/

public void showMemoryBlock() {

for(int i=0; i《size; i++) {

System.out.print(array[i] + “ ”);

}

}

/**

* 清空队列(页框)

*/

public void clear(){

}

/**

* @param args

*/

public static void main(String[] args) {

Integer iter[] = {7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,7,0,1};

FIFO fifo = new FIFO();

for(int i=0; i《iter.length; i++) {

fifo.trans(iter[i]);

fifo.showMemoryBlock();

System.out.println();

}

}

}

电子发烧友App

电子发烧友App

评论