芯片设计和验证工程师通常要为在硅片上实现的每一行RTL代码写出多达10行测试平台代码。验证任务在设计周期内可能会占用50%或更多的时间。尽管如此辛 苦,仍有接近60%的芯片存在功能瑕疵,需要返工。由于HDL仿真不足以发现系统级错误,芯片设计人员正利用FPGA来加速算法创建和原型设计。

利用FPGA处理大型测试数据集可以使工程师快速评估算法和架构并迅速做出权衡。工程师也可以在实际环境下测试设计,避免因使用HDL仿真器耗大量时 间。系统级设计和验证工具(如matlab和Simulink)通过在FPGA上快速建立算法原型,可以帮助工程师实现这些优势。

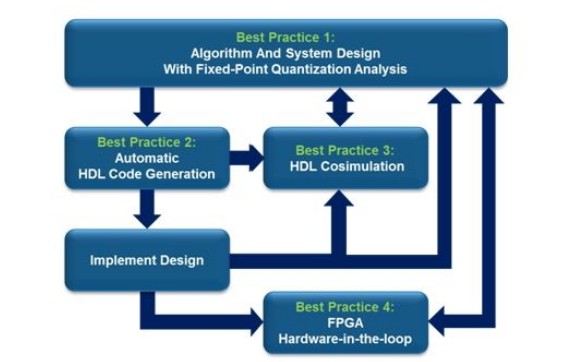

本文将介绍使用MATLAB和Simulink创建FPGA原型的最佳方法。这些最佳方法包括:在设计过程初期分析定点量化的效应并优化字长,产生更 小、更高效的实现方案;利用自动HDL代码生成功能,更快生成FPGA原型;重用具有HDL协同仿真功能的系统级测试平台,采用系统级指标分析HDL实现 方案;通过FPGA在环仿真加速验证(图1)。

为什么在FPGA上建立原型?

在FPGA上建立算法原型可以增强工程师的信心,使他们相信自己的算法在实际环境中的表现能够与预期相符。除了高速运行测试向量和仿真方案,工程师还可 以利用FPGA原型试验软件功能以及诸如RF和模拟子系统的相关系统级功能。此外,由于FPGA原型运行速度更快,可以使用大型数据集,暴露出仿真模型未 能发现的缺陷。

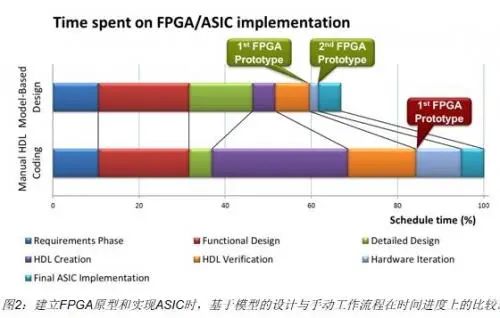

采用HDL代码生成功能的基于模型的设计可以使工程师有效地建立FPGA原型,如图2所示。该图向我们展示了这样一种现实情况:工程师经常缩短详细设计 阶段,试图通过尽快开始硬件开发阶段以符合开发周期的要求。现实中,当工程师发现定点算法达不到系统要求时,就得在HDL创建阶段重新审视详细设计阶段。这样的重叠工作将使HDL创建阶段延长(如紫色长条所示),并可能引发各种设计问题(如胶合逻辑或设计补丁)。

由于自动HDL代码生成流程比手工编码快,工程师得以把节省下来的时间投入到详细设计阶段,生成更优质的定点算法。与手动的工作流程相比,这种方法使工程师能够以更快的速度生成质量更佳的FPGA原型。

数字下变频器案例研究

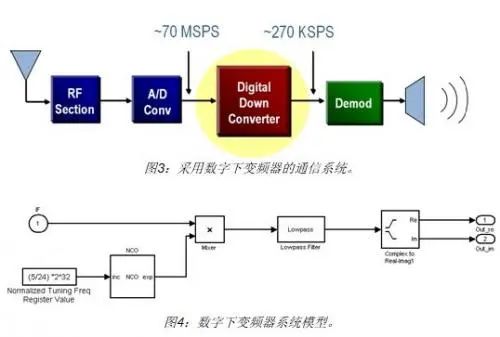

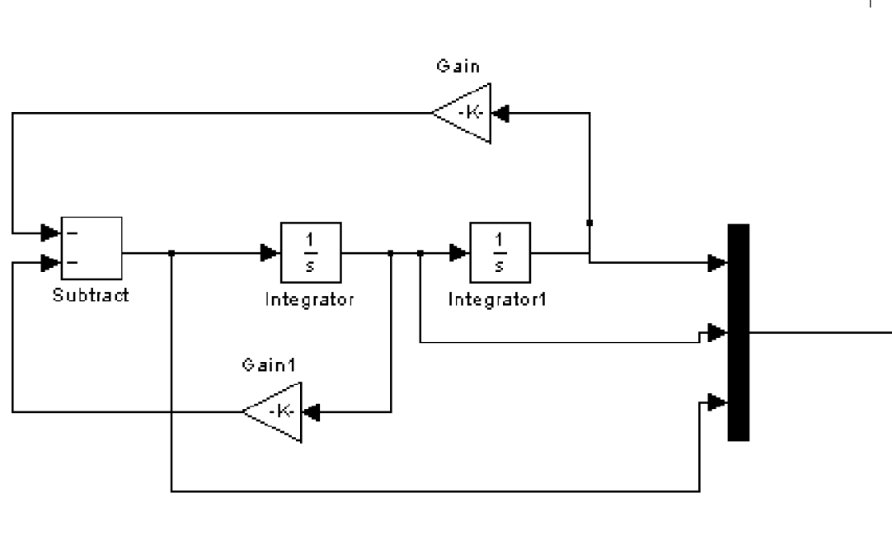

为了说明采用基于模型的设计建立FPGA原型的最佳方法,可借助数字下变频器(DDC)来进行案例研究。在众多的通信系统中,DDC是一种普通的构建块 (图3)。该构建块用于将高速通带输入转换为低速基带输出,以便使用较低采样率时钟进行处理。这样,在硬件实施阶段便可降低功耗、节约资源。DDC的主要 部件包括:数控振荡器(NCO)、混频器和数字滤波器链路(图4)。

在设计过程初期分析定点量化的效应

工程师通常使用浮点数据类型来测试新的构想和开发初始算法。然而,FPGA和ASIC硬件实现要求转换为定点数据类型,而这往往会造成量化误差。使用手 动工作流程时,通常在HDL编码过程中执行定点量化。在该工作流程中,工程师无法轻易地通过比较定点表示形式和浮点参考值量化定点量化的效应,而分析针对 溢出的HDL实现也同样不易。

为了明智确定所需的小数位数,在开始HDL编码过程之前,工程师需要某种方法来比较浮点仿真结果与定点仿真结果。增加小数位数可以减小量化误差;不过,这种方法需要增加字长(区域增多、功耗升高)。

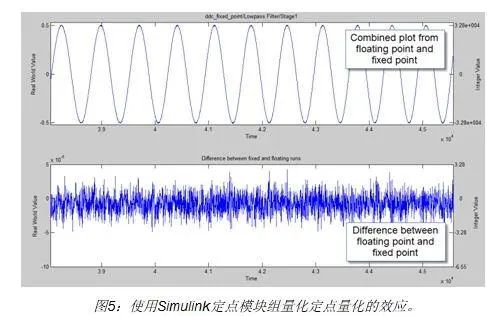

例如,图5展示了DDC滤波器链路中低通滤波器第一阶段浮点与定点仿真结果的差异。这些差异是因定点量化所致。上方图形显示了浮点与定点仿真结果的重叠效果。下方图形显示了图中每一点的量化误差。工程师可能需要根据设计规范来增加小数位数以减小由此引出的量化误差。

除了选择小数位数之外,工程师还需要优化字长,实现低功耗和区域优化的设计。

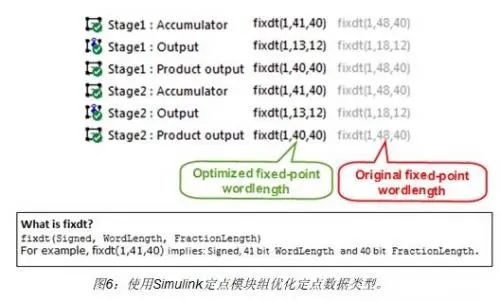

在DDC案例研究中,工程师使用Simulink定点模块组将部分数字滤波器链路的字长减少了8位之多(图6)。

利用自动HDL代码生成功能更快生成FPGA原型

在生成FPGA原型时,HDL代码必不可少。工程师手工编写了Verilog或VHDL代码。作为替代选择,使用HDL编码器自动生成HDL代码具有众 多明显优势。工程师可以快速地评估能否在硬件中实施当前算法;迅速评估不同的算法实现,选择最佳方案;并在FPGA上更快地建立算法原型。

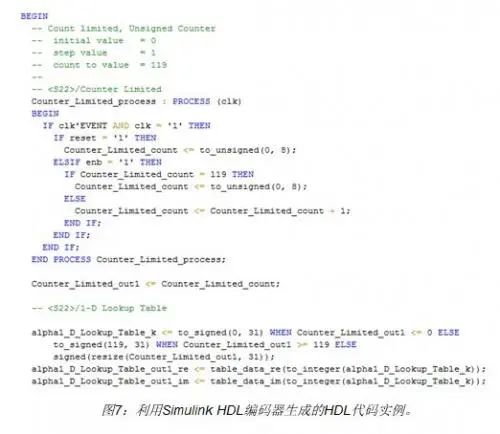

对于DDC案例研究而言,可以在55秒内生成了5780行HDL代码。工程师可以浏览并很快理解代码(图7)。自动代码生成功能允许工程师对系统级模型进行更改,并且,通过重新生成HDL代码,该功能可以在数分钟之内生成更新的HDL实现方案。

重用具有协同仿真功能的系统级测试平台进行HDL验证

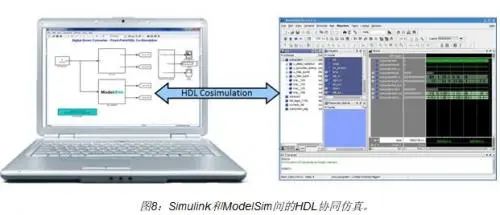

功能验证:HDL协同仿真使工程师能够重用Simulink模型,将激励驱动至HDL仿真器,并对仿真输出执行交互式系统级分析(图8)。

HDL仿真仅提供数字波形输出,而HDL协同仿真则提供了显示HDL代码的完整视图,并可以访问Simulink的全套系统级分析工具。当工程师观察到预期结果与HDL仿真结果存在差异时,可借助协同仿真进一步了解该失配所产生的系统级影响。

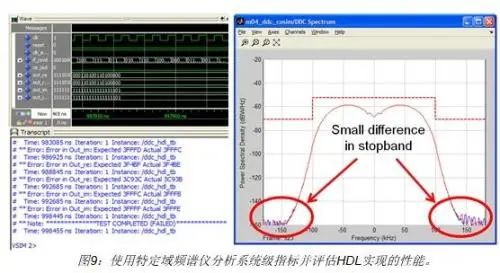

例如,在图9中,频谱仪视图可以使工程师做出明智决定,忽略预期结果与HDL仿真结果之间的失配,其原因是该差异位于阻带区。相比之下,数字波形输出只 是将预期结果与HDL仿真结果的失配标记为误差。尽管工程师最终可能得出相同的结论,但这将需要更多的时间完成所需的分析。

测试覆盖率:工程师可以使用HDL验证工具、Simulink设计验证工具和ModelSim/Questa自动执行代码覆盖率分析。在该工作流程 中,Simulink设计验证工具可针对模型覆盖率生成一套测试用例。HDL验证工具自动使用这一套测试用例运行ModelSim/Questa,收集代 码覆盖率数据,以对生成的代码加以全面分析。

使用FPGA在环仿真加速验证

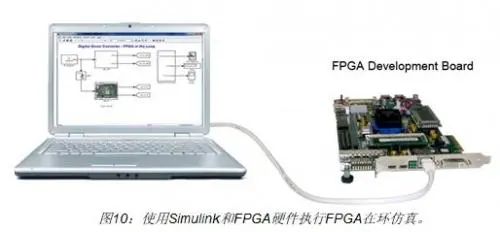

使用系统级仿真和HDL协同仿真验证DDC算法之后,便可以立即在FPGA目标平台上部署DDC算法。对算法执行基于FPGA的验证(也称为FPGA在 环仿真)可以增强对算法在现实环境中有效运行的信心。相比基于主机的HDL仿真,该验证可以使工程师更快地运行测试方案。

对于DDC算法而言,可以使用Simulink模型驱动FPGA输入激励并分析FPGA的输出(图10)。与HDL协同仿真一样,在Simulink中始终可以利用相关数据进行分析。

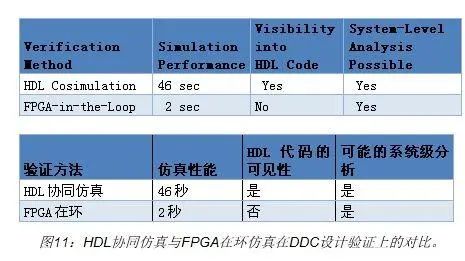

图11对比了HDL协同仿真和FPGA在环仿真这两种用于DDC设计的验证方法。在本案例中,FPGA在环仿真的速度是HDL协同仿真的23倍。这样的 速度提升使工程师能够运行更广泛的测试用例并对其设计进行回归测试。这使他们能够识别出有待进一步分析的潜在问题区域。

尽管HDL协同仿真速度较慢,但它却提高了HDL代码的可见性。因此,它很适合针对FPGA在环仿真过程中发现的问题区域进行更详细的分析。

本文小结

如果工程师遵循本文所述的四种最佳方法,开发FPGA原型将比传统的手动工作流程快出许多,并能使工程师信心倍增。此外,工程师还可以在整个开发过程中 继续优化自己的模型,并快速地重新生成有关FPGA实现的代码。与依赖手工编写HDL的传统工作流程相比,这种能力可以显着缩短设计迭代的周期。

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22508浏览量

639450 -

matlab

+关注

关注

189文章

3029浏览量

239250 -

算法

+关注

关注

23文章

4810浏览量

98600 -

RTL

+关注

关注

1文章

395浏览量

62899 -

Simulink

+关注

关注

23文章

552浏览量

66473

原文标题:在FPGA上建立MATLAB和Simulink算法原型

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

使用MATLAB Simulink和HDL编码器创建自定义IP--AWB

基于MATLAB/Simulink的系统仿真技术与应用

MATLAB和Simulink算法原型如何在FPGA上适配?

如何在FPGA上建立MATLAB和Simulink算法原型?

在FPGA上建立MATLAB和Simulink算法原型的四种最佳方法

浅析MATLAB和Simulink嵌入式视觉应用

使用USRP E310和MATLAB和Simulink进行原型设计和测试软件定义的无线电

Matlab/simulink在FPGA设计中的应用

VB和Matlab/Simulink的接口方法

simulink__matlab教程

关于使用 MATLAB 进行无线通信设计的相关分析和介绍

使用MATLAB和Simulink的建模与仿真详细课件免费下载

在FPGA上部署5G NR无线通信:MATLAB与Simulink工作流程

使用MATLAB和Simulink创建FPGA原型的最佳方法

使用MATLAB和Simulink创建FPGA原型的最佳方法

评论