要为 Versal 的多个 Quad 创建收发器设置,建议从 Transceiver Bridge IP 开始,在其中选择所需的设置,然后交由 Vivado 通过块自动化设置来为此设置创建必要的 Quad。

Bridge IP 仅支持单一设置。以下展示了关于同一个收发器内为 TX 和 RX 采用不同的设置的具体方法示例。其中部分示例支持块自动化设置,但部分示例则需要适当的手动调整。

示例 1

单 RX 核与单 TX 核,各含 8 条通道,置于两个 Quad 内

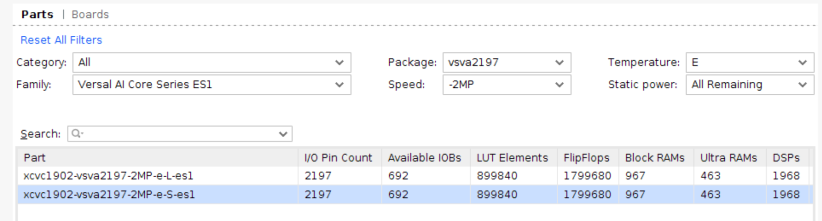

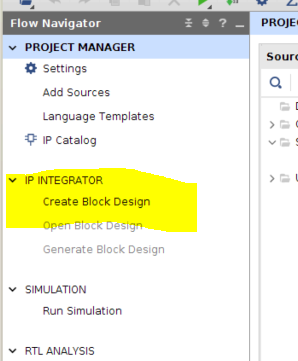

首先,为 Versal 器件创建一个工程,并打开块设计:

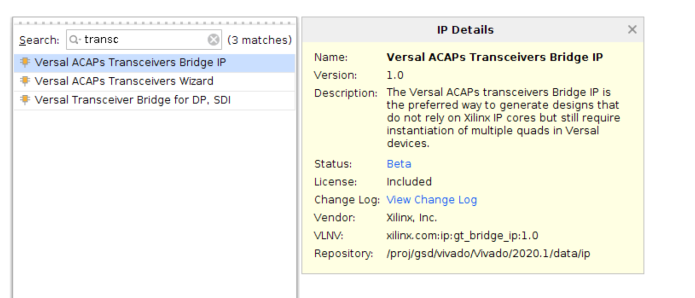

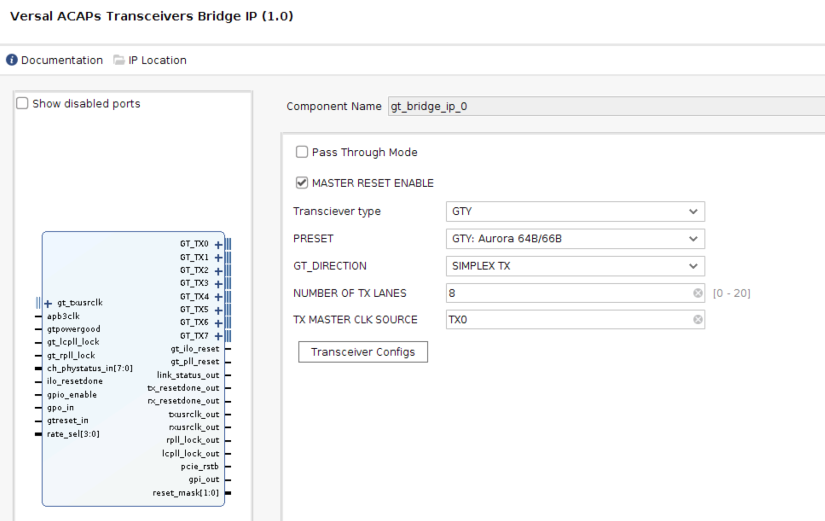

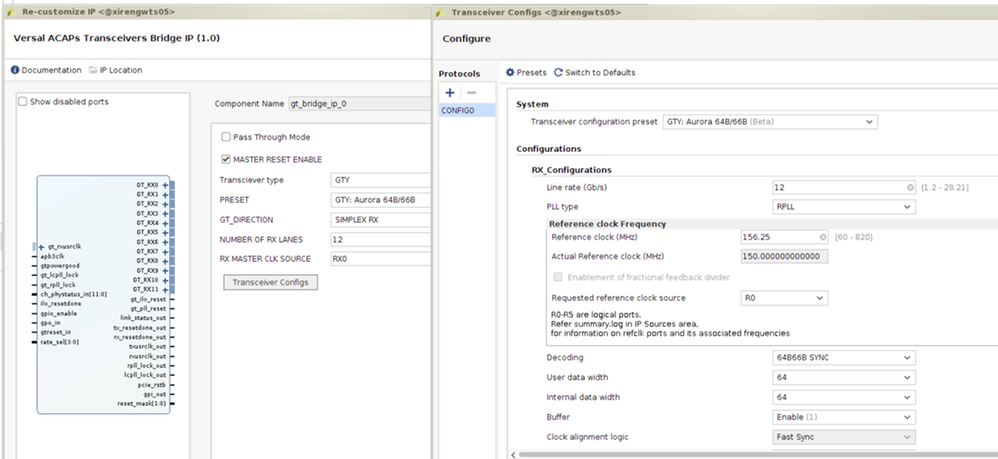

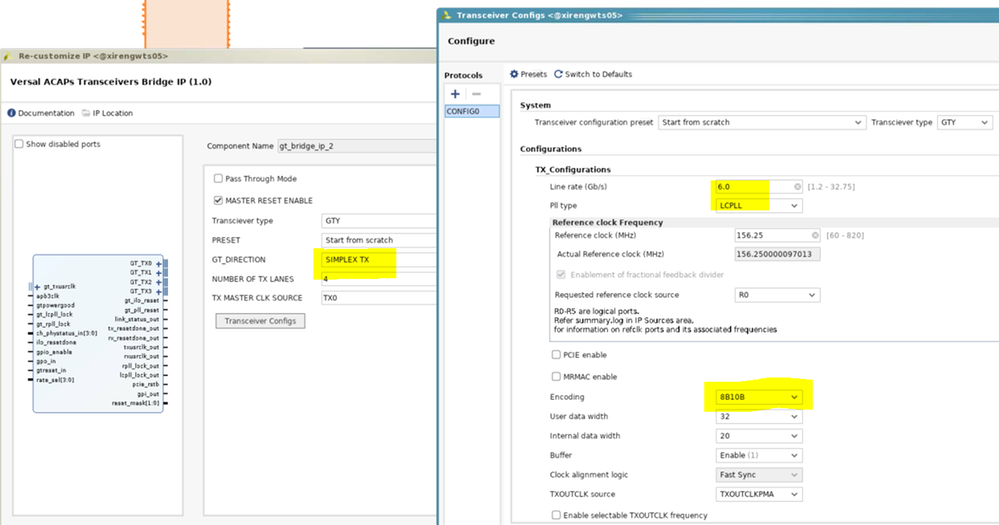

在此块设计中添加一个 Transceivers Bridge IP,并对其进行配置:

此处选择的是 Aurora 模板,针对这 8 条通道选中了 Simplex TX。

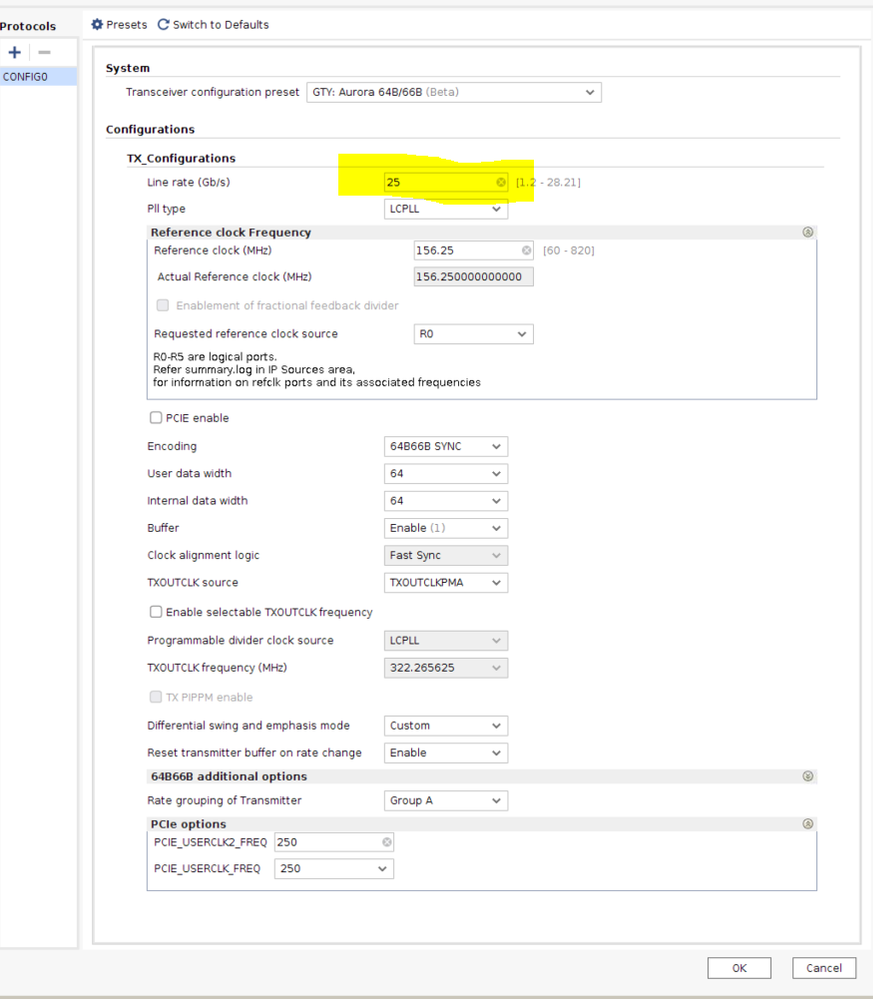

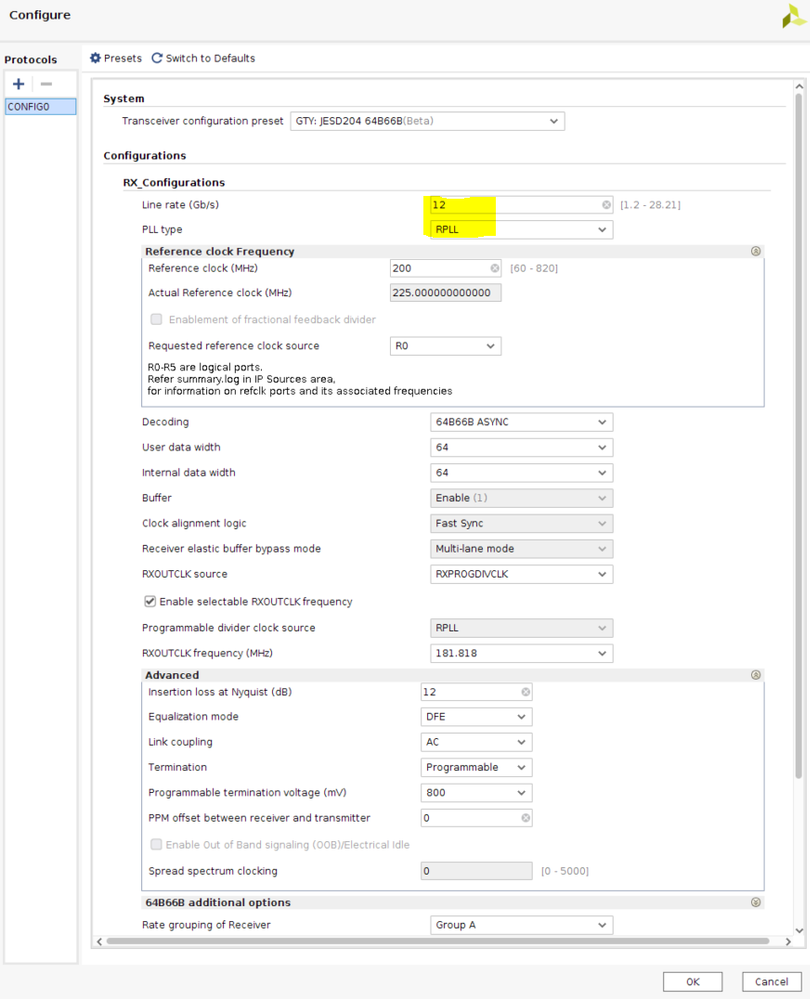

随后进入“Transceiver Configs”(收发器配置),选择要使用的线速率和 PLL:

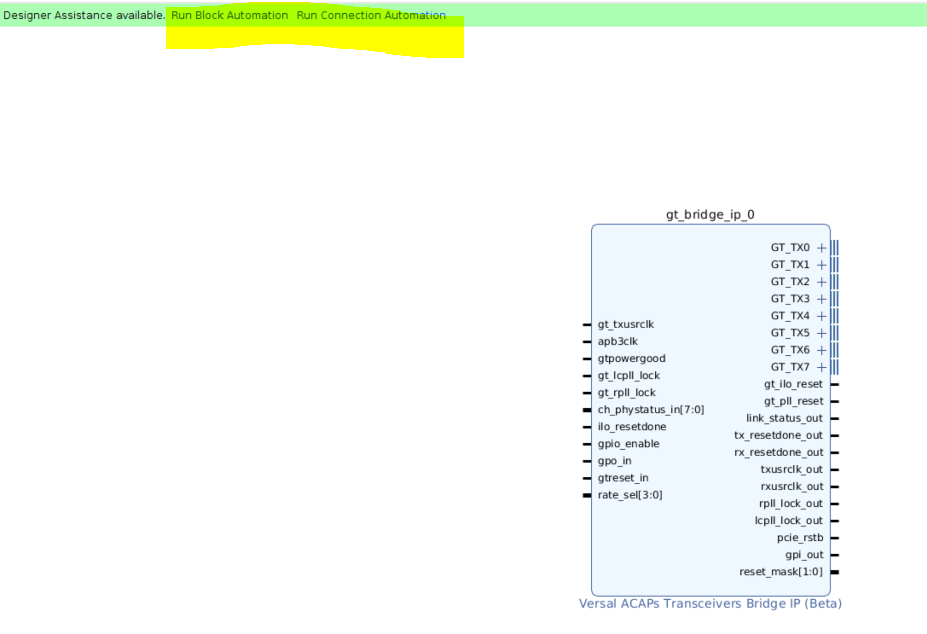

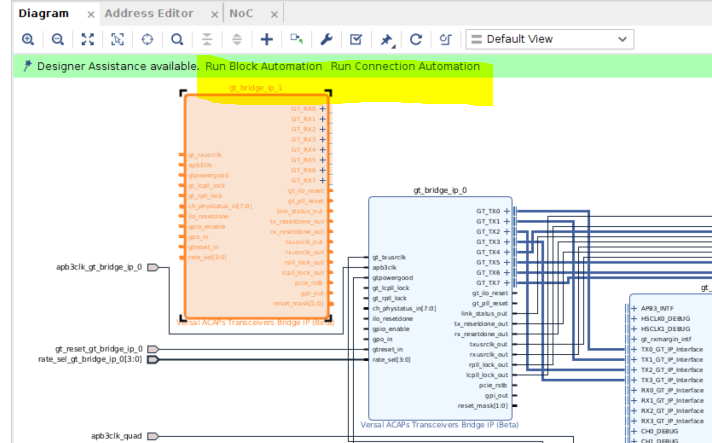

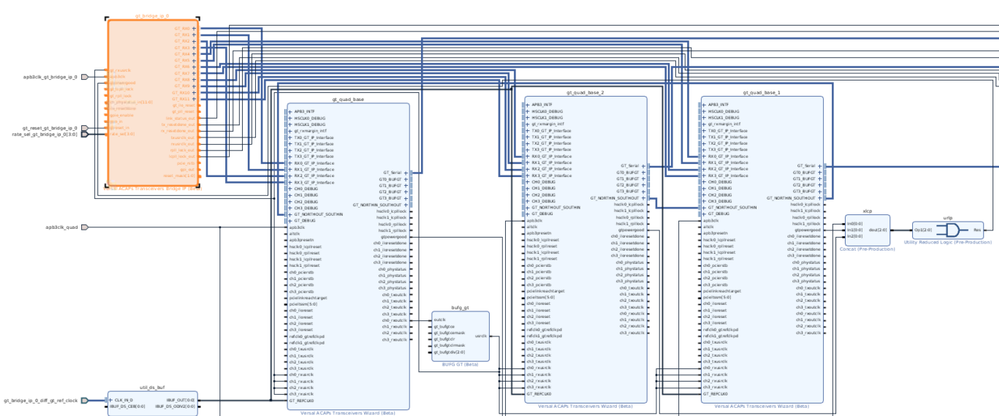

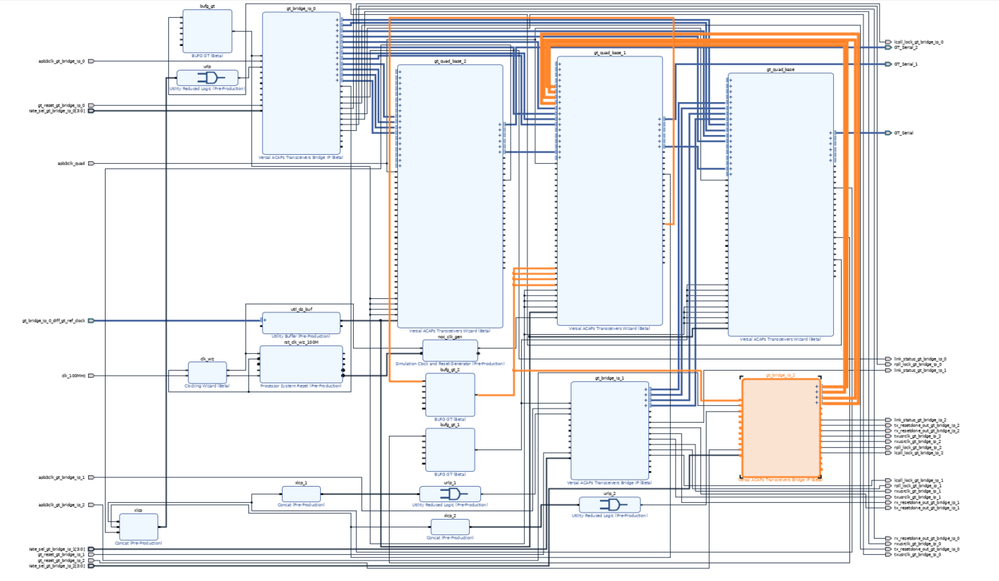

然后,为此 Transceivers Bridge IP 运行“Block Automation”(块自动化设置):

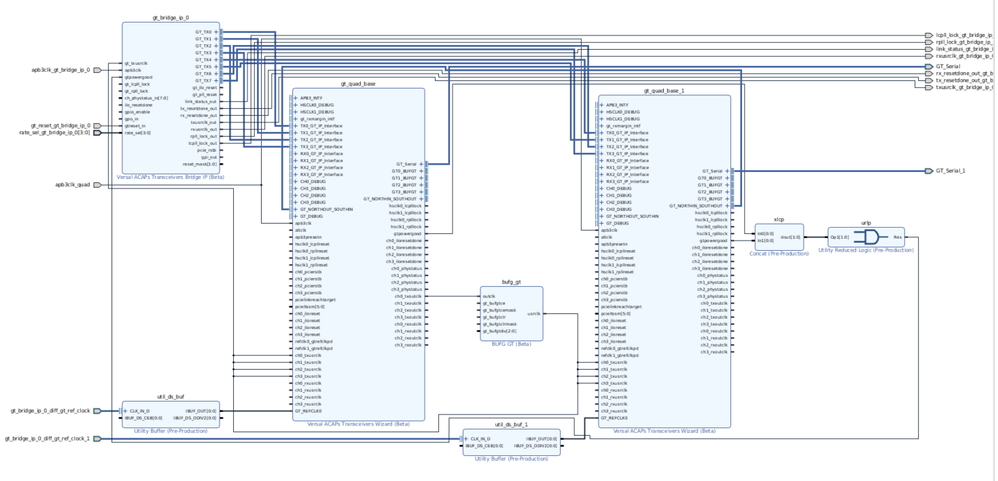

这样即可得到适用于该核的设置:

现在,添加另一个 Transceivers Bridge IP。

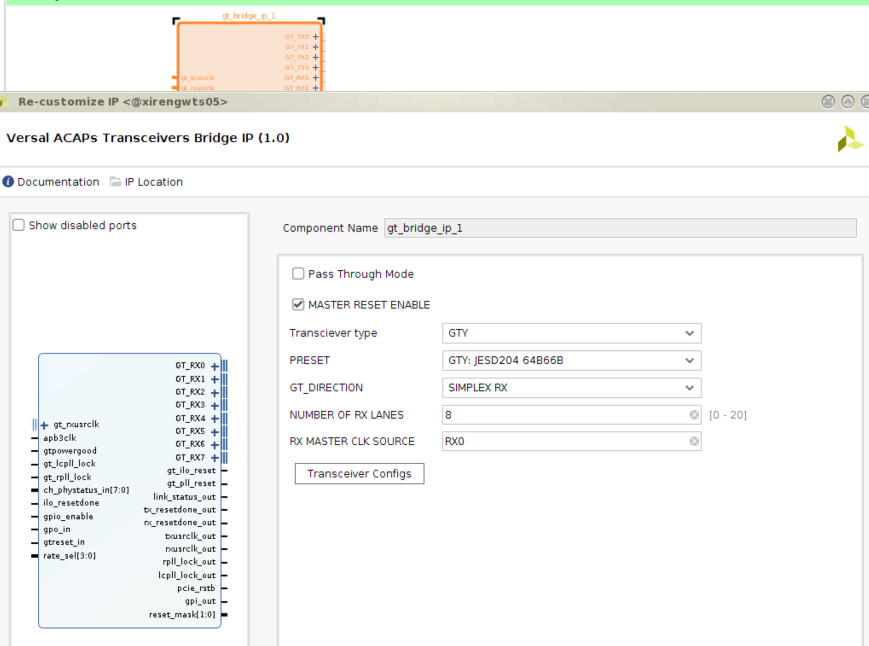

此处选择的是“JESD204 64B66B”,针对 8 条通道选中 Simplex RX:

可以看到,此 RX 设置所选的线速率和 PLL 与前者不同。

为此新 Transceivers Bridge IP 运行块自动化设置:

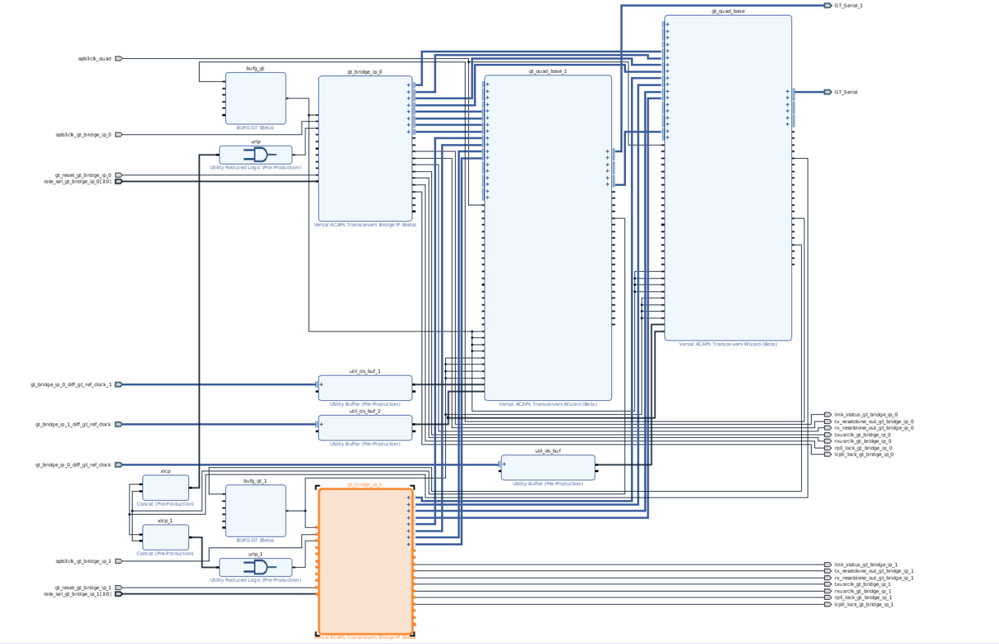

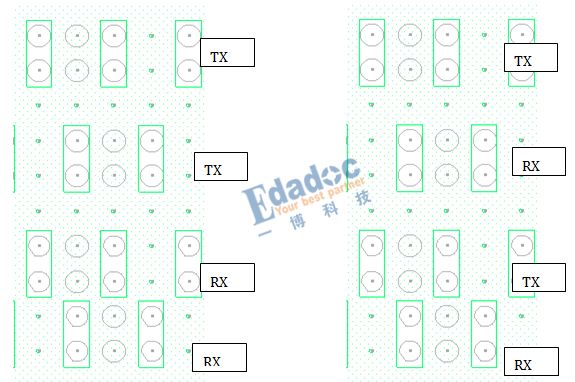

现在可看到,两个 Transceivers Bridge IP 均已连接到以上相同的 Quad IP。

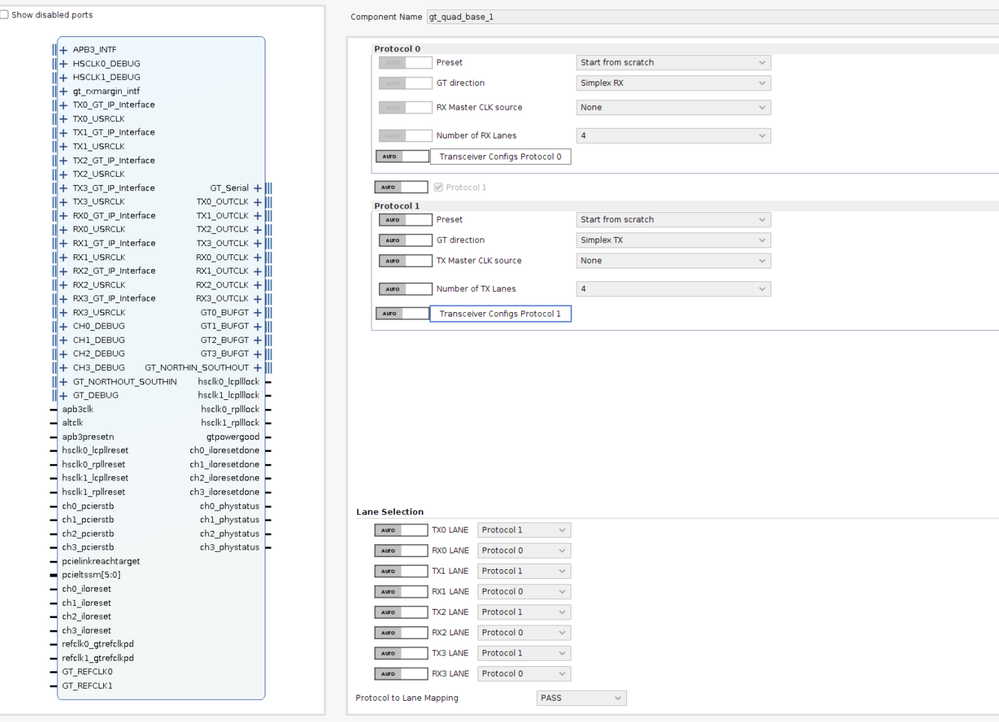

查看 Transceiver Quad IP 可以发现,两个单工设置的协议均已同步到 Quad IP。至此,此示例已完成。下一步,只需照常为 Quad 设置位置即可。

示例 2

单 RX 核与三 TX 核(共含 12 条通道,置于三个 Quad 内)

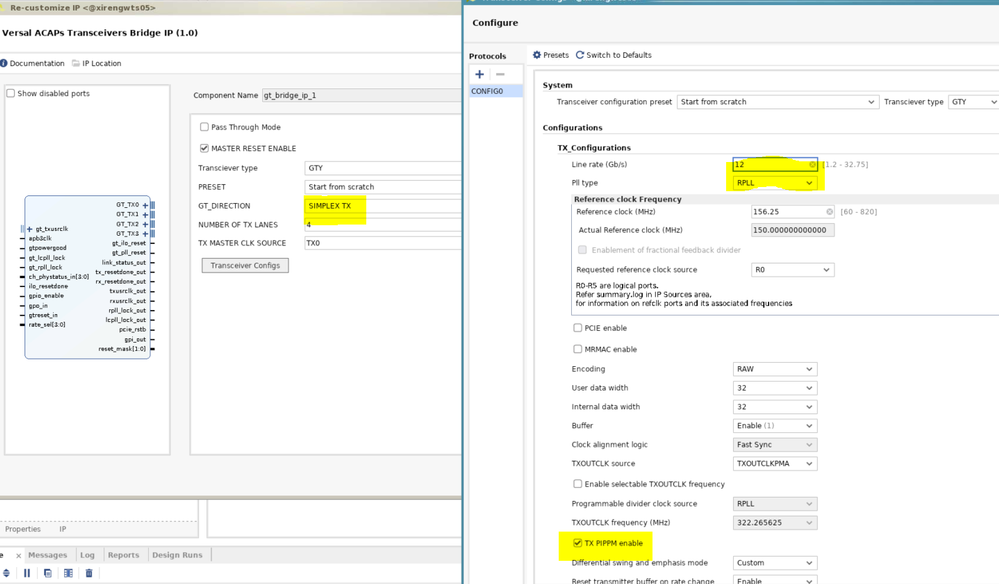

此设置将采用单个含 12 条通道的 Aurora RX 核(12Gbps 和 RPLL)和 3 TX 核(各含 4 条通道)。

一个 TX 核采用默认原始设置,含 12Gbps 和 TXPI 控制。

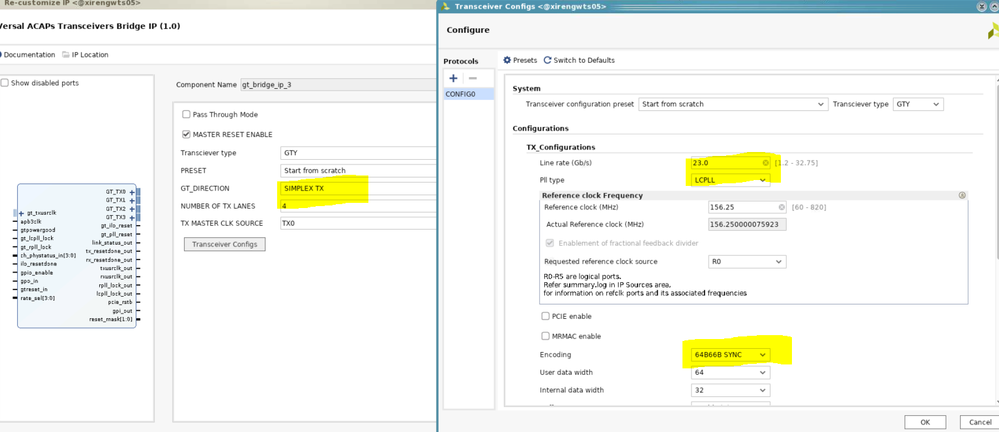

一个 TX 核采用 8B10B 编码和 6Gbps。

一个 TX 核采用 23Gbps 和 64B66B 编码(同步变速箱)。

创建工程和块设计后,首先请为 12 条通道创建一个 RX 核,配置为 Aurora 64B66B 并使用 RPLL:

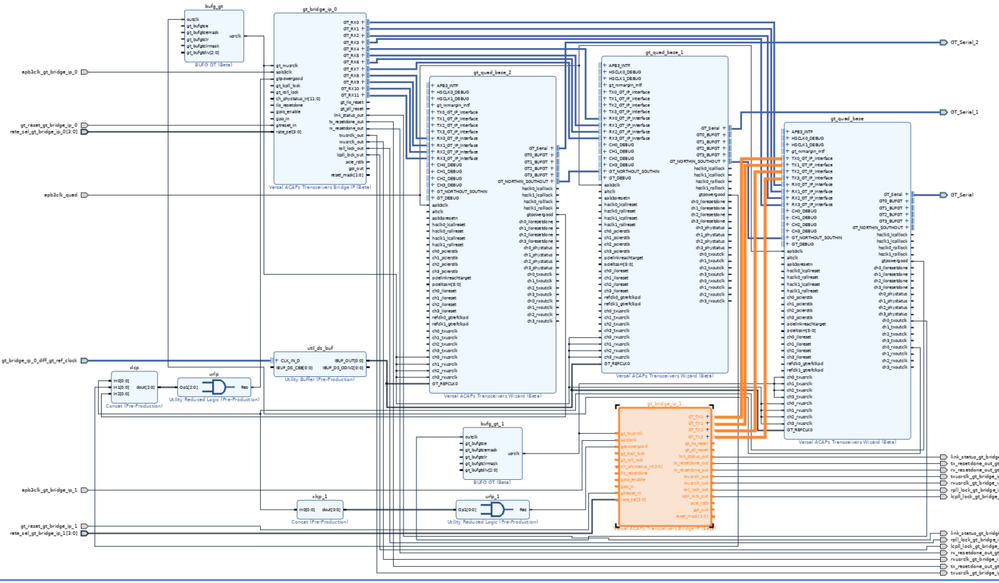

接下来,运行块自动化设置:

在此可以看到含 3 个 Quad IP 的 RX bridge IP。

创建首个 TX 核,如下所示:

运行块自动化设置,这样即可看到:

此 TX 核连接到其中一个 Quad IP。

如果要使用另一个 Quad 的各条通道,则需要手动更改到另一个四通道的连接(已高亮)以及时钟信号和控制信号。

此外还需要在这些 Quad 之间移植 TX 协议。目前暂时无需执行这些操作。

添加第二个 TX 核:

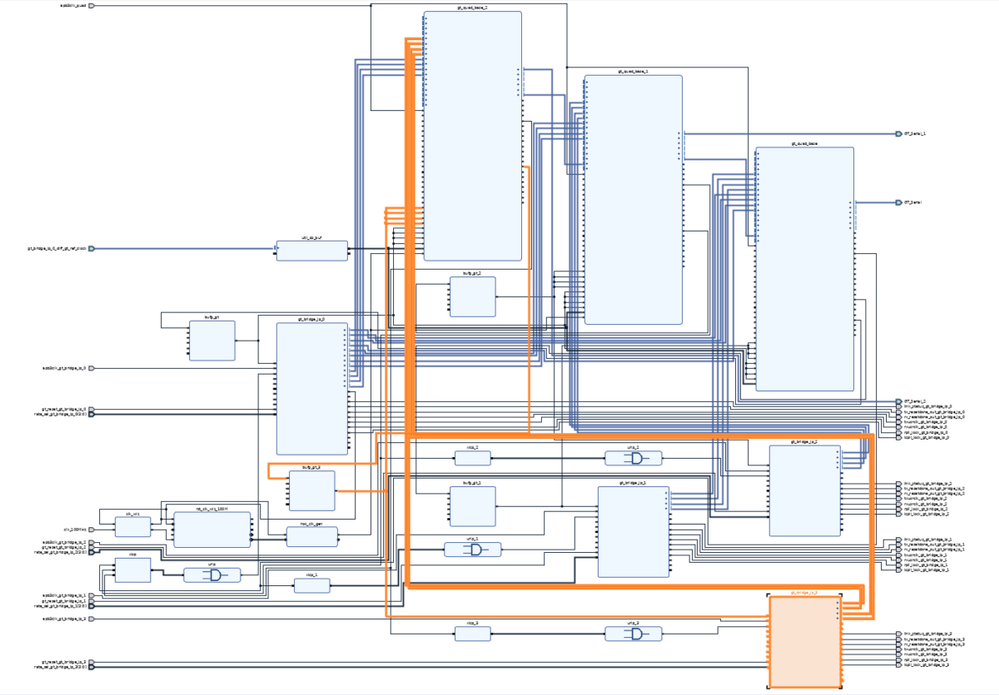

通过执行块自动化设置和自动连接,可得到如下结果:

可看到,块自动化设置会选择下一个 Quad 以连接 4 条通道。

同样,如果希望使用另一个 Quad,需要手动更改连接和协议。

添加第三个 TX 核:

运行块自动化设置和自动连接:

同上,块自动化设置使用可用的 Quad 来连接 TX 通道。

现在,可确认 BD 并通过设置位置约束来照常实现此设计。

审核编辑:汤梓红

-

收发器

+关注

关注

10文章

3836浏览量

111442 -

Xilinx

+关注

关注

73文章

2205浏览量

131834 -

Quad

+关注

关注

0文章

11浏览量

7932 -

集成器

+关注

关注

1文章

7浏览量

2306 -

Versal

+关注

关注

1文章

176浏览量

8535

原文标题:开发者分享|Versal GTY - 如何在 IP 集成器中将单工 TX / RX 核合并到多个 Quad

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何在未使用的QUAD和部分使用的QUAD中连接RX,TX,MGTREFCLK?

Gowin DVI TX RX IP快速用户指南

如何将SAI RX同步到TX?

Northwest Logic支持Xilinx IP集成器工具流

如何在EDK中使用自己的 IP核?

Xilinx的HDMI 1.4Tx/Rx和HDMI 2.0Tx/Rx的IP内核介绍

Gowin DVI TX RX IP用户指南

Gowin LVDS 7to1 TX RX IP用户指南

IP_数据表(I-27):MIPI D-PHY Tx/Rx for TSMC 40nm LP

IP_数据表(I-28):MIPI D-PHY Tx/Rx for Samsung 28nm

如何在IP集成器中将单工TX/RX核合并到多个Quad

如何在IP集成器中将单工TX/RX核合并到多个Quad

评论