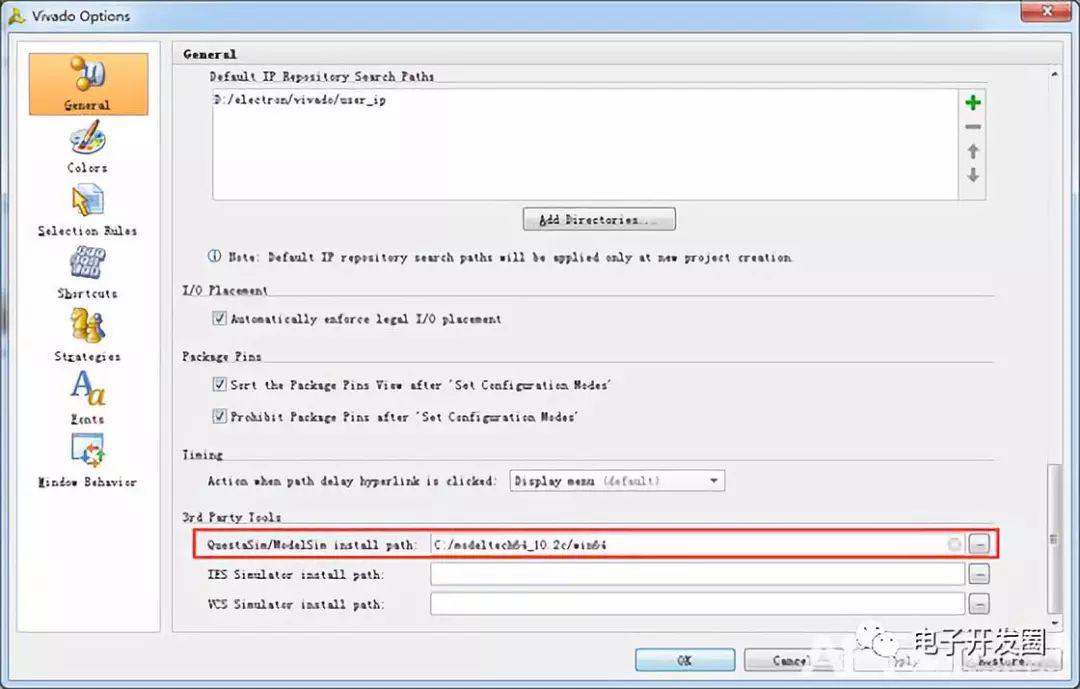

一、在vivado中设置modelsim(即第三方仿真工具)的安装路径。在vivado菜单中选择“Tools”——》“Options.。。”,选择“General”选项卡,将滚动条拉倒最底部,在“QuestaSim/ModelSim install path”栏中输入或选择modelsim工具的安装路径,如图1所示。

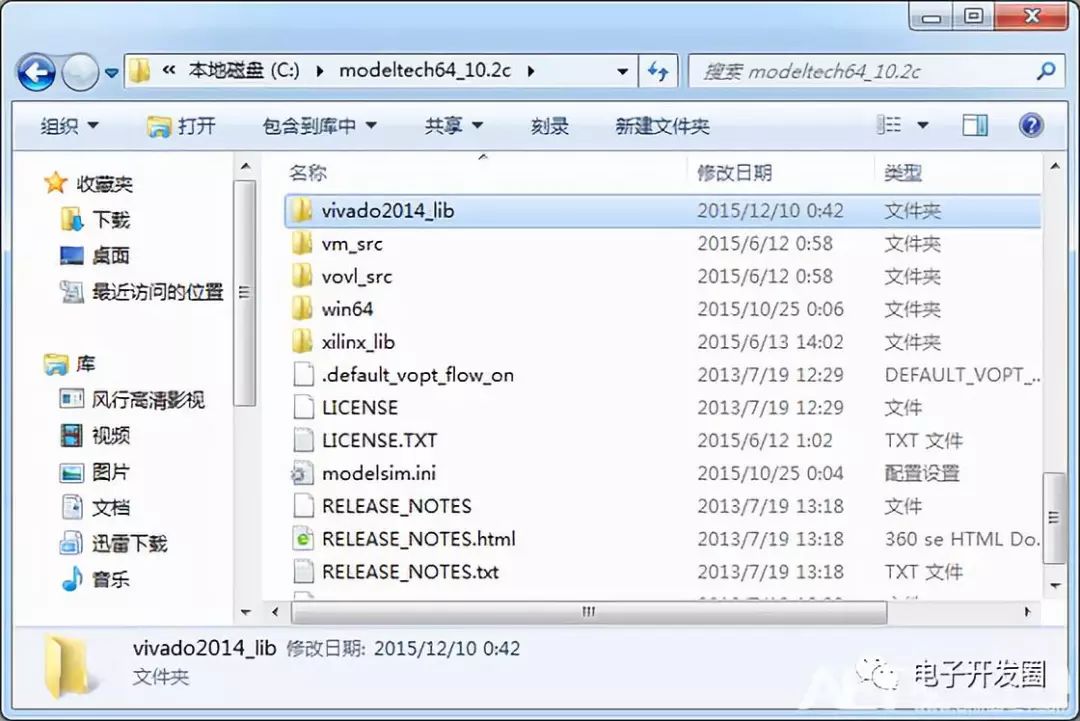

图1 设置modelsim的安装路径 二、器件库编译。首先,在modelsim安装路径中新建一个名为vivado2014_lib的文件夹(路径和文件名可改),如图2所示。

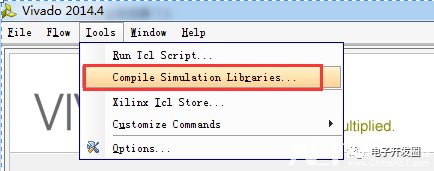

图2 在modelsim安装路径下新建vivado2014_lib文件夹 接着选择vivado菜单“Tools”——》“Compile Simulation Libraries.。。”命令,如图3所示。

图3 选择“Compile Simulation Libraries.。。”命令

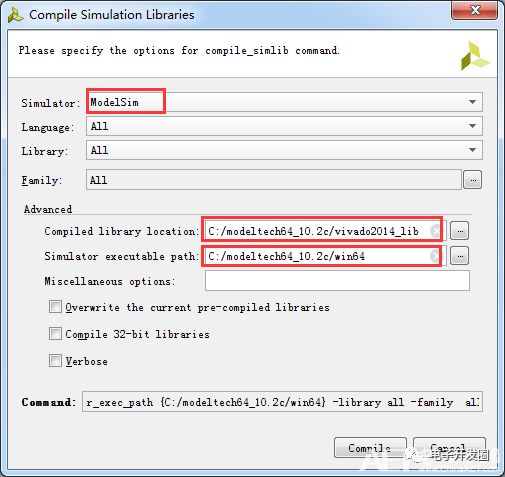

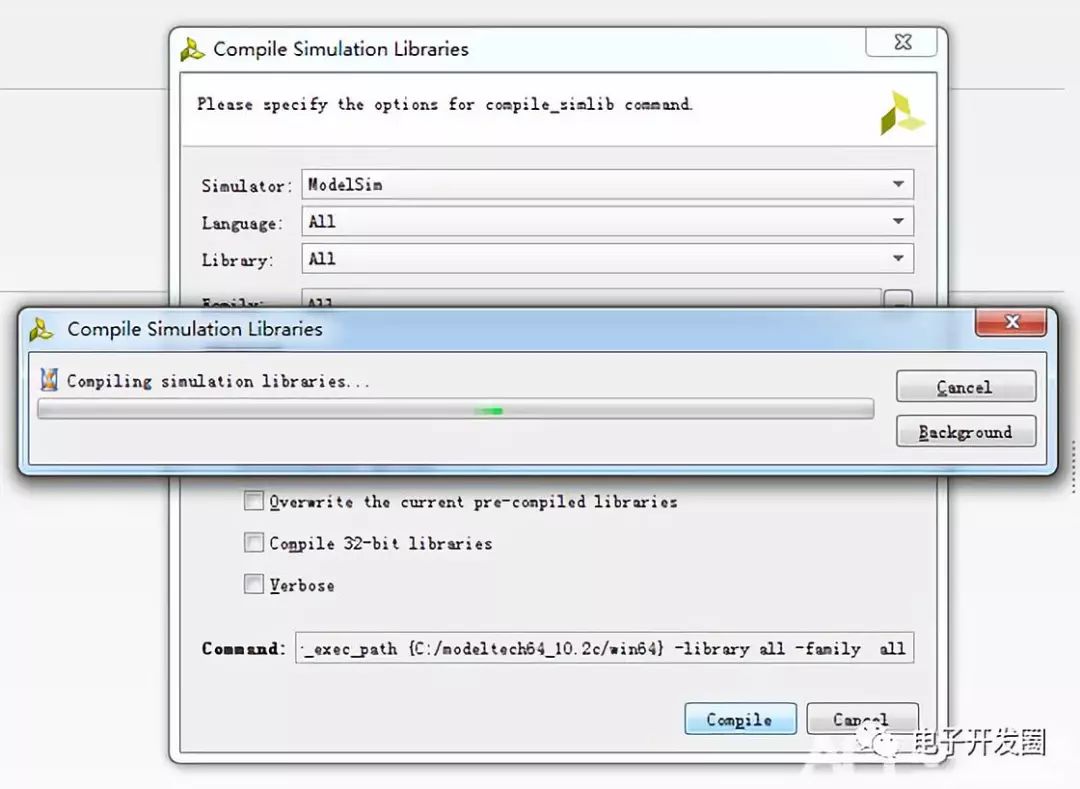

在弹出的对话框中设置器件库编译参数,仿真工具“Simulator”选为ModelSim,语言“Language”、库“Library”、器件家族“Family”都为默认设置All(当然也可以根据自己的需求进行设置),然后在“Compiled library location”栏设置编译器件库的路径,这里选前面新建的vivado2014_lib文件夹,此外在“Simulator executable path”栏设置modelsim执行文件的路径,其他参数默认,如图4所示。

图4 设置器件库编译参数

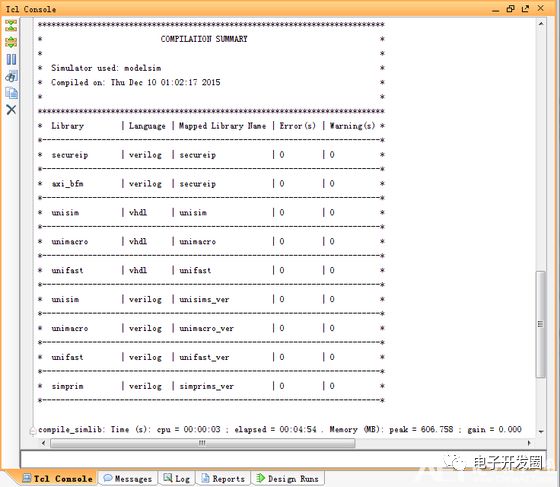

设置好参数后点击“Compile”按钮开始器件库的编译。图5所示为正在编译器件库的过程中。器件库编译结束后给出编译报告,从报告中看出0个警告和0个错误,如图6所示。

图5 正在编译器件库的过程中

图6 器件库

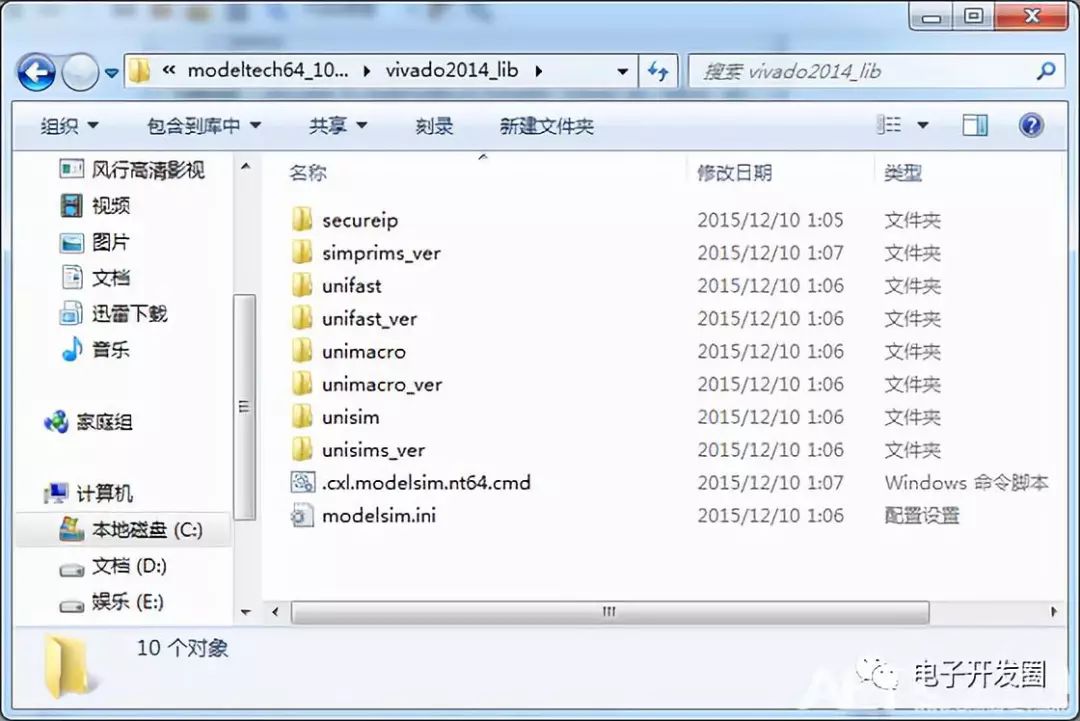

编译结束后产生编译报告 打开modelsim安装路径下的vivado2014_lib文件夹,便可以看到已经产生了器件库,如图7所示。

图7 已在vivado2014_lib文件夹中生成器件库

三、在vivado中关联了modelsim软件和编译器件库之后,就可以在vivado中调用modelsim软件对设计进行仿真了。

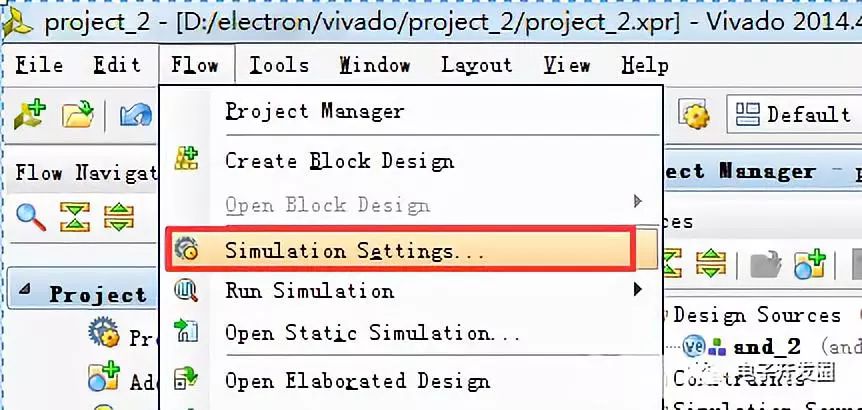

不过,在对每一个新建的工程设计进行仿真时需要进行一些设置。选择vivado菜单“Flow”——》“Simulation Settings.。。”命令或点击流程向导中选择“Simulation Settings.。。”命令,分别如图8和图9所示。

图8 从菜单选择“Simulation Settings.。。”命令

图9 从流程向导中选择“Simulation Settings.。。”命令

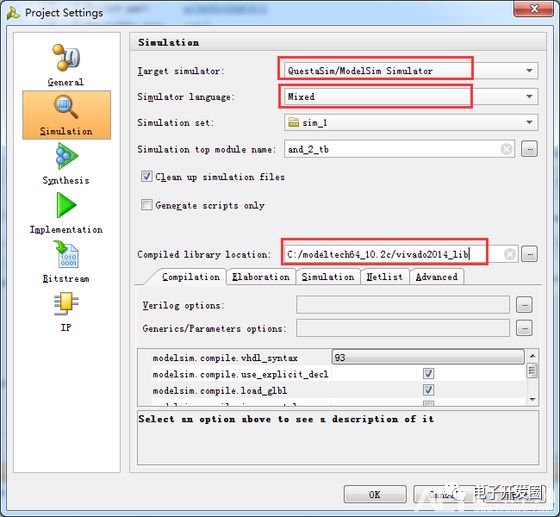

在弹出的对话框中,设置仿真工具为modelsim、仿真语言为verilog或VHDL或混合,当设计中用到vivado中自带的仿真工具时,还要指定器件库的路径,如图10所示。关于仿真的其他参数在这里就不作介绍了。

图10 设置仿真参数

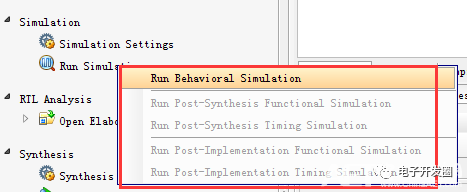

设置好仿真参数后,如果设计文件和仿真文件也准备好,那么就可以开始对设计的功能进行仿真了。选择菜单“Flow”——》“Run Simulation”——》选相应的仿真类型或点击流程向导中的“Run Simulation”——》选相应的仿真类型进行仿真,如图11所示。

图11 选择相应的仿真类型进行仿真

编辑:lyn

-

ModelSim

+关注

关注

5文章

174浏览量

48882 -

Vivado

+关注

关注

19文章

846浏览量

70474

原文标题:Vivado与Modelsim关联方法及器件库编译

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【产品介绍】Modelsim:HDL语言仿真软件

使用Vivado 2018.2编译E203的mcs文件,遇到的问题求解

Vivado仿真之后没有出现仿真结果的解决方法

Windows系统下用vivado将电路烧写到MCU200T板载FLASH的方法

vcs和vivado联合仿真

如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

商品视频关联接口技术详解

如何应对负载的关联性和动态变化?

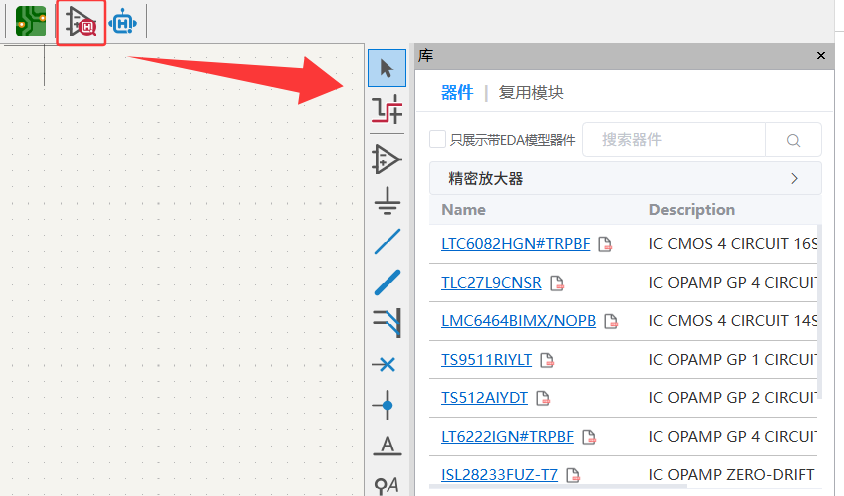

在KiCad华秋发行版中使用云端器件库

Vivado无法选中开发板的常见原因及解决方法

AMD Vivado Design Suite 2025.1现已推出

一文详解Vivado时序约束

详解Vivado与Modelsim关联方法及器件库编译

详解Vivado与Modelsim关联方法及器件库编译

评论