声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4415文章

23955浏览量

426011 -

设计

+关注

关注

4文章

828浏览量

71484 -

PADS

+关注

关注

83文章

821浏览量

111738

发布评论请先 登录

相关推荐

热点推荐

11:如何在 Allegro 中添加自定义的测试点 I Allegro PCB 设计小诀窍

背景介绍: 为了对加工后的PCB性能进行测试,我们在进行PCB设计时,通常会在PCB上一些关键位置添加测试点,Allegro

发表于 04-16 17:07

08. 如何在 Allegro中设置禁止添加测试点区域?| 芯巧Allegro PCB 设计小诀窍

背景介绍: 我们在进行PCB设计时,为了方便对加工后的PCB进行测试,通常会为关键性元件添加测试点,但是在

发表于 04-10 10:56

芯片测试覆盖率99%就够了吗?给DFT设计提个醒

充分。必须将硅后验证向量导入ATPG工具进行覆盖率分析,否则会形成测试盲区。

二、从测试困境到DFT设计反馈

测试工程师的挑战应前置于设计阶段解决。

发表于 02-06 11:06

【「龙芯之光 自主可控处理器设计解析」阅读体验】+可测试性设计章节阅读与自己的一些感想

,也分享下 自己的一些感想。 先介绍了两个术语DFT可测试性 设计,ATE自动测试设备,DFT目

发表于 01-15 23:30

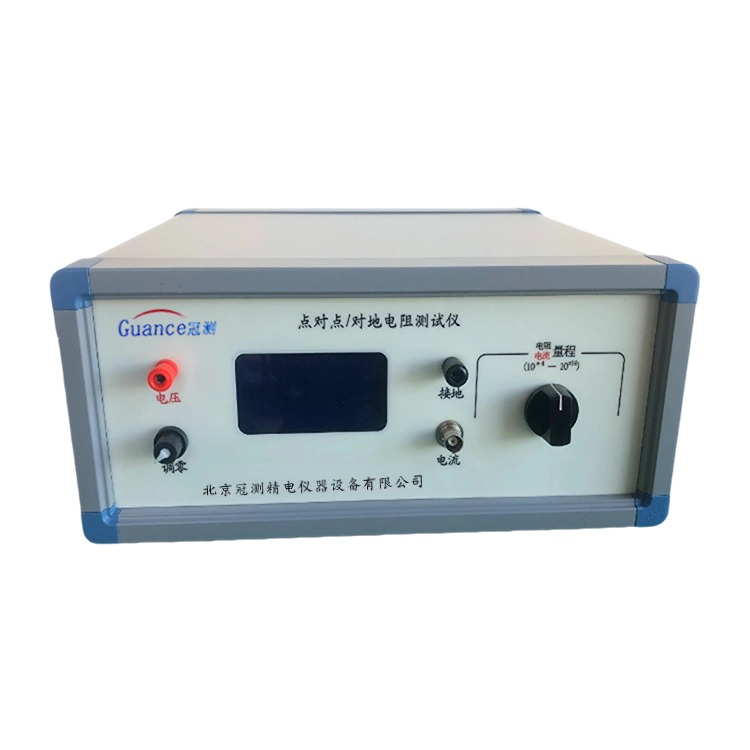

测试点氧化或污浊时的应急技巧:点对点对地电阻测试如何获得真实数据

在点对点对地电阻测试中,测试点的氧化、生锈或附着油污、灰尘等污浊物,会在接触表面形成额外电阻层,导致测试数据虚高或波动频繁,难以反映真实的接地电阻状态。面对这类突发情况,无需依赖专业清洁设备,通过

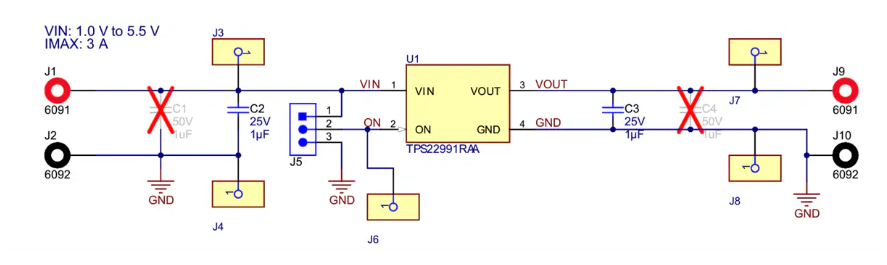

Texas Instruments TPS22991EVM评估模块数据手册

进出被测器件的低电阻路径。测试点连接使用户能够利用用户定义的测试条件控制TI TPS22991EVM和进行精确的R~ON~ 测量。

高压继电器如何提升安规与线缆测试的效率和安全性?

一过程中扮演着至关重要的角色。在多点高压扫描测试中,高压继电器的快速切换能力能够实现不同测试点之间的快速切换,提高测试效率。高压继电器在线缆测试中的应用线缆

标准电阻器不接PCB的地,电阻测量结果就波动大

标准电阻器不接PCB的地,电阻测量结果就波动大,需要电阻箱上面的接地和PCB接地测试点连一起,这个是因为什么,是因为PCB接地不能用测试点裸

发表于 06-17 13:08

借助DFT技术实现竞争力最大化

通过改进和优化设计与制造的各个方面,半导体行业已经能够实现 IC 能力的巨大进步。可测试性设计 (DFT)——涵盖从在 RTL 中插入

利用PADS可测试性设计优化PCB测试点和DFT审核

利用PADS可测试性设计优化PCB测试点和DFT审核

评论