砷化镓GaAs

半导体材料可以分为元素半导体和化合物半导体两大类,元素半导体指硅、锗单一元素形成的半导体,化合物指砷化镓、磷化铟等化合物形成的半导体。砷化镓的电子迁移速率比硅高5.7倍,非常适合用于高频电路。砷化镓组件在高频、高功率、高效率、低噪声指数的电气特性均远超过硅组件,空乏型砷化镓场效晶体管(MESFET)或高电子迁移率晶体管(HEMT/PHEMT),在3V电压操作下可以有80%的功率增加效率(PAE:poweraddedefficiency),非常的适用于高层(hightier)的无线通讯中长距离、长通信时间的需求。

砷化镓元件因电子迁移率比硅高很多,因此采用特殊的工艺,早期为MESFET金属半导体场效应晶体管,后演变为HEMT(高速电子迁移率晶体管),pHEMT(介面应变式高电子迁移电晶体)目前则为HBT(异质接面双载子晶体管)。异质双极晶体管(HBT)是无需负电源的砷化镓组件,其功率密度(powerdensity)、电流推动能力(currentdrivecapability)与线性度(linearity)均超过FET,适合设计高功率、高效率、高线性度的微波放大器,HBT为最佳组件的选择。而HBT组件在相位噪声,高gm、高功率密度、崩溃电压与线性度上占优势,另外它可以单电源操作,因而简化电路设计及次系统实现的难度,十分适合于射频及中频收发模块的研制,特别是微波信号源与高线性放大器等电路。

砷化镓生产方式和传统的硅晶圆生产方式大不相同,砷化镓需要采用磊晶技术制造,这种磊晶圆的直径通常为4-6英寸,比硅晶圆的12英寸要小得多。磊晶圆需要特殊的机台,同时砷化镓原材料成本高出硅很多,最终导致砷化镓成品IC成本比较高。磊晶目前有两种,一种是化学的MOCVD,一种是物理的MBE。

SiGe

1980年代IBM为改进Si材料而加入Ge,以便增加电子流的速度,减少耗能及改进功能,却意外成功的结合了Si与Ge。而自98年IBM宣布SiGe迈入量产化阶段后,近两、三年来,SiGe已成了最被重视的无线通信IC制程技术之一。

依材料特性来看,SiGe高频特性良好,材料安全性佳,导热性好,而且制程成熟、整合度高,具成本较低之优势,换言之,SiGe不但可以直接利用半导体现有200mm晶圆制程,达到高集成度,据以创造经济规模,还有媲美GaAs的高速特性。随着近来IDM大厂的投入,SiGe技术已逐步在截止频率(fT)与击穿电压(Breakdownvoltage)过低等问题获得改善而日趋实用。

目前,这项由IBM所开发出来的制程技术已整合了高效能的SiGeHBT(HeterojunctionBipolarTransistor)3.3V及0.5μm的CMOS技术,可以利用主动或被动组件,从事模拟、RF及混合信号方面的配置应用。

SiGe既拥有硅工艺的集成度、良率和成本优势,又具备第3到第5类半导体(如砷化镓(GaAs)和磷化铟(InP))在速度方面的优点。只要增加金属和介质叠层来降低寄生电容和电感,就可以采用SiGe半导体技术集成高质量无源部件。此外,通过控制锗掺杂还可设计器件随温度的行为变化。SiGeBiCMOS工艺技术几乎与硅半导体超大规模集成电路(VLSI)行业中的所有新技术兼容,包括绝缘体硅(SOI)技术和沟道隔离技术。

不过硅锗要想取代砷化镓的地位还需要继续在击穿电压、截止频率、功率消耗方面努力。

RF CMOS

RF CMOS工艺可分为两大类:体硅工艺和SOI(绝缘体上硅)工艺。由于体硅CMOS在源和漏至衬底间存在二极管效应,造成种种弊端,多数专家认为采用这种工艺不可能制作高功率高线性度开关。与体硅不同,采用SOI工艺制作的RF开关,可将多个FET串联来对付高电压,就象GAAS开关一样。

尽管纯硅的CMOS制程被认为仅适用于数字功能需求较多的设计,而不适用于以模拟电路为主的射频IC设计,不过历经十几年的努力后,随着CMOS性能的提升、晶圆代工厂在0.25mm以下制程技术的配合、以及无线通信芯片整合趋势的引领下,RFCMOS制程不仅是学界研究的热门课题,也引起了业界的关注。采用RFCMOS制程最大的好处,当然是可以将射频、基频与存储器等组件合而为一的高整合度,并同时降低组件成本。但是症结点仍在于RFCMOS是否能解决高噪声、低绝缘度与Q值、与降低改善性能所增加制程成本等问题,才能满足无线通信射频电路严格的要求。

目前已采用RFCMOS制作射频IC的产品多以对射频规格要求较为宽松的Bluetooth与WLAN射频IC,例如CSR、Oki、Broadcom等Bluetooth芯片厂商皆已推出使用CMOS制造的Bluetooth传送器;英特尔公司宣布已开发出能够支持当前所有Wi-Fi标准(802.11a、b和g)并符合802.11n预期要求的全CMOS工艺直接转换双频无线收发信机原型,包括了5GHz的PA,并轻松实现了发送器与接收器功能的分离。而Atheros、Envara等WLAN芯片厂商也在最近推出全CMOS制程的多模WLAN(.11b/g/a)射频芯片组。

手机用射频IC规格非常严格,但是坚冰已经被打破。SiliconLabs最先以数字技术来强化低中频至基频滤波器及数字频道选择滤波器功能,以降低CMOS噪声过高的问题所生产的Aero低中频GSM/GPRS芯片组,英飞凌立刻跟进,也大量推出RFCMOS工艺的产品,而高通在收购Berkana后,也大力采用RFCMOS工艺,一批新进射频厂家无一例外都采用RFCMOS工艺,甚至是最先进的65纳米RFCMOS工艺。老牌的飞利浦、FREESCALE、意法半导体和瑞萨仍然坚持用传统工艺,主要是SiGeBiCMOS工艺,诺基亚仍然大量使用意法半导体的射频收发器。而欧美厂家对新产品一向保守,对RFCMOS缺乏信任,但是韩国大厂三星和LG还有中国厂家夏新和联想,在成本压力下,大量采用RFCMOS工艺的收发器。目前来看,缺点可能是故障率稍高和耗电稍大,并且需要多块芯片,增加设计复杂程度。但仍在可忍受的范围内。

其他应用领域还包括汽车的安全雷达系统,包括用于探测盲区的24GHz雷达以及用于提供碰撞警告或先进巡航控制的77GHz雷达;IBM在此领域具备领导地位,2005年推出的第四代SIGE线宽有0.13微米。

Ultra CMOS

SOI的一个特殊子集是蓝宝石上硅工艺,在该行业中通常称为Ultra CMOS。蓝宝石本质上是一种理想的绝缘体,衬底下的寄生电容的插入损耗高、隔离度低。Ultra CMOS能制作很大的RFFET,对厚度为150~225μm的正常衬底,几乎不存在寄生电容。晶体管采用介质隔离来提高抗闩锁能力和隔离度。为了达到完全的耗尽工作,硅层极薄至1000A。硅层如此之薄,以致消除了器件的体端,使它成为真正的三端器件。目前,UltraCMOS是在标准6寸工艺设备上生产的,8寸生产线亦已试制成功。示范成品率可与其它CMOS工艺相媲美。

尽管单个开关器件的BVDSS相对低些,但将多个FET串联堆叠仍能承爱高电压。为了确保电压在器件堆上的合理分压,FET至衬底间的寄生电容与FET的源与漏间寄生电容相比应忽略不计。当器件外围达到毫米级使总电阻较低时,要保证电压的合理分压,真正的绝缘衬底是必不可少的。

Peregrine公司拥有此领域的主要专利,采用UltraCMOS工艺将高Q值电感和电容器集成在一起也很容易。线卷Q值在微波频率下能达到50。超快速数字电路也能直接集成到同一个RF芯片上。该公司推出PE4272和PE4273宽带开关例证了UltraCMOS的用处(见图)。这两个75Ω器件设计用于数字电视、PCTV、卫星直播电视机顶盒和其它一些精心挑选的基础设施开关。采用单极双掷格式,它们是PIN二极管开关的很好的替代品,它们可在改善整体性能的同时大大减少了元器件的数量。

两个器件1GHz时的插入耗损仅为0.5dB、P1dB压缩率为32dBm、绝缘度在1GHz时高达44dB。两种器件在3V时静态电流仅为8μA、ESD高达2kV。PE4273采用6脚SC-70封装,绝缘值为35dB。PE4272采用8脚MSOP封装,绝缘值为44dB。10K订购量时,PE4272和PE4273的价格分别为0.45和0.30美元。

和Peregrine公司有合作关系的日本冲电气也开发了类似产品,冲电气称之为SOS技术,SOS技术是以“UTSi”为基础开发的技术。“UTSi”技术是由在2003年1月与冲电气建立合作关系的美国派更半导体公司(PeregrineSemiconductorCorp.)开发的。在蓝宝石底板上形成单晶硅薄膜,然后再利用CMOS工艺形成电路。作为采用具有良好绝缘性的蓝宝石的SOS底板,与硅底板和SOI(绝缘体上硅)底板相比,能够降低在底板上形成的电路耗电量。冲电气开发的RF开关的耗电电流仅为15μA(电源电压为2.5~3V),与使用GaAs材料的现有RF开关相比,耗电量降到了约1/5。

Si BiCMOS

以硅为基材的集成电路共有SiBJT(Si-BipolarJunctionTransistor)、SiCMOS、与结合Bipolar与CMOS特性的SiBiCMOS(SiBipolarComplementaryMetalOxideSemiconductor)等类。由于硅是当前半导体产业应用最为成熟的材料,因此,不论在产量或价格方面都极具优势。传统上以硅来制作的晶体管多采用BJT或CMOS,不过,由于硅材料没有半绝缘基板,再加上组件本身的增益较低,若要应用在高频段操作的无线通信IC制造,则需进一步提升其高频电性,除了要改善材料结构来提高组件的fT,还必须藉助沟槽隔离等制程以提高电路间的隔离度与Q值,如此一来,其制程将会更为复杂,且不良率与成本也将大幅提高。

因此,目前多以具有低噪声、电子移动速度快、且集成度高的SiBiCMOS制程为主。而主要的应用则以中频模块或低层的射频模块为主,至于对于低噪声放大器、功率放大器与开关器等射频前端组件的制造仍力有未逮。

氮化镓GaN

氮化镓并非革命性的晶体管技术,这种新兴技术逐渐用于替代横向扩散金属氧化物硅半导体(Si LDMOS)和砷化镓(GaAs)晶体管技术以及某些特定应用中的真空管。

与现有技术相比,氮化镓(GaN)的优势在于更高的漏极效率、更大的带宽、更高的击穿电压和更高的结温操作,这些特点经常作为推动其批量生产的重要因素,但在价格、可用性和器件成熟度方面还需加以综合考量。

-

半导体

+关注

关注

339文章

31250浏览量

266613 -

氮化镓

+关注

关注

67文章

1915浏览量

120151 -

砷化镓

+关注

关注

4文章

179浏览量

20353

原文标题:行业 | 常见的射频半导体工艺,你知道几种?

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体中常见的载流子散射机制

安森美半导体产品/工艺变更通知解读

华太电子射频PA如何重塑半导体设备行业

半导体器件清洗工艺要求

半导体行业案例:晶圆切割工艺后的质量监控

高精度半导体冷盘chiller在半导体工艺中的应用

半导体冷水机在半导体后道工艺中的应用及优势

苏州芯矽科技:半导体清洗机的坚实力量

半导体制冷机chiller在半导体工艺制程中的高精度温控应用解析

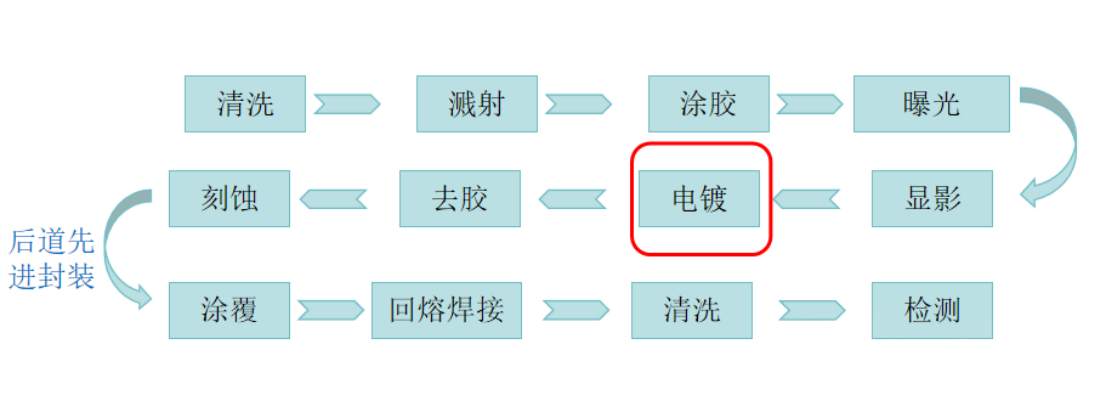

揭秘半导体电镀工艺

常见的几种射频半导体工艺

常见的几种射频半导体工艺

评论