如今,人们对先进封装所面临的挑战已充分了解。然而,在薄化的器件芯片被封装之前,就在晶圆级克服这些挑战可以进一步增加价值和性能,同时降低拥有成本。

这些新材料已展示出超越其他现有解决方案的更出色性能,我们将结合示例,探讨受益于使用经新技术制造的芯片的应用。

概述

更好的系统性能和功能、更低的功耗以及更小的外形尺寸是驱动当今封装技术需要的主要因素。

广泛用于大规模生产的晶圆级封装 (WLP) 技术目前主要用于制造消费类产品,如智能手机、平板电脑和其他手持设备等。

许多封装平台正在部署,以便能够实现更高性能的封装、更低的成本、更小的外形尺寸,以及更高级别的集成。

晶圆级芯片尺寸封装 (WLCSP) 因其成本性能比和无衬底封装而具吸引力,但却受到芯片尺寸的限制。

另一种替代方案,扇出型晶圆级封装 (FOWLP) 技术正在研发和应用,因为它允许通过“扇出”与外部衬垫互连来增加 I/O 密度。最终使其具有更小的外形尺寸和更低的功耗。

异构集成的半导体封装技术,如系统级封装 (SIP) 和堆叠封装 (PoP) 基础结构,由于日益复杂的集成而面临着重大挑战。

晶圆级封装挑战

对于许多此类技术来说,薄化器件的衬底处理是制造流程中的一个主要挑战。

硅晶片薄化至 <50 微米 (µm),或使用一个 RDL-first流程创建的重分布层 (RDL) 需非常小心且制造成本很昂贵。

处理过程要求使用通过临时键合和解键合 (TBDB) 技术处理支撑衬底,以方便构建复杂的封装基础机构【1】。

使用热塑性聚合物制造的临时键合材料通常用于 TB/DB 工艺。

当与载体衬底一起使用时,它们能够提供热机械稳定性,并使薄型器件衬底更易于处理。

然而,在更高的温度下,这些材料表现得更像液体,随着熔体粘度的降低,机械稳定性也逐渐消失,材料软化,从而降低了键合层的稳定性。

器件晶圆可能发生变形和分层,导致下游工艺出现问题【2】。

现在我们已经对先进封装目前所面临的一些挑战进行了高层次的研究,接下来,我们将更深入地探索其中的一些技术。

第 II 部分将研究chip-first和chip-last工艺程流之间的区别,以及为什么后者更受关注和欢迎。

Chip-First或Chip-Last流程

两类主要的扇出型晶圆级封装 (FOWLP) 技术是chip-first和chip-last工艺,又称 RDL-first。

chip-first和chip-last工艺流程都需要高温和高真空工艺来创建重分布层 (RDL)。

当今的 FOWLP 工艺所需的材料需要能够承受高温和恶劣的化学环境,同时保持对器件衬底的机械支持。

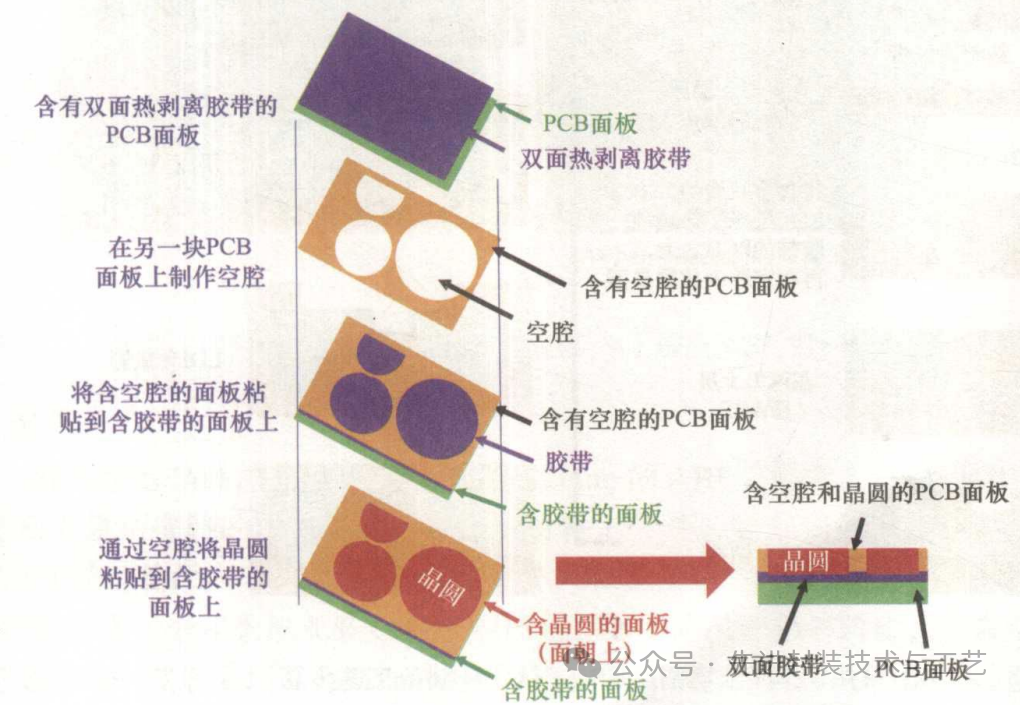

对于chip-first工艺来说,在热压过程中,先将单一芯片放置在用临时键合材料或热释放胶带 (TRT) 处理过的衬底上,然后再用环氧树脂成型化合物 (EMC) 包覆成型并固化。

高温电介质处理会产生应力并导致载体晶圆与 EMC 之间产生翘曲。

在 EMC 工艺流程中,由于衬底翘曲和键合材料软化导致的芯片移动和偏离会造成 RDL 与嵌入芯片的错位【1】。

晶圆在晶圆厂加工完毕后,芯片就会被切成小块。然后,通过取放系统将芯片放置在基于环氧树脂模塑料上的新的 200 毫米或 300 毫米圆晶圆上。

封装工艺在这个新的晶圆上进行,切割芯片,以便获得在扇出型封装中的芯片。

尽管chip-first封装在过去 10 年里一直用于生产,但这一工艺也存在一些挑战。

在工艺流程中,晶圆可能会发生翘曲,嵌入的芯片可能会发生位移,从而导致良率下降。

另一方面,Chip-last/RDL-first还没有得到广泛应用,但是人们对这种方法的兴趣正在增加,因为它使用了与chip-first非常不同的工艺。

RDL-first对于希望从chip-first FOWLP 过渡到尚未准备好应对 2.5D/3D 封装的芯片制造商来说,是一种理想的工艺。

在 RDL-first工艺流程中,玻璃载体晶圆被涂上可去除的激光脱模材料,而 RDL 将在此基础上构建。

激光脱模材料需要具有良好的热稳定性、机械稳定性和化学稳定性,才能经受住薄化、背面介质和沉淀这几道工艺。

首先构建 RDL,然后安装芯片。在该流程中,RDL 结构既可以进行电子测试,也可以进行目视检查,以确定良率损失,从而避免将好的芯片放置在不好的位置。该流程特别适合于良率至关重要的大型 I/O 芯片。

为了确保 FOWLP 成功,无论采用chip-first还是 RDL-first方法,使用合适的键合材料来确保重组晶圆的稳定性和均匀性则至关重要。Brewer Science 已经为此研制了一系列材料。

BrewerBOND®T1100和BrewerBOND®C1300系列材料代表了新一代键合系统,能够提供更高的产量和热稳定性。

这些材料在较高的工艺温度下提供了更好的机械稳定性、良好的化学耐受性,不管是晶圆级或面板级工艺,都能在室温下进行键合和解键合。

较低的总厚度变化 (TTV) 加上该系统机械强度的增加,可使超薄背面晶圆进行薄化,实现研磨后晶圆厚度小于50µm。

BrewerBUILD™ 材料是单层高吸收材料,可用于 RDL 的构建和组装,并专为激光烧蚀工艺而设计。

这些材料增加了 308 nm 至 355 nm 波长的吸光度,并在激光烧蚀工艺中为器件晶圆提供保护。

除了在激光烧蚀工艺中提高性能之外,新一代材料还具有较强的耐溶剂性,对多种材料的附着力高,并且烧蚀后具很好的溶剂清洗效果【2】。

用于FOWLP工艺的材料

本部分,我们将进一步探讨在上文中介绍的用于扇出型晶圆级封装 (FOWLP)的BrewerScience的BrewerBOND® T1100和BrewerBOND® C1300系列材料。

该系统由一种应用于玻璃载体晶圆的低 Tg 热固性材料组成,然后键合至器件晶圆上,而器件晶圆上已经涂有相应的高 Tg 键合材料。

在室温下键合之后,键合对既可以暴露在紫外线 (UV) 下,也可以在热板上烘烤以固化热固性材料

图 1:典型工艺流程

当在 350°C 温度下处理时,BrewerBOND®T1100 系列材料仍然可溶于溶剂,且在 300°C 以下几乎没有熔体流动。

涂层后,这种材料可以高度适形,甚至可以薄涂一层来覆盖严重不平的表面。

图 2 是使用扫描电子显微镜 (SEM),在 80-µm 焊料隆起焊盘上加工的 BrewerBOND®T1100 系列材料的 2.15-µm 薄膜的横截面。

图 2:BrewerBOND® T1100 材料的保形涂敷

BrewerBOND® C1300 系列材料拥有较高的熔态流动性(低 Tg),在固化前为液体的形态。

这样能够无需施压就能在室温下与 BrewerBOND®T1100 系列材料键合。键合后,这种材料需要一个固化过程来形成键合层。这一特性使得该系统即使在高温下也具有较高的机械强度(表 1)。

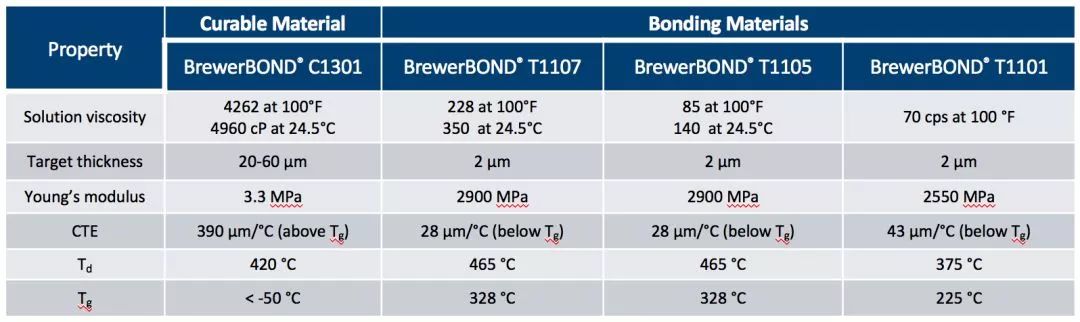

表 1:材料属性

电介质处理、金属沉淀和金属退火是需要使用高温的工艺。

这些新一代 BrewerBOND® 材料能够维持键合层的完整性,不会分解、释气或回流。

这些材料在 350°C 下加热三个小时后,在氮气中进行的等温热重分析 (TGA) 显示,其重量损失不到 6%。

在 FOWLP 技术中,材料对有机和无机衬底以及金属层的附着也是必要的。

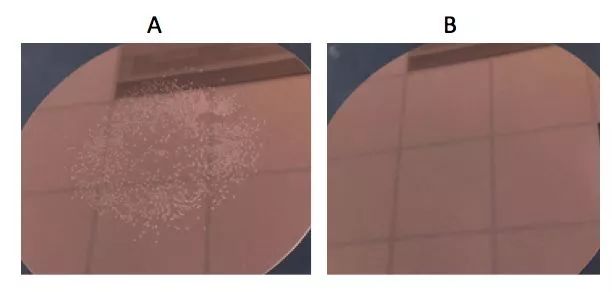

如图 3 所示,新型键合材料对铜板和环氧树脂成型化合物 (EMC) 均展示出良好的附着性。

图 3:键合材料上的铜沉淀:(A) 材料附着性差,显示有缺陷;(B)材料附着性好,无缺陷。

在键合过程中,BrewerBOND®T1100 系列材料连同 BrewerBOND®C1300 系列材料都显示出对常见的下游湿化学工艺的耐受性。

工艺完成后,载体衬底可以通过机械释放或激光烧蚀技术从薄化的器件上移除。

这两种工艺均可在室温下完成,且都是轻力技术,可与薄化衬底一起使用。

当使用激光烧蚀工艺时,BrewerBOND®T1100 系列材料吸收激光烧蚀过程中用于在 308 nm 和 355 nm 解键合时的能量,从而防止激光直接损伤器件晶圆。

解键合完成后,可以使用溶剂或氧等离子体蚀刻工艺从器件衬底上去除 BrewerBOND®T1100 系列材料。

可以使用 Dynaloy 出售的 Dynasolve™ 220 清洁剂材料,从载体衬底上去除 BrewerBOND® C1300 系列材料。

总结

Brewer Science公司正在研发新型临时键合材料和工艺,为 FOWLP 技术的发展铺平道路。

当作为一个系统使用时,这些材料能够改善在高真空和高温下加工的薄化、键合晶圆的机械稳定性。

耐化学性与室温键合和解键合技术相结合,在降低拥有成本的同时,提供了附加价值并提高了性能。

对于 RDL-first工艺,Brewer Science 最近推出了用于构建和装配的 BrewerBUILD™ 材料,它可以成为热释放胶带的优选替代品。

这些新材料促进了低能量激光解键合工艺,为拥有低碳残留的器件晶圆提供了更好的保护。

Brewer Science公司 将通过提供新一代材料来支持 FOWLP 技术,从而继续推进晶圆级封装 (WLP) 技术的发展。

-

晶圆

+关注

关注

53文章

5451浏览量

132768 -

封装

+关注

关注

128文章

9339浏览量

149062

原文标题:解决晶圆级封装难题的新方案

文章出处:【微信号:eda365wx,微信公众号:EDA365电子论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

华为将向业界发布核心网网络智能新方案

晶圆级MOSFET的直接漏极设计

什么是晶圆级扇入封装技术

解决晶圆级封装难题的新方案

解决晶圆级封装难题的新方案

评论