声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

收发器

+关注

关注

10文章

3839浏览量

111464 -

adc

+关注

关注

100文章

7947浏览量

556912 -

dac

+关注

关注

44文章

2856浏览量

197617

发布评论请先 登录

相关推荐

热点推荐

AD9083:16通道、125 MHz带宽JESD204B模数转换器的全方位解析

AD9083:16通道、125 MHz带宽JESD204B模数转换器的全方位解析 在电子设计领域,模数转换器(ADC)的性能直接影响着整个系统的精度和效率。AD9083作为一款16通道、125

AD9094:8位、1 GSPS、JESD204B四通道ADC的深度解析

AD9094:8位、1 GSPS、JESD204B四通道ADC的深度解析 在电子设计领域,ADC(模拟 - 数字转换器)一直是信号处理系统中的关键组件。今天,我们来深入探讨Analog

AD9528:高性能JESD204B/JESD204C时钟发生器的深度解析

AD9528:高性能JESD204B/JESD204C时钟发生器的深度解析 在电子设计领域,时钟发生器对于系统的稳定运行起着至关重要的作用。今天,我们就来深入探讨一款功能强大的时钟发生器

技术文章|高速DAC JESD204接口接收机物理层压力测试(下)

,为大家详细介绍了高速串行JESD204B/C/D标准、高速DAC接收机(RX)面临的物理层测试挑战等内容,并结合SL3000系列误码仪的技术指标、功能指标等给出针

LMK04828 超低噪声JESD204B兼容时钟抖动清除器技术手册

LMK0482x 系列是业界性能最高的时钟调节器,支持 JEDEC JESD204B。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个 JESD204B

LMK0482x系列超低噪声JESD204B兼容时钟抖动清除器技术文档总结

LMK0482x 系列是业界性能最高的时钟调节器,支持 JEDEC JESD204B。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个 JESD204B

LMK04616 超低噪声低功耗JESD204B兼容时钟抖动清除器总结

LMK0461x 器件系列是业界性能最高、功耗最低的抖动清除器,支持 JESD204B。16 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 8 个 JESD204B 转换器或其他逻辑器件。第 17 个输出可配置为提供来自 PLL2 的信号或来自外部 VCXO 的副

LMK04828-EP 超低噪声JESD204B兼容时钟抖动清除器总结

LMK04828-EP 器件是业界性能最高的时钟调理器,支持 JESD204B。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B转换器或其他逻辑器件

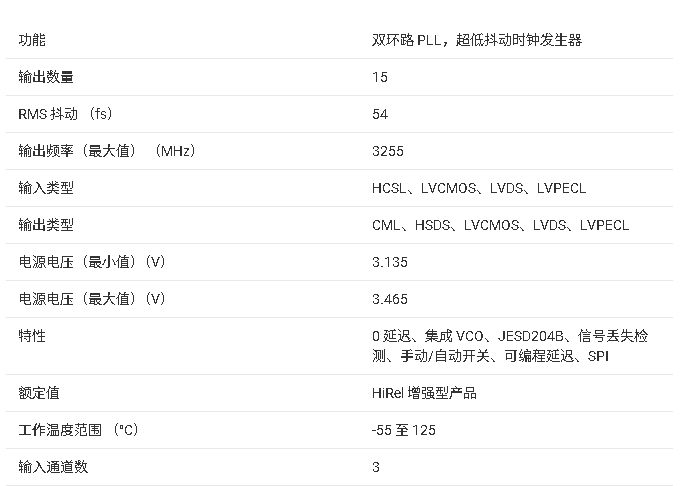

LMK04832 超低噪声、3.2 GHz、15 输出、JESD204B 时钟抖动清除器技术手册

该LMK04832是一款超高性能时钟调节器,支持 JEDEC JESD204B,还与 LMK0482x 系列器件引脚兼容。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个

LMK04368-EP 超低噪声JESD204B/C双环路时钟抖动清除器总结

LMK04368-EP 是一款高性能时钟调节器,支持 JEDEC JESD204B/C,适用于太空应用。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个

JEDSD204B标准verilog实现-协议演进

定性延时的实现方案如下图:

最小延时实现方案如下图:

后续代码实现时,会对上述两种时延的细节进行详细描述。

本连载主要针对JESD204B的subclass1做详细说明和

发表于 09-05 21:18

替代HMC7044超低噪高性能时钟抖动消除器支持JESD204B

VCO 输入,支持高达 3200MHz车载调节器可实现出色的电源抑制比3. 应用• JESD204B 时钟生成• 蜂窝基础设施(多载波 GSM、 LTE、 W-CDMA)• 数据转换器时钟• 微波基带卡• 相控阵参考时钟分布

发表于 05-08 15:57

JESD204B传输层的实现方式介绍

JESD204B传输层的实现方式介绍

评论