了解如何为UltraScale +设计添加额外的安全级别。 该视频演示了如何防止差分功耗分析(DPA),以在比特流配置之上增加额外的安全性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22502浏览量

639231 -

赛灵思

+关注

关注

33文章

1798浏览量

133655 -

安全

+关注

关注

1文章

377浏览量

36853

发布评论请先 登录

相关推荐

热点推荐

AMD Zynq UltraScale+ RFSoC评估套件调试检查表

本篇文章包含一份调试检查表,它是对 AMD Zynq UltraScale+ RFSoC 评估套件(ZCU208、ZCU216、ZCU111 和 ZCU670)上评估板相关问题进行故障排除的重要资源。

探秘MAX11902:18位、1Msps低功耗全差分SAR ADC的卓越性能

探秘MAX11902:18位、1Msps低功耗全差分SAR ADC的卓越性能 一、引言 在电子设计领域,高精度、低功耗的模数转换器(ADC)一直是工程师们追求的目标。MAX11902作

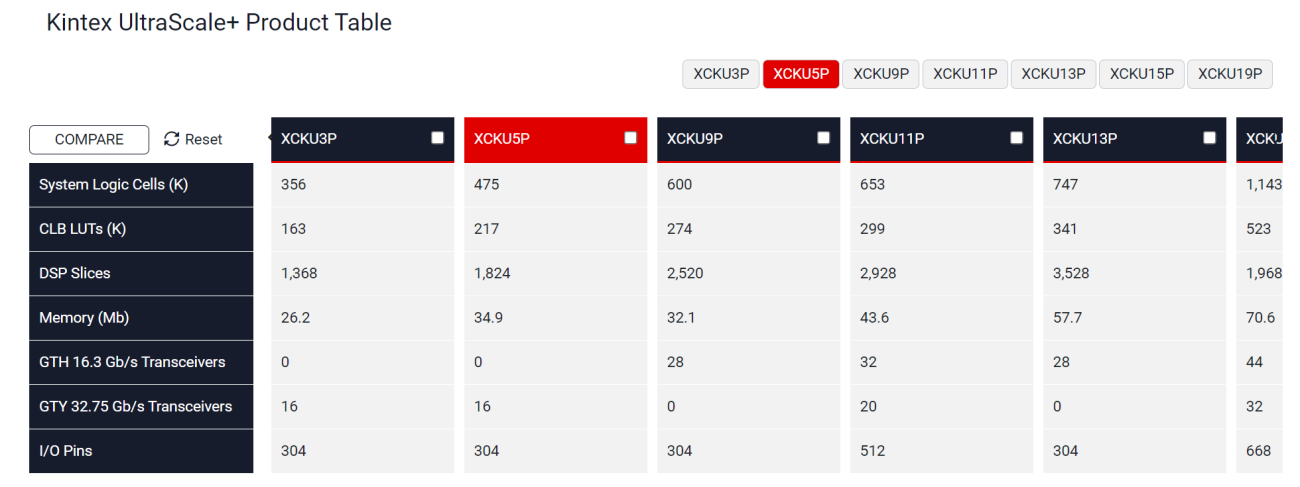

第二代AMD Kintex UltraScale+ FPGA的亮点

第二代 AMD Kintex UltraScale+ FPGA 可有效赋能专业音视频、广播、医疗、机器视觉、机器人技术及测试测量等领域的开发者,助力其打造兼具卓越性能和可靠性的强大系统,即使是面对

【ALINX选型】AMD Kintex UltraScale+ 系列 FPGA 开发板速选

在中高端 FPGA 应用中,AMD Kintex UltraScale+ 系列通常用于对吞吐能力、接口规模和功耗控制都有高要求的系统。其中, XCKU15P 是一个被广泛采用的型号,它在资源规模

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

在本博客中,我们将介绍使用 Aurora 6466b 协议实现 AMD UltraScale+ FPGA 与 AMD Versal 自适应 SoC 的对接。我们还将涵盖有关 IP 配置、FPGA 之间的连接、时钟设置以及复位拓扑结构的详细信息。

如何在Zynq UltraScale+ MPSoC平台上通过JTAG启动嵌入式Linux镜像

流程教程)。本文则进一步讲解如何在 Zynq UltraScale+ MPSoC 平台上通过 JTAG 逐步启动 Linux,并提供了完整的过程与关键命令。只要按步骤操作,即使是复杂的 Linux 镜像也能成功通过 JTAG 启动。

低功耗低成本差分ADC驱动器AD8137的深度剖析

低功耗低成本差分ADC驱动器AD8137的深度剖析 在当今对功耗和成本极为敏感的系统设计中,一款性能卓越的差

AMD UltraScale架构:高性能FPGA与SoC的技术剖析

的性能,成为了众多工程师的首选。本文将深入剖析UltraScale架构的各个方面,为电子工程师们提供全面的技术参考。 文件下载: AMD ,Xilinx Artix™ UltraScale+

现已上市:AMD Spartan UltraScale+ FPGA SCU35 评估套件——面向所有开发人员的经济实惠平台

设计。 灵活、可靠且高能效的连接 这款新的评估套件使用户 能够验证 Spartan UltraScale+ SU35P FPGA,并连接套件提供的各种接口选项。 它面向需要高 I/O、低功耗、多传感器配置

AMD Spartan UltraScale+ FPGA的优势和亮点

AMD Spartan UltraScale+ FPGA 集小型封装、先进的 I/O 功能与低功耗等优势于一体。该系列 FPGA 配备高速 16.3 Gb/s 收发器、内置的外部内存控制器以及

光隔离探头与高压差分探头的技术特性分析与替代性研究

文章对比了光隔离探头与高压差分探头,分析其工作原理、性能参数及适用场景,总结其技术差异与替代性。

fpga开发板 璞致 Kintex UltraScale Plus PZ-KU3P 与 PZ-KU5P核心板与开发板用户手册

Xilinx Kintex UltraScale+系列FPGA器件采用FinFET工艺,具有120万逻辑单元、UltraRAM、100G以太网MAC等资源,功耗比7系列降低60%。璞致电子开发

璞致电子 UltraScale+ RFSoC 架构下的软件无线电旗舰开发平台

璞致电子 PZ-ZU49DR-KFB 开发板基于 Xilinx ZYNQ UltraScale+ RFSoC XCZU49DR 主控制器,以 "ARM+FPGA 异构架构" 为

AMD Spartan UltraScale+ FPGA 开始量产出货

高 I/O、低功耗及先进的安全功能,适用于成本敏感型边缘应用 AMD 很高兴宣布,Spartan UltraScale+ 成本优化型系列的首批器件现已投入量产! 三款最小型的器件——SU10P

如何防止UltraScale+的差分功耗分析

如何防止UltraScale+的差分功耗分析

评论