Jigyasa Panchal 和 Vatsal Tripathi

在本博客中,我们将介绍使用 Aurora 6466b 协议实现 AMD UltraScale+ FPGA 与 AMD Versal 自适应 SoC 的对接。我们还将涵盖有关 IP 配置、FPGA 之间的连接、时钟设置以及复位拓扑结构的详细信息。

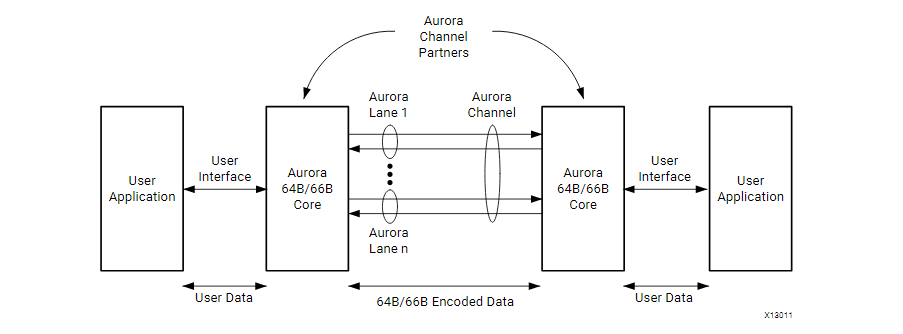

Aurora 64B/66B 是一项用于多千兆位链路的轻量级串行通信协议。它使用一个或多个 GTX、GTH、GTY 或 GTM 收发器在器件之间进行数据传输。可以采用全双工(双向数据)连接,也可以采用单工(任一方向的数据)连接。本博客重点关注两种器件双工配置下的互联操作: UltraScale+ FPGA 使用 GTY连接 Versal 自适应 SoC 的 GTM。

本博客涵盖以下内容:

1. VCU118 和 VMK180 的示例设计

2. IP 配置

3. 综合、实现与比特流生成

4. 复位序列

5. FPGA 之间的连接

这里使用的两个 FPGA 分别是 AMD Virtex UltraScale+(VCU118 评估板)和 Versal Prime(VMK180 评估板)。此测试中使用的是 AMD Vivado 2024.2。在“相关”部分中包含了测试使用的比特流。

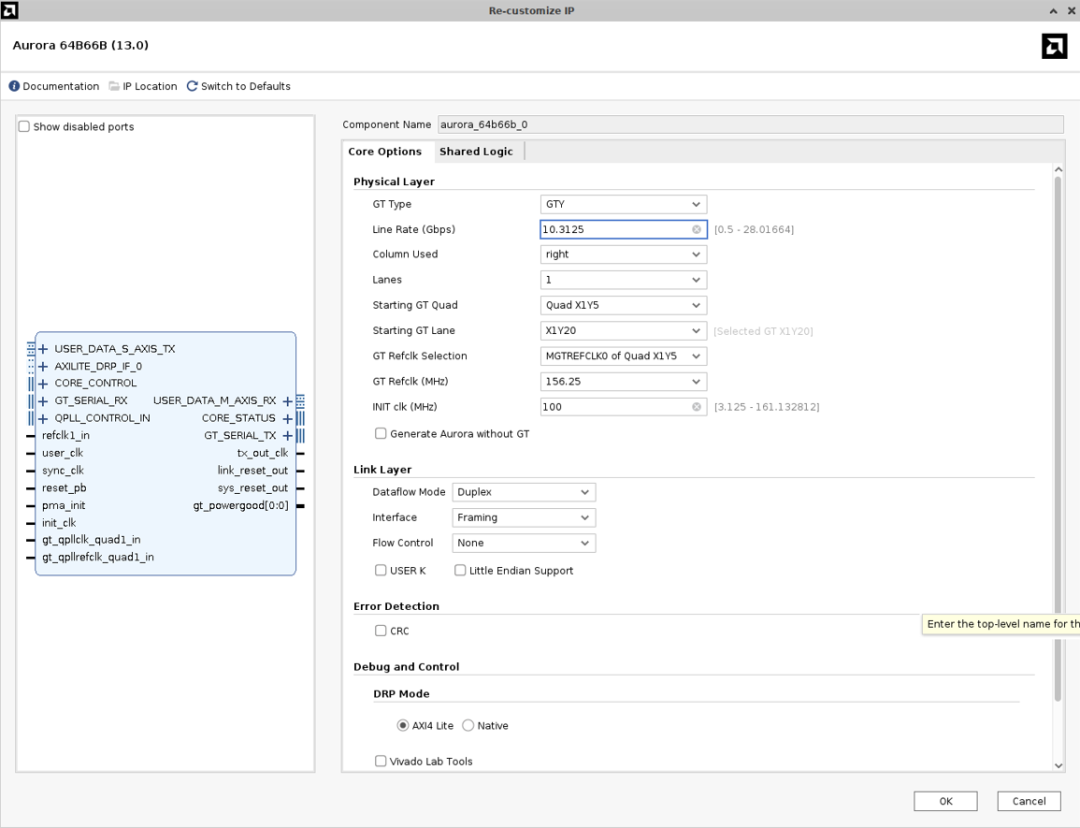

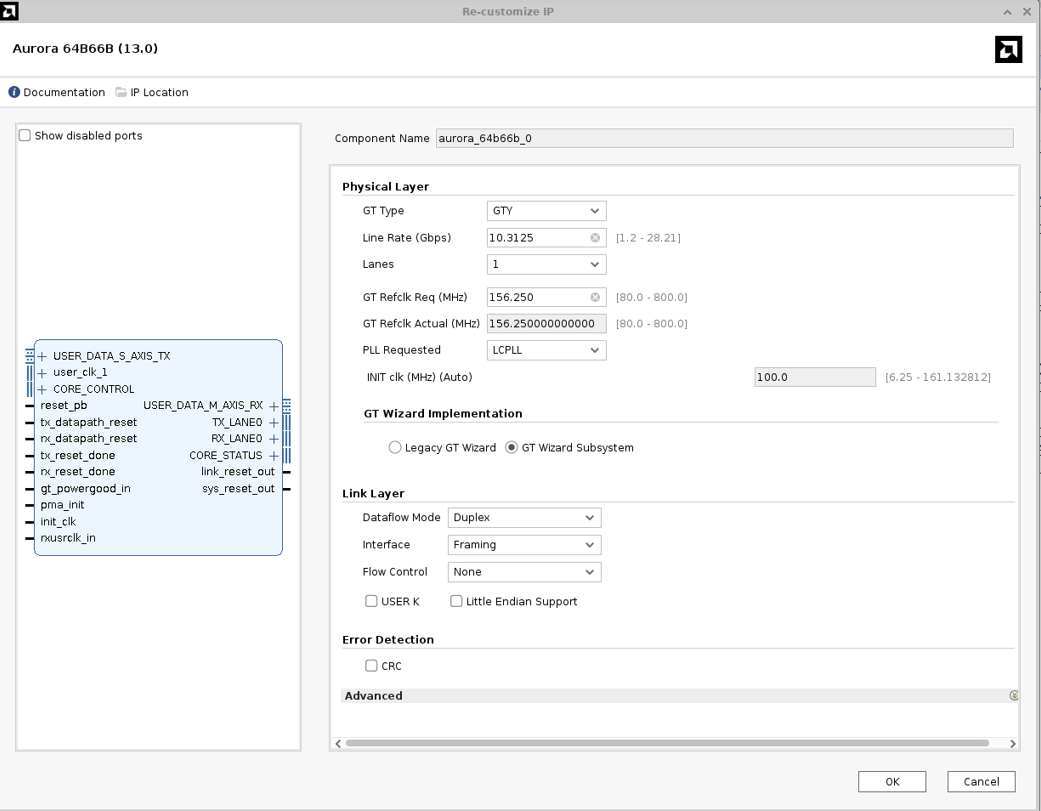

在 Aurora 6466b IP 自定义 GUI 中,有两个选项卡:“Core Options”(核选项)和“Shared Logic”(共享逻辑)。在“Core Options”选项卡中,您可以选择下列配置的相关选项:通道宽度、线速率、GT 参考时钟、INIT 时钟与 DRP 时钟频率、数据流为双工/仅发送/仅接收、接口为成帧或串流以及调试选项。

在“Shared Logic”选项中,您需要在“Include Shared Logic in core”(在核中包含共享逻辑)或“Include Shared Logic in example design”(在示例设计中包含共享逻辑)两者之间进行选择。

对于上述示例设计,建议两个器件的线速率和 GT REFCLK 保持一致,以确保两端的连接稳定,这也是一项良好的实践。

1.VCU118 和 VMK180 的示例设计

VCU118 的单通道示例设计

自定义 Aurora 核。

请按照以下步骤为单通道自定义并生成 Aurora 64b66b 核:

启动 Vivado Design Suite。

选择“Create New Project”(创建新工程)并单击“Next”(下一步)。

选择工程名称和路径,然后单击“Next”。

选择 RTL 工程以允许运行示例设计,并勾选“Do not specify sources at this time”(此时不指定源文件)。单击“Next”。

单击 xcvu9p-flga2104-2L-e,或选择“Boards”(开发板)选项,然后单击“Virtex UltraScale+ VCU118 Evaluation Platform(xcvu9p-flga2104-2L-e)”

单击“Next”,然后单击“Finish”(完成)。

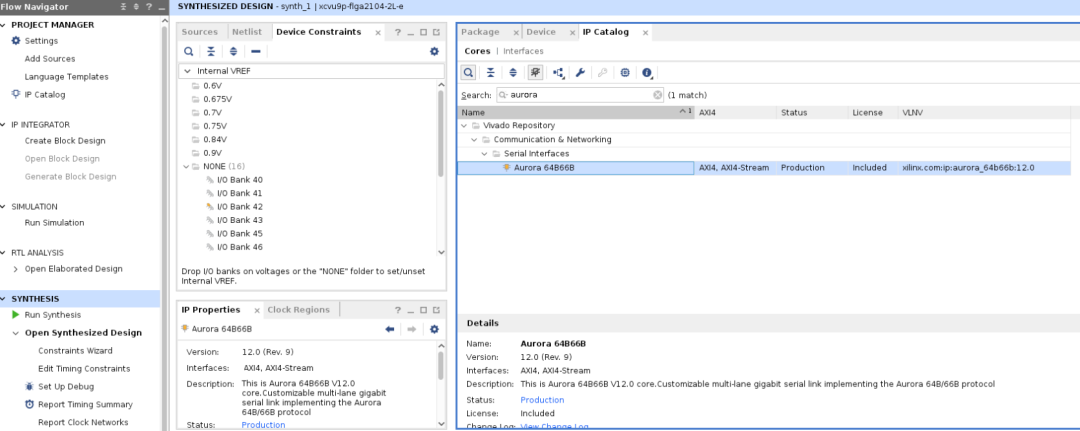

在 Flow Navigator 面板的“Project Manager”(工程管理器)下,选择 IP 目录并搜索

Aurora 64b66b。在“Communication & Networking > Serial Interfaces”(通信与联网 > 串行接口)下可以找到 Aurora 核。

在为 VMK180 创建 2 通道示例设计时也应遵循相同的步骤。

VMK180 的单通道示例设计

自定义 Aurora 核。

请按照以下步骤为单通道示例自定义并生成 Aurora 64b66b 核:

启动 Vivado Design Suite。

选择“Create New Project”(创建新工程)并单击“Next”(下一步)。

选择工程名称和路径,然后单击“Next”。

选择 RTL 工程以允许运行示例设计,并勾选“Do not specify sources at this time”(此时不指定源文件)。单击“Next”。

单击 xcvp1802-lsvc4072-2MP-e-S,或选择“Boards”选项,然后单击“Versal VMK180 ES1 Evaluation Platform”(Versal VMK180 ES1 评估平台)。

单击“Next”,然后单击“Finish”(完成)。

在 Flow Navigator 面板的“Project Manager”(工程管理器)下,选择 IP 目录并搜索 Aurora 64b66b。在“Communication & Networking > Serial Interfaces”(通信与联网 > 串行接口)下可以找到 Aurora 核。

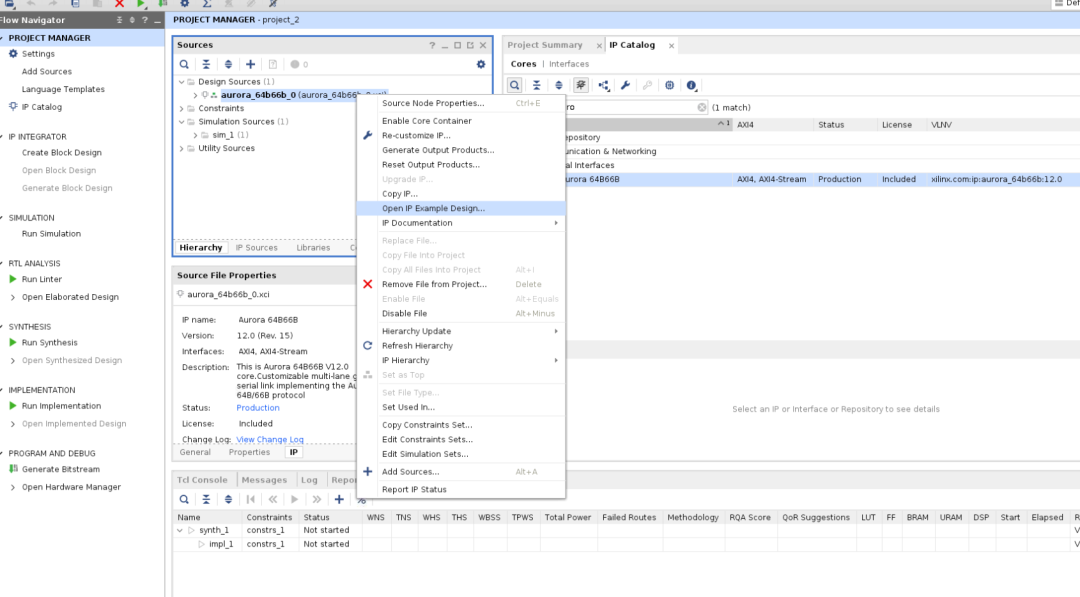

图 1:Vivado IP 目录中的 Aurora 64B66B

VCU118 和 VMK180 的示例设计共享以下软件需求:

VCU118- vivado design suite 2025.1

VMK180- vivado design suite 2025.1

2.IP 配置

对于 VCU118。

右键单击 Aurora 64B66B 并选择“Customize IP”(自定义 IP)。

在“Customize IP”窗口的“Core Options”(核选项)选项卡中,将“GT Refclk (MHz)”设置为 156.25,将“INIT clk (MHz)”设置为 100。见图 2。

注释:为 VCU118 自定义 IP 时,您还可以选择 Vivado Lab Edition。这将允许您在顶层文件中添加内建 ILA 和 VIO。

图 2:Aurora 64B66B 核选项设置

对于 VMK180。

右键单击 Aurora 64B66B 并选择“Customize IP”(自定义 IP)。

在“Customize IP”窗口的“Core Options”选项卡中,将“GT Refclk (MHz)”设置为 156.25。

将“INIT clk (MHz)”设置为 100。见图 3。

图 3:为 VMK180 自定义 Aurora 64B66B 核。

注释:建议在实践中,两项设计的线速率和 GT REFCLK 保持一致。INIT CLK 根据开发板上的系统时钟进行配置。

综合、实现与比特流生成

在 Vivado IDE 的“Project Manager”部分,右键单击核名称并选择“Open IP Example Design”(打开 IP 示例设计)(见图 4)。

单击“OK”覆盖现有示例设计。

生成示例设计后,运行综合。

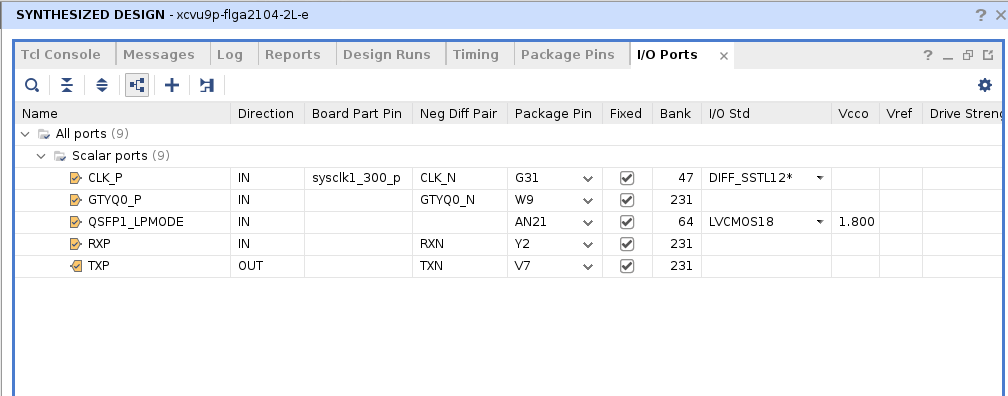

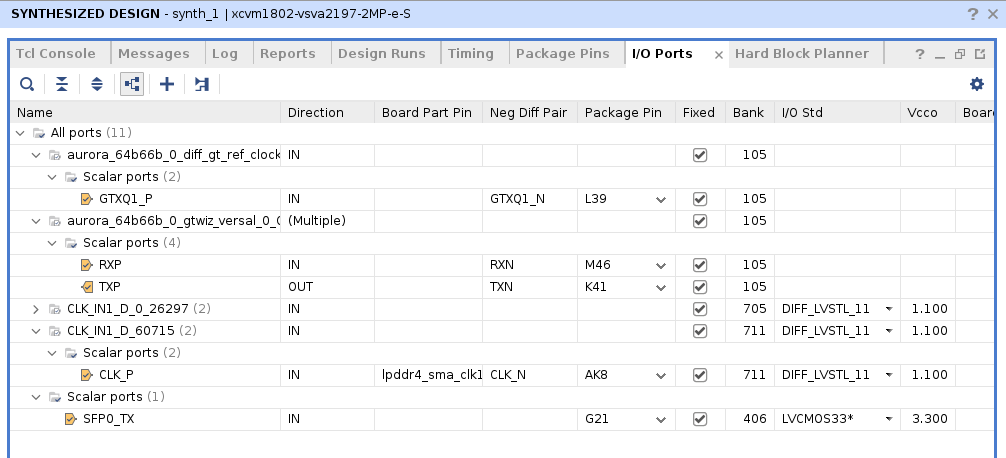

在 I/O 管脚分配中为 Aurora 核端口分配管脚位置(见图 5)。

完成管脚分配后,保存并更新 XDC 文件,然后运行实现。

下一步是生成比特流。

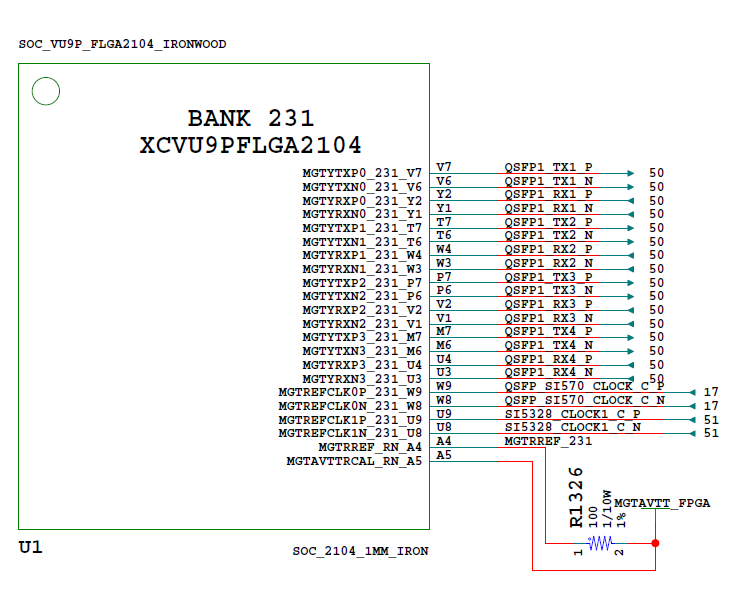

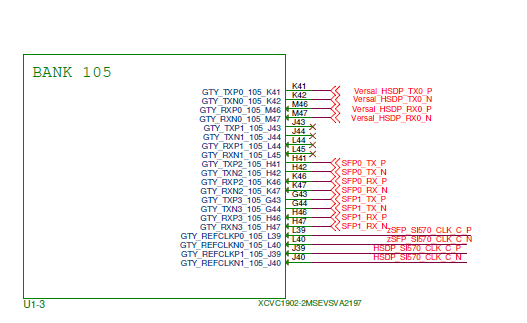

注释:VCU118 的 I/O 端口是基于 bank 231 的原理图进行分配的(见图 6)。

图 4:打开 IP 示例设计

图 5:VCU118 的 I/O 端口

图 6:VCU118 的 I/O 管脚分配所使用的 bank 231 的原理图

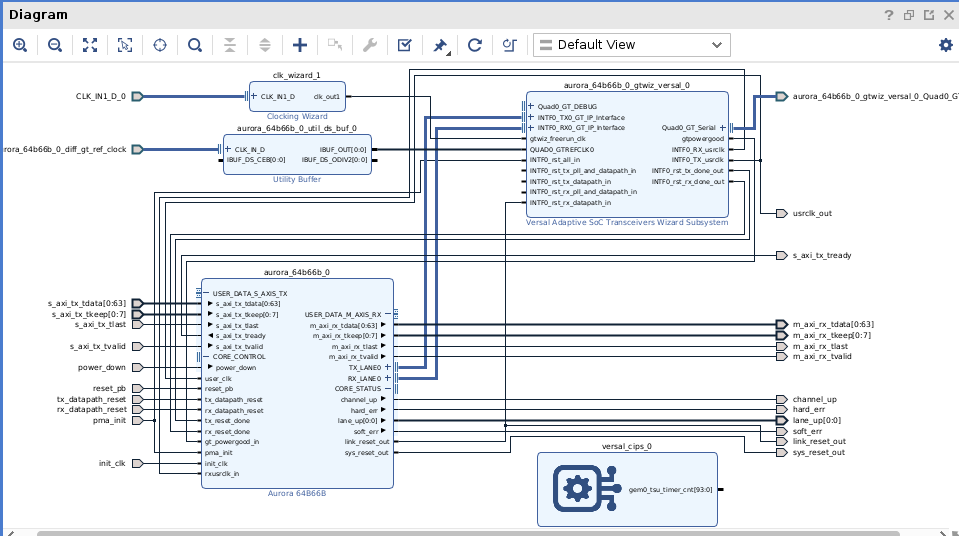

对于 VMK180。

在 Vivado IDE 的“Project Manager”部分,右键单击核名称并选择“Open IP Example Design”。(见图 6)

单击“OK”覆盖现有示例设计。

生成示例设计后,运行综合。

在 I/O 管脚分配中为 Aurora 核端口分配管脚位置(见图 7)。

完成管脚分配后,保存并更新 XDC 文件,然后运行实现。

下一步是生成比特流。

图 7:在生成示例设计后为 VMK180 生成的块设计

图 8:VMK180 的 I/O 端口

图 9:VMK180 的 I/O 管脚分配所使用的 bank 105 的原理图

注释:VMK180 的 I/O 端口是基于 bank 105 的原理图进行分配的(见图 8)。

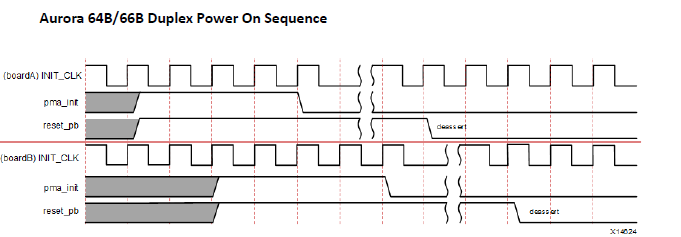

4.上电与复位序列

以下是在可用数据流配置的示例设计层面针对 Aurora 64B/66B 核推荐的 Aurora 双工复位序列。有关复位序列请见图 10。

在开发板上电序列期间,pma_init 和 reset_pb 信号应处于高电平状态。为确保 Aurora 64B/66B 核正常工作,INIT_CLK 与 GT_REFCLK 在上电期间应保持稳定。当两个时钟稳定后,将 pma_init 断言无效,然后再将 reset_pb 断言无效。

图 10:Aurora 64B/66B 双工上电复位序列

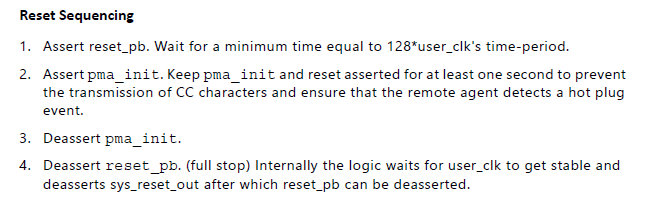

以下是在数据传输之前连接两个器件的步骤。

图 11:复位时序

5.FPGA 之间的连接

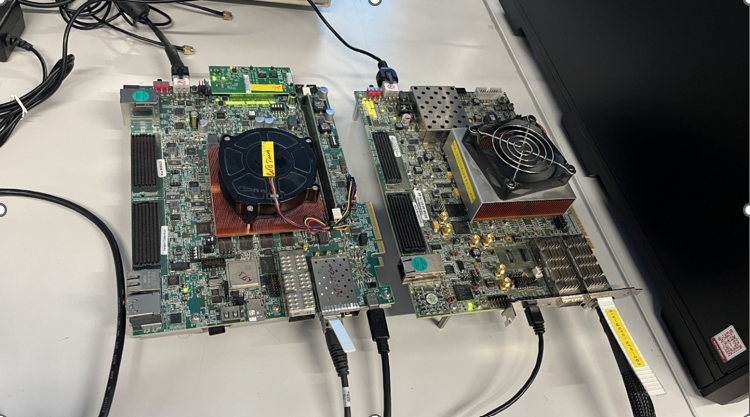

此示例展示了两个平台之间的单通道 Aurora 64B66B 连接。此平台由 VCU118 和 VMK180 评估套件板组成,如图 12 所示。随后对两个器件进行烧录,将烧录文件设置为比特流文件名 (aurora_64b66b_0_exdes.bit),将探针文件设置为探针文件名 (aurora_64b66b_0_exdes.ltx)。

图 12:Aurora 64B/66B 单通道设置

注释:如果在 AMD 评估板上进行测试,请确保已启用 QSFP/SFP 端口。请根据相应的开发板原理图启用这些端口。

要执行该设计,需遵循以下必要步骤:

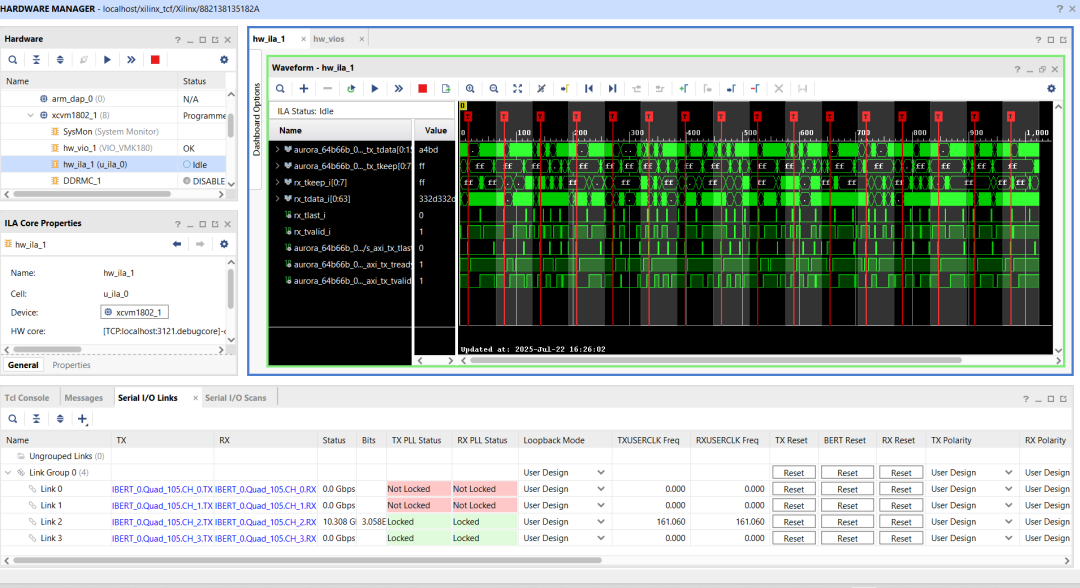

在“Hardware”(硬件)列表中右键单击器件并选择“Run Trigger”(运行触发器)。在出现的波形窗口中,观察到 lane_up 和 channel_up 信号处于高电平状态。

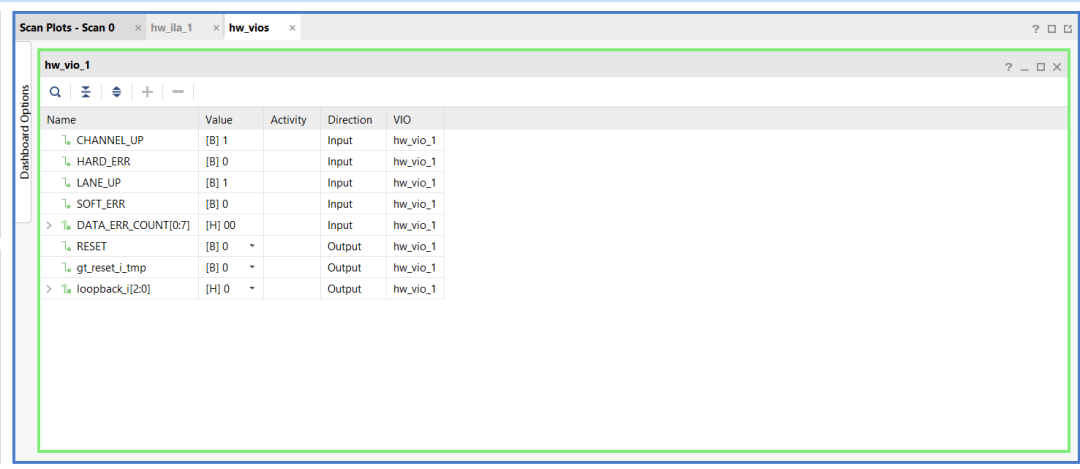

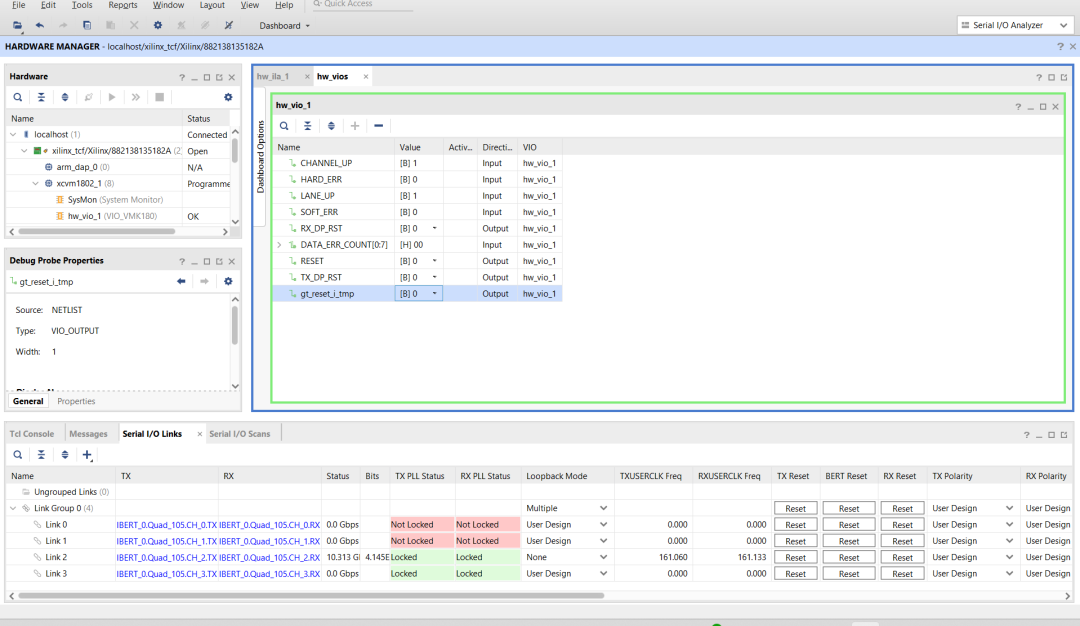

在 hw_vios 下的“Debug Probes”(调试探针)列表中选中以下所有信号,将探针添加到 VIO 窗口中:channel_up、lane_up、RESET、gt_reset_i_temp。

按照复位序列切换复位信号,具体操作是:先对器件 A 断言 pma_init 有效,再对器件 B 断言该信号有效;随后先对器件 A 断言 RESET_PB 有效,再对器件 B 断言该信号有效,如图 9 所示。

channel_up 和 lane_up 信号必须变为低电平状态。

随后再次依次切换器件 A 与器件 B 的复位信号。每次复位信号切换后,channel_up 和 lane_up 都会返回高电平状态。

以下步骤表明,当 reset_pb 和 pma_init 断言有效时,核(或收发器)处于复位状态,channel_up 和 lane_up 均变为低电平状态。然而,当这两个复位信号均为低电平状态时,核会发生解复位,channel_up 和 lane_up 均为高电平状态。

图 13:VCU118 的 Aurora 64B/66B HW-ILA 波形

图 14:VCU118 的 Aurora 64B/66B VIO 探针窗口

图 15:VMK180 的 Aurora 64B/66B HW-ILA 波形

图 16:VMK180 的 Aurora 64B/66B VIO 探针窗口

-

FPGA

+关注

关注

1664文章

22502浏览量

639076 -

收发器

+关注

关注

10文章

3838浏览量

111445 -

amd

+关注

关注

25文章

5707浏览量

140398 -

Versal

+关注

关注

1文章

176浏览量

8538

原文标题:开发者分享 | 使用 Aurora 6466b 实现 AMD UltraScale+™ FPGA 与 AMD Versal™ 自适应 SoC 之间的互联

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

AMD Versal自适应SoC中eMMC烧录/启动调试检查表(上)

AMD Versal自适应SoC内置自校准的工作原理

AMD率先推出符合DisplayPort™ 2.1 8K视频标准的FPGA和自适应SoC

AMD推出全新Spartan UltraScale+ FPGA系列

AMD 扩展市场领先的 FPGA 产品组合,推出专为成本敏感型边缘应用打造的AMD Spartan UltraScale+ 系列

AMD推出Spartan UltraScale+ FPGA系列产品

AMD 扩展市场领先的 FPGA 产品组合,推出专为成本敏感型边缘应用打造的AMD Spartan UltraScale+ 系列

AMD推出全新Spartan UltraScale+ FPGA系列

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

AMD Versal自适应SoC器件Advanced Flow概览(上)

AMD Versal自适应SoC器件Advanced Flow概览(下)

AMD Spartan UltraScale+ FPGA 开始量产出货

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

评论