Virtex®-7 2000T拥有 68 亿个晶体管, 200 万个逻辑单元,相当于 2,000 万个 ASIC 门。这也是首款采用赛灵思独特的堆叠硅片互联(SSI)技术的FPGA。Virtex-7 2000T将使其无需借助并行或者串行I/O, 或者通过片外的 PCB连线与相邻的 FPGA 互联, 即可充分享受到FPGA芯片内高带宽、低时延、低功耗互联机制的优势。

了解如何将复杂的SoC平台映射到单个Virtex®-7 2000T FPGA

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1655文章

22287浏览量

630315 -

赛灵思

+关注

关注

33文章

1797浏览量

133150 -

soc

+关注

关注

38文章

4514浏览量

227631

发布评论请先 登录

相关推荐

热点推荐

【TES818 】青翼凌云科技基于 VU13P FPGA+ZYNQ SOC 的 8 路 100G 光纤通道处理平台

TES818是一款基于VU13PFPGA+XC7Z100SOC的8路100G光纤通道处理平台,该平台采用一片Xilinx的VirtexUltraScale+系列FPGA(XCVU13

请问如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?

如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?有参考教程吗?小白求教

主要是引脚分配,我这边有移植到Xilinx Artix-

发表于 11-11 07:44

蜂鸟E203在黑金XC7A200T型FPGA上的移植工作

一、队伍介绍

本篇介绍的内容是蜂鸟E203在黑金XC7A200T型FPGA上的移植工作。

二、前言

由于我们队的设计需要用到DDR,比赛提供的MCU200T

发表于 10-31 07:54

NVMe高速传输之摆脱XDMA设计43:如何上板验证?

Virtex-7 FPGA Gen3 PCIE 集成块和 UltraScale+ Gen4 PCIE集成块, 为证明 NoP 逻辑加速引擎对不同版本硬核的适配性, 硬件平台将在 VC709F

发表于 10-30 18:10

如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

如标题所示,我们分享如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

具体步骤

1. 将蜂鸟soc移植到Vivado

只要将端口

发表于 10-21 11:08

【VPX650 】青翼凌云科技基于 VPX 系统架构的 VU13P FPGA+ZYNQ SOC 超宽带信号处理平台

VPX650 是一款基于 6U VPX 系统架构的 VU13P FPGA + XC7Z100 SOC 超宽带信号处理平台,该平台采用一片

【TES600G】青翼凌云科技基于JFM7K325T FPGA+FT-M6678 DSP的全国产化信号处理平台

的Kintex-7系列FPGAJFM7K325T16作为协处理单元,具有1个FMC子卡接口,具有4路SFP+万兆光纤接口,具有2路RJ45千兆以太网接口,其中1路挂在FP

Altera Agilex 3 FPGA和SoC产品介绍

Altera 的 Agilex 3 FPGA 和 SoC 可在不影响性能的前提下显著提高成本效益。其通过出色的 Hyperflex FPGA 架构、先进的收发器技术、更高的集成度和更强大的安全

如何将小于1024字节的缓冲区从FPGA发送到PC?

的 PC 请求读取时出现错误,然后我尝试从 FPGA 连续发送到 PC。

最后,我意识到 PC(主机)只能读取 1024 个字节。 非常糟糕,如何将小于1024字节的缓冲区从FPGA发送到PC?

发表于 05-09 08:18

如何将RT-Thread移植到NXP MCUXPressoIDE上

RT-Thread默认支持的IDE只有IAR 和 Keil, 那如何将RT-Thread移植到NXP MCUXPressoIDE上呢?本文内容比较简单但稍有琐碎,希望对有需要的小伙伴有所帮助。

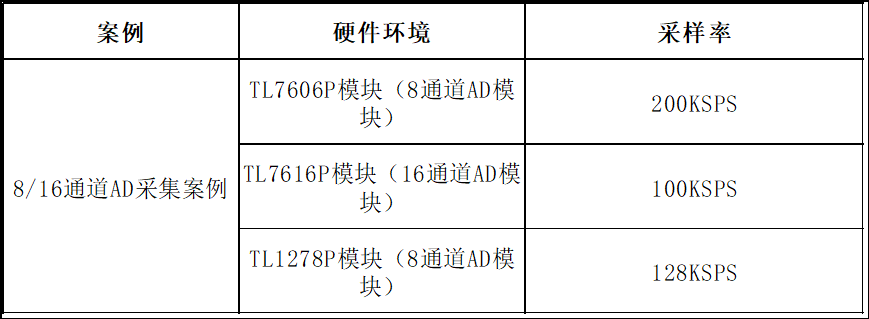

16通道AD采集方案,基于复旦微ARM + FPGA国产SoC处理器平台

FMQL20S400M评估板(TLFM20S-EVM)、TL7606P模块、TL7616P模块和TL1278P模块。 复旦微FMQL20SM ARM+FPGA SoC国产平台介绍 FMQL20S400M是复旦微四核ARM Cor

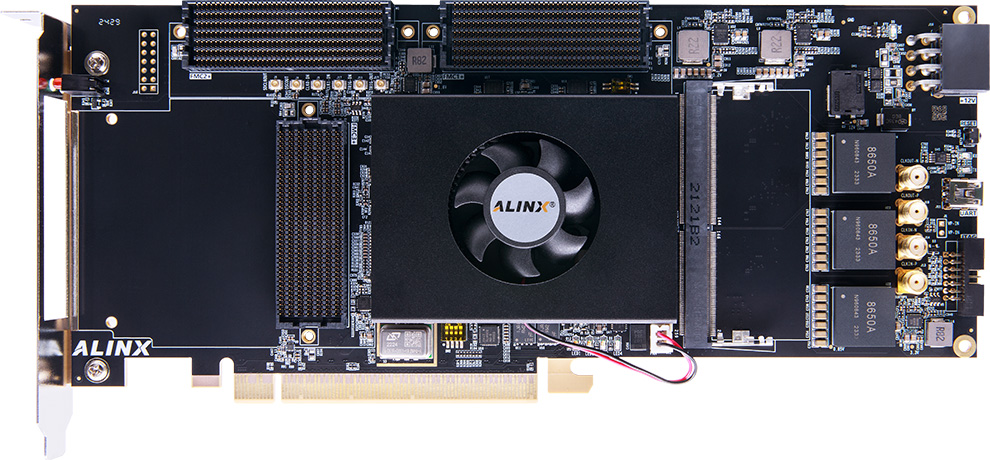

ALINX 发布 AXVU13P:AMD Virtex UltraScale+ 高端 FPGA PCle 3.0 综合开发平台

ALINX 正式发布 AMD Virtex UltraScale+ 系列 FPGA PCIe 3.0 综合开发平台 AXVU13P! 这款搭载 AMD 16nm 工艺 XCVU13P 芯片的高性能

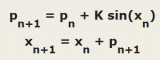

如何将复杂的SoC平台映射到单个Virtex-7 2000T FPGA上

如何将复杂的SoC平台映射到单个Virtex-7 2000T FPGA上

评论