Virtex-7 FPGA的时钟输入主要通过其全局时钟缓冲器(BUFG、BUFH等)和时钟管理模块(MMCM、PLL)来处理。对输入时钟的要求主要围绕电气特性、抖动和引脚分配。

1. 电气特性与引脚兼容性

支持的I/O标准:全局时钟输入引脚(通常位于MRCC/SRCC bank)支持多种差分和单端标准。

差分:LVDS(低压差分信号)、LVPECL、HSTL、HCSL、BLVDS等。这是最推荐的方式,因为抗噪能力强,抖动性能好。

单端:LVCMOS(3.3V, 1.8V等)、LVTTL、HSTL、SSTL。

电压匹配:必须根据FPGA Bank的VCCO电压来选择匹配的I/O标准。例如,如果Bank的VCCO为1.8V,则不能使用LVCMOS3.3标准的时钟信号。

端接:对于高速差分时钟(>100 MHz),必须在PCB上靠近FPGA引脚处进行端接匹配,以防止信号反射。

差分端接:通常在接收端并联一个100Ω电阻。

LVPECL端接:需要特殊的戴维宁端接(例如,130Ω上拉+82Ω下拉到VCC-2V)或使用AC耦合。

2. 抖动要求

抖动是衡量时钟质量的核心指标,分为时间间隔误差(TIE)、周期抖动(Period Jitter)和相位抖动(Phase Jitter)。

总抖动(Total Jitter):对于一般应用,需要小于时钟周期的1/10到1/20。

相位抖动:这是更关键的指标,通常需要在特定频带内(如12 kHz - 20 MHz)进行测量。Xilinx的MMCM/PLL对输入时钟的相位抖动有容忍度。一个质量优良的时钟源,其相位抖动应低于1 ps RMS(在12 kHz - 20 MHz范围内)。

MMCM要求:输入时钟的抖动会经过MMCM的抖动滤波效应。高频抖动会被衰减,但低频抖动( wander)会几乎无衰减地传递到输出。因此,时钟源的低频噪声性能至关重要。

3. 引脚分配与使用建议

使用专用时钟引脚:必须将外部时钟输入连接到标有MRCC(多区域时钟)或SRCC(区域时钟)的引脚。这些引脚有专用的、低抖动的路由路径直接连接到时钟管理模块(CMT)和全局时钟缓冲器。

避免使用普通I/O:切勿将时钟信号连接到普通用户I/O引脚,否则会引入巨大的抖动和布线延迟,导致时序难以收敛。

参考手册:具体使用必须参照《Virtex-7 FPGA Packaging and Pinout》手册(UG475)和《7 Series FPGAs SelectIO Resources》手册(UG471)。

JESD204B接口的时钟架构是其实现同步的关键,也是设计中最复杂的部分。它主要涉及两种时钟:器件时钟(Device Clock)和SYSREF信号。

XC7V690T内部的GTX收发器是实现JESD204B的核心。

1. 器件时钟

定义:提供给FPGA和高速数据转换器(ADC/DAC)的核心工作时钟。所有收发器(GTX)的并行数据和逻辑操作都同步于这个时钟。

频率:其频率与链路数据率(Lane Rate)和帧时钟有确定的倍数关系。

链路数据率 = 器件时钟频率 × 40 / (CF × HD)

其中,CF是每帧的字节数,HD是高密度模式标志。

要求:

极低的抖动:这是最严格的要求。器件时钟的抖动会直接传递给GTX收发器的串行数据,增加接收端的误码率(BER)。通常要求< 100 fs RMS(在12 kHz - 20 MHz频带内)的高性能时钟。

差分输入:必须使用LVDS或HCSL等差分形式,通过MRCC引脚输入。

路由匹配:连接到FPGA和所有数据转换器的器件时钟必须等长,以最小化器件间的时钟偏斜(skew)。

2. SYSREF 信号

定义:JESD204BSubclass 1模式下的确定性延迟对齐参考信号。它用于同步所有设备内的本地多帧时钟(LMFC)和初始帧对齐。

性质:一个周期性的脉冲信号,其频率是器件时钟频率的整数分频。

要求:

与器件时钟同步:SYSREF必须与器件时钟边沿对齐(在规定的建立/保持时间窗口内)。这通常要求SYSREF和器件时钟来自同一个时钟源(例如,同一时钟芯片的不同输出)。

严格的时序:必须满足FPGA GTX收发器对SYSREF的建立和保持时间要求(详见UG476)。 violation会导致对齐失败,链路无法同步。

PCB布线:SYSREF到FPGA和所有转换器的布线必须严格等长,甚至比器件时钟的要求更高,以确保所有设备在同一时钟边沿捕获到SYSREF。

3. XC7V690T GTX 对时钟架构的实现

在FPGA内部,时钟处理流程如下:

器件时钟输入后,通常通过一个BUFG连接到:

GTX收发器的QPLL/CPLL:为串行器/解串器提供比特率时钟。

GTX的DRP时钟:用于控制接口。

JESD204B IP核的用户逻辑时钟:用于处理并行数据。

SYSREF信号输入后,会直接连接到GTX收发器的SYSREF专用引脚。GTX内部电路会在SYSREF有效边沿到来时,对本地计数器进行复位,从而实现所有通道的确定性对齐。

总结与关键设计要点

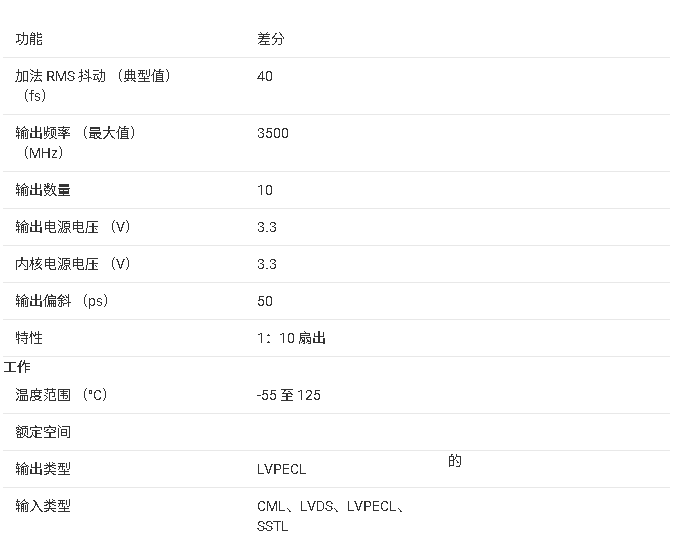

| FPGA全局时钟 | 提供FPGA内核和GTX的基本工作时钟。 | 电气兼容,抖动<1 ps RMS,使用MRCC/SRCC引脚。 | 差分走线,100Ω端接,参考完整地平面。 |

| JESD204B 器件时钟 | FPGA和ADC/DAC的核心同步时钟。 | 极低抖动(<100 fs RMS),频率与链路速率匹配。 | 到FPGA和所有转换器的时钟线严格等长。 |

| JESD204B SYSREF | 实现确定性延迟(Subclass 1)。 | 必须与器件时钟边沿对齐,满足建立/保持时间。 | 到所有设备的SYSREF线严格等长,且与器件时钟同步同源。 |

| 时钟类型 | 作用 | 关键要求 | PCB设计要点 |

|---|

最终建议:

使用专业时钟芯片:选择支持JESD204B的时钟发生器(如TI的LMK系列,ADI的HMC系列),它们能产生超低抖动的器件时钟和与之严格同步的SYSREF信号。

meticulous PCB布局:

将时钟芯片靠近FPGA放置。

器件时钟和SYSREF走线必须作为差分对处理,长度匹配要求通常在±5 mil以内。

为时钟信号提供完整的接地屏蔽和隔离。

查阅官方文档:

《7 Series FPGAs GTX/GTH Transceivers User Guide》(UG476) - JESD204B部分的圣经。

《JESD204B Survival Guide》- 无论哪个厂商都会推荐的系统级参考资料。

Xilinx的JESD204 IP核文档- 了解IP核具体的时钟和SYSREF配置要求。

设计JESD204B系统时,时钟质量是成功的第一要素,必须从芯片选型和PCB布局阶段就给予最高优先级的重视。

-

FPGA

+关注

关注

1663文章

22493浏览量

638939 -

接口

+关注

关注

33文章

9588浏览量

157592 -

时钟输入

+关注

关注

0文章

8浏览量

2111

原文标题:FPGA的时钟输入和JESD204B 接口对时钟的要求

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Xilinx FPGA中的混合模式时钟管理器MMCME2_ADV详解

高速时钟设计利器:AD9520 - 5全方位剖析

深入剖析AD9512:高性能时钟分配IC的卓越之选

浅谈高精度晶振与铷原子时钟的区别

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

基于FPGA的高效除法器设计

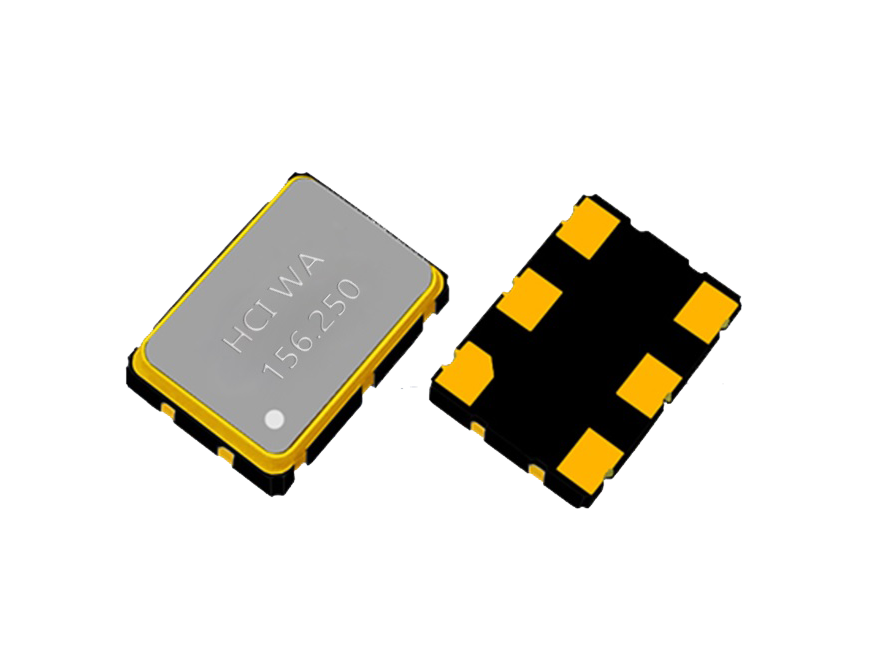

CDCLVP111-SP 低电压1:10 LVPECL可选择性输入时钟驱动器技术文档总结

AMD FPGA异步模式与同步模式的对比

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

FPGA时序约束之设置时钟组

浅谈FPGA的时钟输入要求

浅谈FPGA的时钟输入要求

评论