了解在启用PIPE模式的情况下创建PCI Express IP设计的过程,以便可以使用Mentor Graphics Questa Verification IP(QVIP)进行模拟。 PIPE模式模拟通过移除tra来大大加快模拟时间

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1797浏览量

133134 -

IP

+关注

关注

5文章

1849浏览量

154892 -

PIC

+关注

关注

8文章

511浏览量

90425

发布评论请先 登录

相关推荐

热点推荐

Xilinx FPGA串行通信协议介绍

Xilinx FPGA因其高性能和低延迟,常用于串行通信接口设计。本文深入分析了Aurora、PCI Express和Serial RapidIO这三种在Xilinx系统设计中关键的串行通信协议。介绍了它们的特性、优势和应用场景

【产品介绍】Modelsim:HDL语言仿真软件

仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

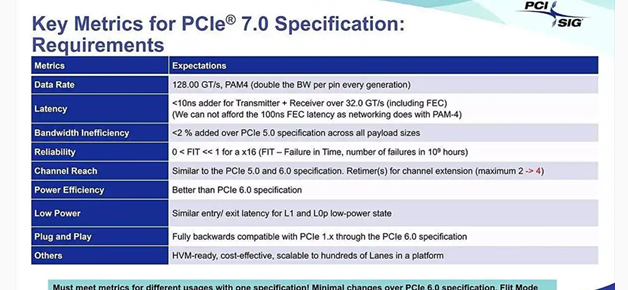

PCIe 7.0技术细节曝光

6 月 11 日 PCI SIG官宣 PCI Express 7.0(PCIe 7.0)规范最终版已制定完毕,但几乎没有公开任何技术细节。不过,在 7 月 16 日,PCI-SIG 通

简仪科技推出PXIe-3171 PXI Express嵌入式控制器

PXIe-3171配备集成的PCI Express交换机,支持四个x4或两个x8的PXI Express配置,通过PCI Express 3

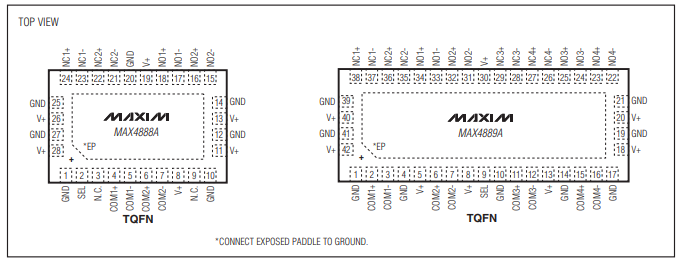

MAX4888A/MAX4889A 5.0Gbps PCI Express无源开关技术手册

MAX4888A/MAX4889A高速无源开关用于在两个接收端之间切换PCI Express® (PCIe)数据。MAX4888A是四路单刀/双掷(4 x SPDT)开关,非常适合在两个接收端之间

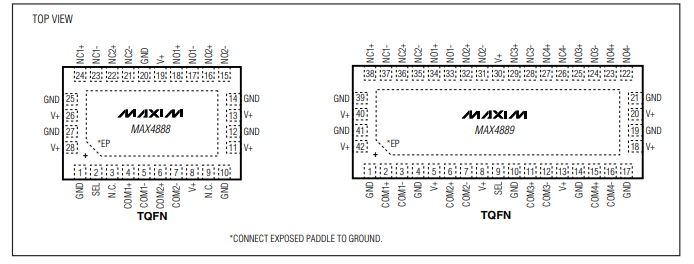

MAX4888/MAX4889 2.5Gbps PCI Express无源开关技术手册

MAX4888/MAX4889高速无源开关可在两个接收端之间切换PCI Express® (PCIe)数据。MAX4888是四路单刀/双掷(4 x SPDT)开关,非常适合在两个接收端之间切换2路

QDMA Subsystem for PCI Express v5.0产品指南

AMD QDMA Subsystem for PCI Express( PCIe )旨在利用多队列的概念实现高性能 DMA,以搭配 PCI Express Integrated Blo

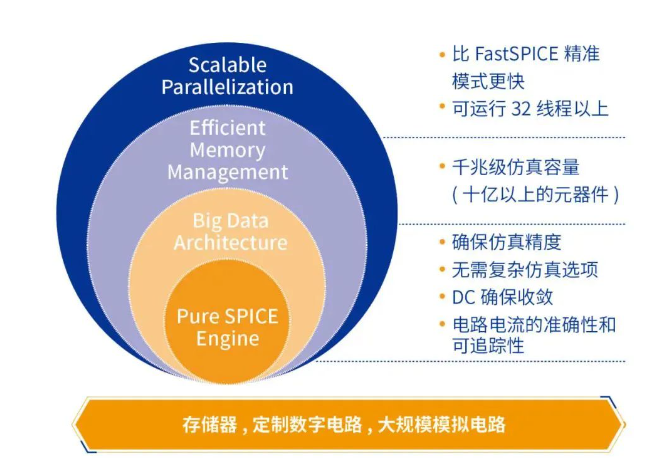

概伦电子千兆级高精度电路仿真器NanoSpice Giga介绍

。NanoSpiceGiga采用TrueSPICE精度级仿真引擎确保了先进工艺节点下芯片设计中功耗、漏电、时序、噪声等的精度要求,并通过先进的并行仿真技术在不降低仿真精度的情况下实现高速电路仿

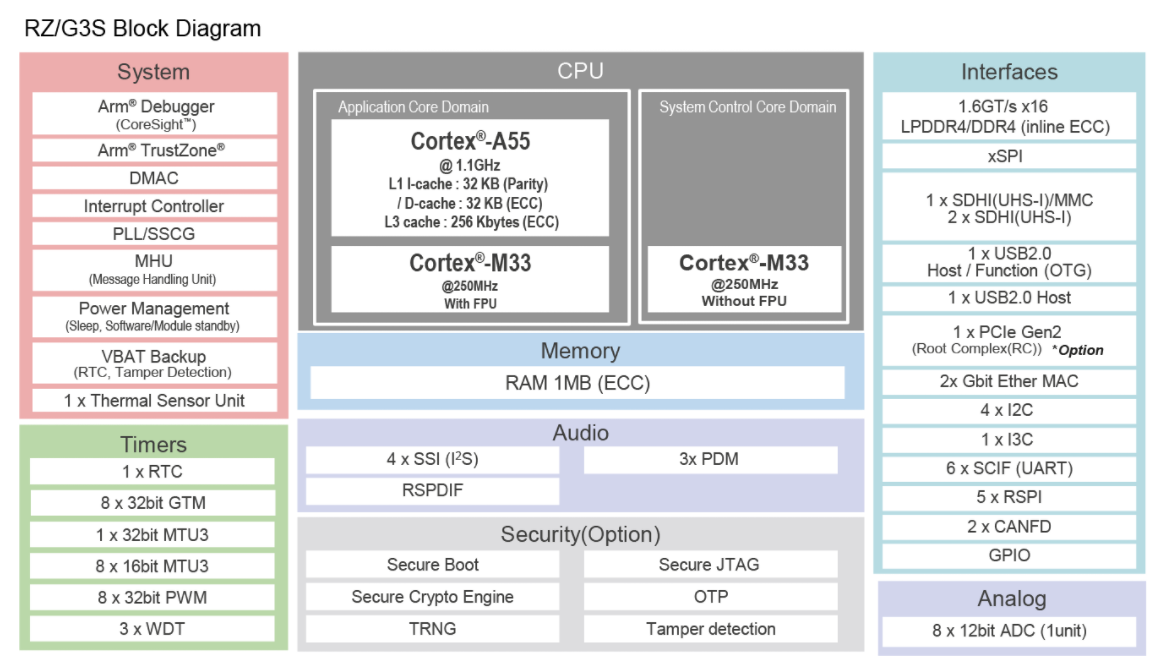

支持低功耗模式和 PCI Express的通用微处理器RZ/G3S数据手册

的基本软件。 *附件:支持低功耗模式和 PCI Express的通用微处理器RZ G3S数据手册.pdf 特性 Cortex-A55 Cortex-M33(双核或单核)(其中一个 Cortex®-M33 具

博世GTM IP模块架构介绍

上篇文章我们介绍了博世GTM IP模块的核心功能及基础结构模块。本篇文章将继续解析GTM模块架构,重点介绍I/O模块,特殊功能模块及内核模块。这些模块不仅增强了GTM的信号处理能力,还极大提升了系统的灵活性和集成度,能够满足汽车

PCI Express Gen5自动化多通道测试方案

对高速链路(如PCI Express)的全面表征需要对被测链路的发送端(Tx)和接收端(Rx)进行多差分通道的测量。由于需要在不同通道之间进行同轴连接的物理切换,这对于完全自动化的测试环境来说是一个

PCI Express IP设计的过程与仿真介绍

PCI Express IP设计的过程与仿真介绍

评论