ICHEC讨论了FPGA对HPC应用的适用性,并重点介绍了能够利用特定FPGA上所有DSP的器件的最佳数据模式。

Virtex®-7 FPGA 针对 28nm 系统性能与集成进行了优化,可为您的设计带来业界最佳的功耗性能比架构、DSP 性能以及 I/O 带宽。 该系列可用于 10G 至 100G 联网、便携式雷达以及 ASIC 原型设计等各种应用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

561文章

8277浏览量

368376 -

FPGA

+关注

关注

1664文章

22508浏览量

639431 -

赛灵思

+关注

关注

33文章

1798浏览量

133671

发布评论请先 登录

相关推荐

热点推荐

ISL8126EVAL1Z评估板:双相单输出应用的性能演示

ISL8126EVAL1Z评估板:双相单输出应用的性能演示 在电子设计领域,电源管理模块的性能评估至关重要。ISL8126EVAL1Z评估板作为一款用于双相单输出应用性能演示的工具,为工程师们提供了

浅谈FPGA的时钟输入要求

Virtex-7 FPGA的时钟输入主要通过其全局时钟缓冲器(BUFG、BUFH等)和时钟管理模块(MMCM、PLL)来处理。对输入时钟的要求主要围绕电气特性、抖动和引脚分配。

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

IDELAYCTRL 是 Xilinx FPGA(特别是支持高速 I/O 的系列,如 Virtex-5/6/7、Kintex-7、Artix-7

【VPX610】基于6U VPX总线架构的高性能实时信号处理平台

板卡概述VPX610是一款基于6UVPX架构的高性能实时信号处理平台,该平台采用2片TI的KeyStone系列多核DSPTMS320C6678作为主处理单元,采用1片Xilinx的Virtex

FPGA DSP模块使用中的十大关键陷阱

FPGA 芯片中DSP(数字信号处理)硬核是高性能计算的核心资源,但使用不当会引入隐蔽性极强的“坑”。这些坑不仅影响性能和精度,甚至会导致功能错误。以下是总结了十大关键陷阱及其解决方案

基于DSP与FPGA异构架构的高性能伺服控制系统设计

DSP+FPGA架构在伺服控制模块中的应用,成功解决了高性能伺服系统对实时性、精度和复杂度的多重需求。通过合理的功能划分,DSP专注于复杂算法和上层控制,FPGA处理高速硬件任务,两者

DSP、FPGA之间SRIO通信的问题?

目前在使用DSP和FPGA之间通过SRIO的SWRITE事务完成双向数据通信,大多数情况下都正常,但是在我不停的给DSP进行烧写程序时,会偶尔出错,

发表于 11-15 16:22

NVMe高速传输之摆脱XDMA设计43:如何上板验证?

Virtex-7 FPGA Gen3 PCIE 集成块和 UltraScale+ Gen4 PCIE集成块, 为证明 NoP 逻辑加速引擎对不同版本硬核的适配性, 硬件平台将在 VC709FPGA 开发板

发表于 10-30 18:10

Altera Agilex 3 FPGA和SoC产品家族的性能分析

本文采用严谨的基准测试方法,对全新推出的 Agilex 3 FPGA 和 SoC 产品家族进行性能分析。该系列专为成本优化型应用设计,兼具高性能

【TES600G】青翼凌云科技基于JFM7K325T FPGA+FT-M6678 DSP的全国产化信号处理平台

产品概述TES600G是一款基于FPGA+DSP协同处理架构的通用高性能实时信号处理平台,该平台采用1片国防科大的银河飞腾多核浮点/定点DSPFT-M6678作为主处理单元,采用1片

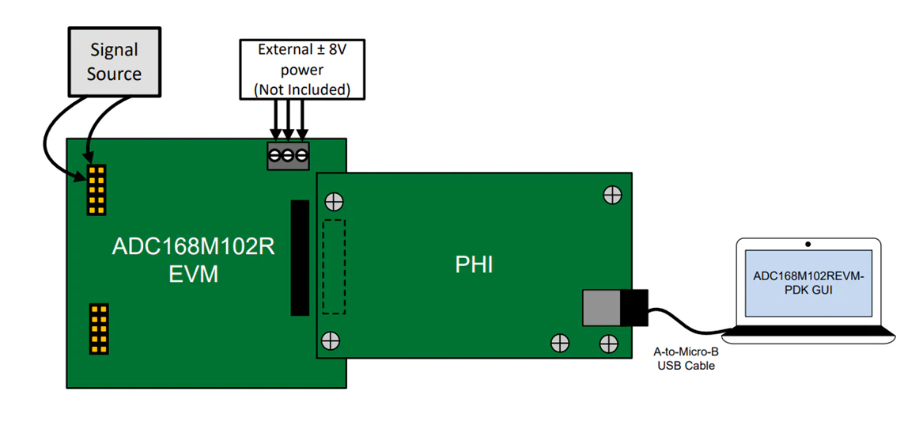

Texas Instruments ADC168M102REVM-PDK性能演示套件数据手册

Texas Instruments ADC168M102REVM-PDK性能演示套件 (PDK) 用于评估16位、8通道1MSPS同步采样模数转换器 (ADC) ADC168M102R-SEP

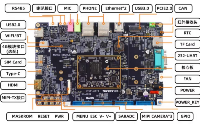

中科亿海微SoM模组——FPGA+DSP核心板

FPGA+DSP核心板是基于中科亿海微EQ6HL130型FPGA芯片搭配国产DSP开发的高性能核心板卡。对外接口采取邮票孔连接方式,可以极大提高信号传输质量和焊接后的机械强度。核心板卡

采用Virtex-7 FPGA进行DSP性能演示

采用Virtex-7 FPGA进行DSP性能演示

评论