1、画定布线区域距PCB板边≤1mm的区域内,以及安装孔周围1mm内,禁止布线;

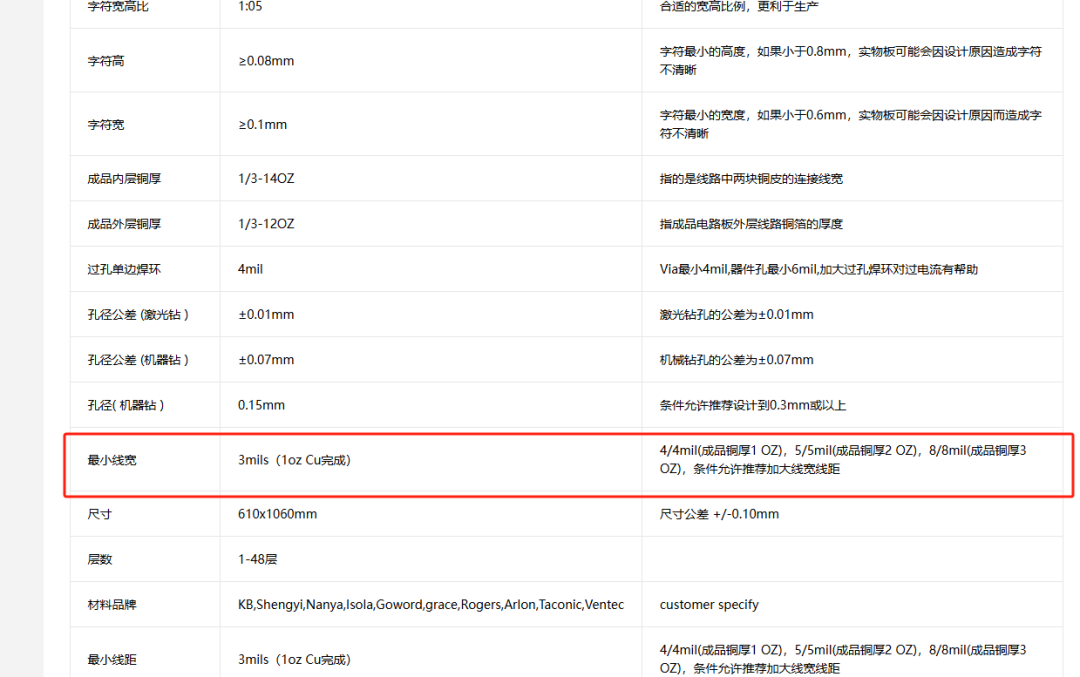

2、电源线尽可能的宽,不应低于18mil;信号线宽不应低于12mil;cpu入出线不应低于10mil(或8mil);线间距不低于10mil;

3、正常过孔不低于30mil;

4、 双列直插:焊盘60mil,孔径40mil;

1/4W电阻: 51*55mil(0805表贴);直插时焊盘62mil,孔径42mil;

无极电容: 51*55mil(0805表贴);直插时焊盘50mil,孔径28mil;

5、 注意电源线与地线应尽可能呈放射状,以及信号线不能出现回环走线。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4417文章

23962浏览量

426105 -

元器件

+关注

关注

113文章

5042浏览量

100302

发布评论请先 登录

相关推荐

热点推荐

PLC和变频器布线规范

要求: 核心布线规范:信号与动力分离 这是最关键的原则,必须严格遵守: 保持物理距离 :控制信号线(特别是模拟量)必须与动力线(主回路)分开走线,间距至少 30cm 。控制柜内也同样适用。 走线方式 :强弱电应分层分区布置,避免长距离

技术资讯 I PCB设计三大顽疾:规则乱、布线慢、叠层偏——Allegro X Designer 的系统级解法

在高速、高密度的PCB设计项目中,工程师的设计早已迈入了另外一个台阶——从“连通即可”的基础要求,跃迁至以规则驱动、以仿真验证、以工艺为导向的精密设计时代。本文基于AllegroXDesigner

PCB元器件推力测试怎么做?推拉力测试机厂家实拍测试操作流程

最近,我们接待了一位做PCB元器件制造的客户,他们遇到了一个棘手的质量问题:同样是0201规格的贴片,在不同批次的电路板上表现出的焊接强度差异很大,有的轻轻一碰就掉,有的怎么推都推不掉。客户想知道

【「Altium Designer 25 电路设计精进实践」阅读体验】+第六章节 PCB设计

一放,在布局好了之后,布线的时候再设置也不迟

放置器件,可以放在配置规则前面

三、布线

这前面可以先把快捷键设置下,方便自己快速有限的布线

发表于 02-26 11:05

PCB中常用的快捷键

● M + M 移动元器件

● S + L 两次左键,选中多条线同时走线

● 拖动器件 + L 元器件顶层、底层快速切换

● T + U 删除全部布线(all)

● J + C在

发表于 01-30 06:01

PCB外观品质标准判定规则

PCB对PCB长、宽均按照±0.15mm管控。

V-CUT余厚公差:

若无特殊要求,华秋PCB按照板厚的1/3、公差±0.1mm管控,上下刀对位精度±0.1mm。

2、板翘

对于用于表面贴装

发表于 01-29 14:39

为了减少电磁干扰,装置在硬件设计时应该遵循哪些原则?

在硬件设计阶段减少电磁干扰(EMI)对电能质量在线监测装置的影响,需遵循 “ 源头抑制、路径阻断、敏感防护 ” 三大核心逻辑,覆盖元器件选型、电路拓扑、信号隔离、滤波设计、接地布局、PCB 设计等全

怎么找出PCB光电元器件失效问题

在电子信息产品中,PCB作为元器件的载体与电路信号传输的关键枢纽,其质量与可靠性对整机设备起着决定性作用。随着产品小型化及环保要求的提升,PCB正向高密度、高Tg和环保方向发展。然而,受成本和技术

PCB特殊元器件布局策略

在高速PCB设计中,特殊元器件的布局直接影响信号完整性、散热性能及制造可行性。本文结合行业实践与工程案例,系统阐述高频、高压、重型、热敏及可调元器件的布局规范与优化方法。 一、高频元器件

时源芯微 PCB 布线规则详解

PCB 布线规则详解 走线方向控制规则 相邻布线层的走线方向应采用正交结构,避免不同信号线在相邻层沿同一方向走线,以此降低不必要的层间串扰。若因 P

高层数层叠结构PCB的布线策略

高层数 PCB 的布线策略丰富多样,具体取决于 PCB 的功能。这类电路板可能涉及多种不同类型的信号,从低速数字接口到具有不同信号完整性要求的多个高速数字接口。从布线规划和为各接口分配

如何布线才能降低MDDESD风险?PCB布局的抗干扰设计技巧

在现代电子产品日益集成化、小型化的趋势下,MDDESD(静电二极管)防护设计变得至关重要。除了元器件选型,PCB的布线与布局也是影响ESD抗扰性能的关键因素。作为FAE,本文将结合实战经验,分享一些

PCB元器件应该遵循哪些布线规则

PCB元器件应该遵循哪些布线规则

评论