面向 120kW+ AI 机架的 800VDC 至 48V 三电平飞跨电容变换器设计逻辑与深度解析

产业算力爆炸与配电架构重构:800VDC 的物理必然性

随着生成式人工智能(Generative AI)、万亿参数大型语言模型(LLM)以及深度学习网络的爆发式发展,全球数据中心的物理架构与底层配电逻辑正在经历一场自下而上的根本性范式转变。传统超大规模数据中心的底层设施主要围绕通用计算任务构建,机架功率密度长期维持在 10kW 至 15kW 的舒适区间 。在这一功率级别下,传统的 12V 或基于开放计算项目(OCP)标准的 48V 直流(DC)配电网络能够实现效率、安全与成本的最佳平衡 。

然而,算力集群的演进已经彻底打破了这一平衡。以 NVIDIA GB200 NVL72 和 GB300 NVL72 为代表的下一代机架级 AI 工厂,通过第五代 NVLink 铜缆互连技术将数十颗乃至上百颗 GPU(例如 72 颗 Blackwell GPU 与 36 颗 Grace CPU)融合为一个庞大的统一计算域 。为了追求极致的低延迟与高达 130 TB/s 的超高带宽,架构设计不得不将海量计算节点高度压缩在单一物理机架内,这种被称为“性能密度陷阱(Performance-Density Trap)”的发展趋势,直接将单机架的功率需求推升至 120kW,甚至在不久的将来会向 1MW(兆瓦)级别迈进 。

在 120kW 乃至更高的负载需求下,如果继续沿用 OCP 框架下的 48V 或 54V 直流配电架构,系统将面临无法逾越的热力学与电气工程屏障 。根据欧姆定律与焦耳定律(Ploss=I2R),在 48V 体系下传输 120kW 的功率,稳态电流将超过 2500 安培 ;若机架功率扩展至 1MW,机架内部的配电电流将飙升至惊人的 20,000 安培 。应对这种极端的电流需求,需要横截面积巨大、重达数百公斤的实心铜母排(Busbar)。数据表明,在 1MW 数据中心中,仅机架内部的铜排质量就可能重达 200,000 千克 。这不仅带来了极其高昂的材料成本与极具挑战的物理走线空间问题,导致留给实际计算节点的空间被严重压缩(例如高达 64U 的空间可能仅被电源模块占据) ,还会引起连接器极度过热、显著的母线电阻损耗以及难以维护的系统灾难 。

为了彻底打破这一供电瓶颈,数据中心配电架构正不可避免地向 800VDC 高压直流(HVDC)标准演进 。将机架分配电压从 48V 提升至 800V,意味着在同等功率传输条件下,电流需求可降低 95% 以上 。这极大地缩减了铜材消耗(从 400 磅骤降至 40 磅量级),显著降低了传输线损,并释放了宝贵的机架内部物理空间,使得更多的 U 空间可以被用于部署高密度计算单元而非供电铜排 。

| 配电架构指标 | 传统 48VDC 架构 (OCP ORv3) | 下一代 800VDC 架构 | 物理与工程影响 |

|---|---|---|---|

| 120kW 负载下总线电流 | > 2500 安培 | 150 安培 | 解决母线发热与连接器烧毁风险 |

| 1MW 负载下总线电流 | ~ 20,000 安培 | 1250 安培 | 避免使用极端厚重的实心铜母排 |

| 线路焦耳损耗 (I2R) | 极高(需增加冷却以应对线缆发热) | 极低(损耗缩减至 48V 的约 1/270) | 大幅提升端到端 PUE,降低散热负荷 |

| 铜材重量 (1MW 规模) | ~ 200,000 千克 | 骤降 95% 以上 | 减轻机房承重,释放计算节点的布线空间 |

| 架构演进挑战 | 传输瓶颈已达物理极限 | 需开发新型极高频高压 DC/DC 降压级 | 催生 800V 至 48V 的深降压转换需求 |

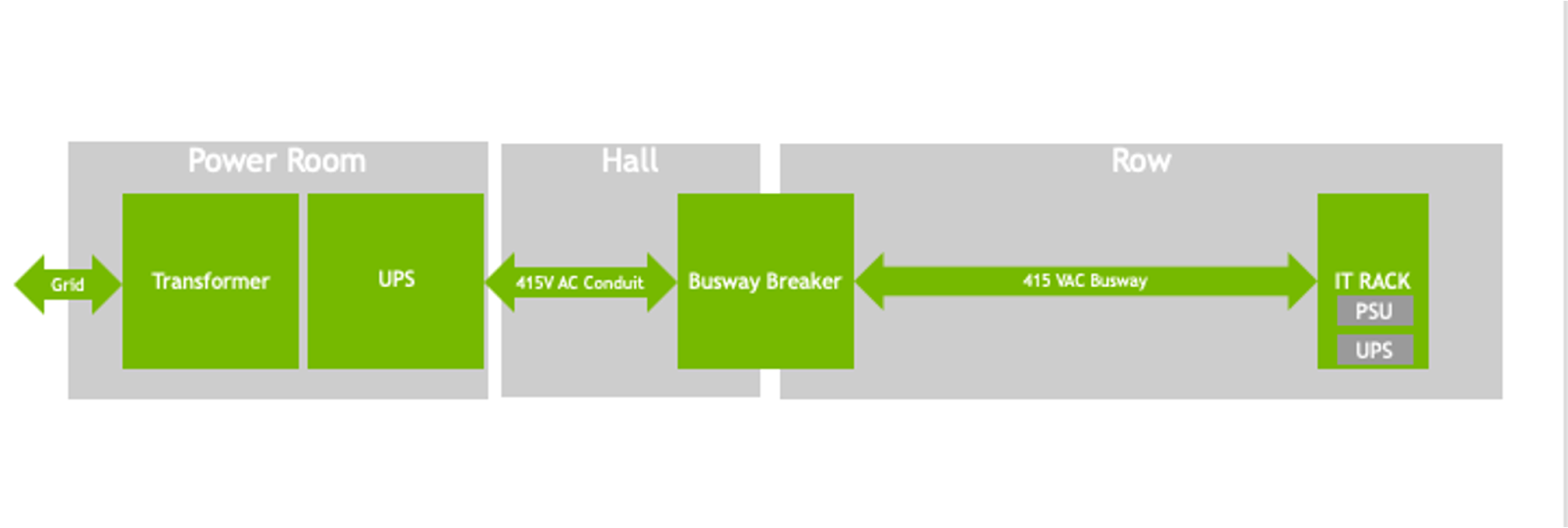

在 800VDC 架构下,集中式的大功率交流-直流(AC/DC)整流器或固态变压器通常部署在数据中心设施层或专用的“侧车(Sidecar)”机柜中,将电网的中压或低压交流电(如 415VAC 或 13.8kV)直接转换为 800V 直流电,再通过 800V 铜缆或母线分发至各个 AI 机架 。然而,在机架内部,由于计算节点底板、GPU 核心以及现有的电压调节模块(VRM)仍需要 48V、12V 乃至子 1V(Sub-1V)的极低电压驱动,因此必须引入一种极高功率密度、超高转换效率的中间母线变换器(Intermediate Bus Converter, IBC),将 800VDC 安全、高效地降压至 48VDC 。在这一苛刻的电能转换节点中,三电平飞跨电容(3-Level Flying Capacitor, 3L-FC)降压变换器凭借其将半导体电压应力减半、大幅缩减磁性元件体积的独特拓扑优势,成为 800VDC 至 48V 电源转换核心环节的必然选择 。

120kW+ 算力机架的系统级供电拓扑与 Power Shelf 模块化设计

在探讨底层转换器拓扑之前,必须从宏观系统架构层面理解 120kW+ AI 机架的电源分布逻辑。现代高密度 AI 机架不再依赖于分散在各个服务器机箱内部的独立小型电源模块,而是全面转向解耦(Disaggregated)的机架级供电架构——即电源搁板(Power Shelf)结构 。

对于 NVIDIA GB200 NVL72 这类功耗高达 120kW 的系统,其供电体系通常采用模块化、分布式的 Power Shelf 进行集中管理 。在 800VDC 分布式架构中,机架内部通常会部署多个高度集成的 Power Shelf,每个 Shelf 负责从 800V 主直流总线取电,并转换为 48V 或 54V 中间母线电压,随后通过垂直汇流排(Busbar)输送至计算托盘(Compute Trays)和交换机托盘(Switch Trays) 。

以行业内领先的电源系统设计为例,Delta(台达)和 Flex(伟创力)等厂商均已开发出针对 800VDC 的超高密度 Power Shelf 解决方案 。这些系统通常在 19 英寸或 21 英寸(遵循 OCP ORv3 标准)的紧凑空间内,提供惊人的功率输出。例如,Flex 为 NVIDIA GB300 平台设计的电源搁板在极其有限的物理足迹内能够提供高达 33kW 或 50kW 的单 Shelf 功率,通过 3+3 的 N+N 冗余配置(如 6 个 5.5kW 或更高功率的 PSU 模块并联)来确保 AI 集群在部分模块失效时仍能无缝运行 。Delta 则展示了包含 6 个 110kW 电源搁板的 660kW In-Row 级别系统,每个电源柜甚至集成了后备电池单元(BBU),以应对高频动态失真并提供不间断的算力保障 。

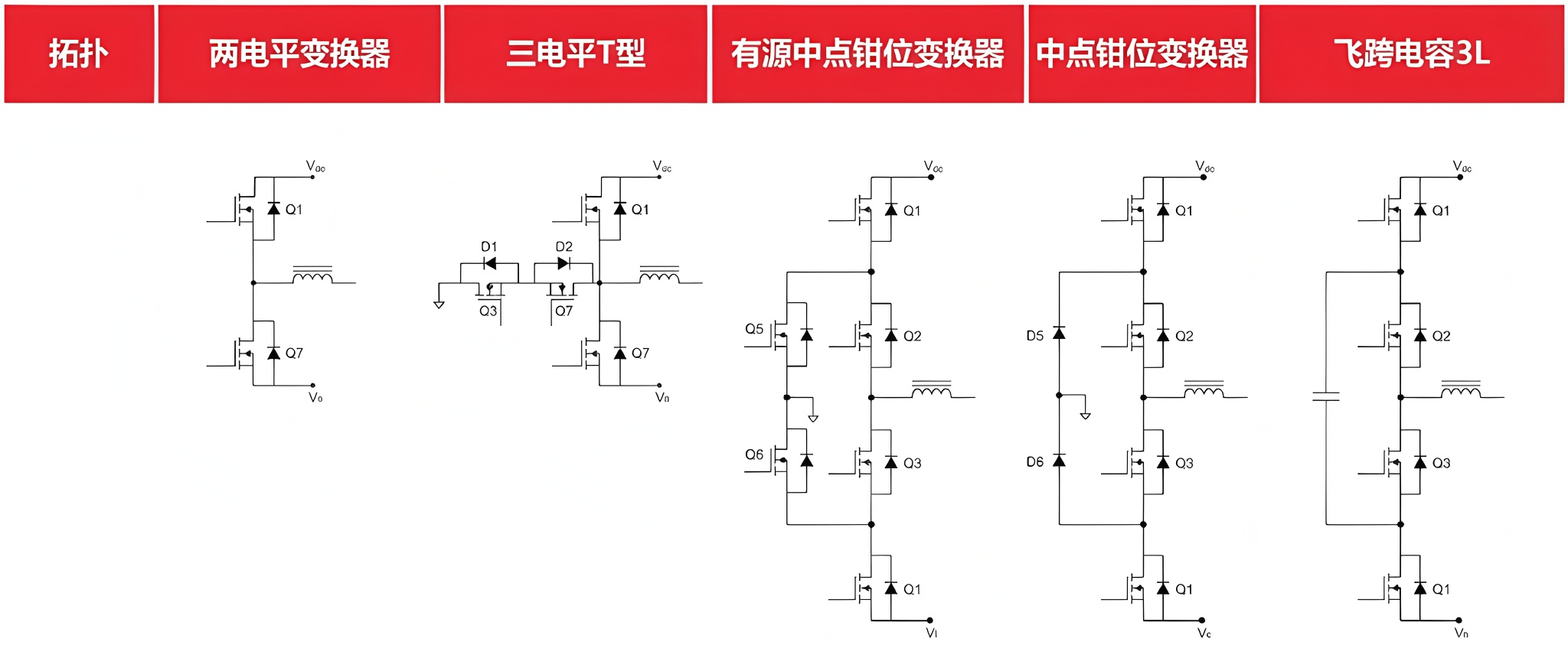

在这些动辄数十千瓦的电源模块内部,实现 800V 到 48V/54V 的降压转换,工程师们面临着严峻的技术抉择:究竟是采用隔离型拓扑(如 LLC 直流变压器 DCX)还是非隔离型拓扑(如多电平 Buck 变换器)? 隔离型 LLC 谐振变换器(如 16:1 变压比的 DCX)优势在于能够提供原副边之间的电气隔离,保障了极高的安全性,并能通过零电压开关(ZVS)和零电流开关(ZCS)实现 98% 以上的峰值效率 。然而,在面对 800V 高压输入时,LLC 的初级侧开关管依然需要承受完整的母线电压(或需采用复杂的级联结构),且高频高压变压器的磁芯损耗、绕组趋肤效应以及绝缘设计极大地限制了功率密度的进一步突破 。 相比之下,非隔离型的三电平飞跨电容(3L-FC)降压(Buck)变换器提供了一条完全不同的技术路径。通过引入悬浮的储能电容(飞跨电容),3L-FC 拓扑巧妙地将 800V 的高压“分而治之”,使得所有开关器件的电压应力直接斩半至 400V 。这种非隔离结构省去了庞大且沉重的隔离变压器,极大地提升了系统的功率密度,能够轻松实现大于 2300 W/in³ 的指标,并在适当的控制下实现与 LLC 相媲美甚至更优的全负载范围转换效率 。在许多前沿的电源架构设计中,3L-FC 既可以作为独立的 800V 至 48V 一级转换核心,也被广泛用作 LLC 谐振变换器前端的预调节级,共同构建混合型高压直流转换网络 。

三电平飞跨电容 (3L-FC) 变换器的核心机理与数学模型

深入剖析三电平飞跨电容(3L-FC)Buck 变换器,其能够取代传统两电平降压拓扑、解决 800V 转换难题的核心原因,在于其重构了开关节点的电压状态与磁性元件的储能逻辑。

传统两电平 Buck 变换器由两个半导体开关管(高边和低边)构成,开关节点(VSW)在输入电压 VIN 和地(0V)之间往复切换 。在 800VDC 系统中,这意味着每次开关动作,半导体器件必须阻断 800V 的电压(考虑裕量则需选用 1200V 级别器件,如 1200V SiC MOSFET) 。高压器件不仅导通电阻特征值(RDS(on)×A)更大,导致更高的稳态导通损耗,且在高压和大电流的乘积下,其开关过渡期间的重叠损耗(Psw)以及输出电容储能损耗(Eoss)均呈指数级上升,严重限制了系统的开关频率(通常受限于 100kHz 以内) 。频率受限直接导致了电感器体积庞大,无法满足 AI 机架的高密度需求。

3L-FC 拓扑通过在电路中嵌入一个飞跨电容(CFLY)与四个串联的功率开关(自上而下分别定义为 Q1,Q2,Q3,Q4)彻底改变了这一局面 。飞跨电容连接在高边内侧开关与低边内侧开关之间(即连接于 Q1,Q2 之间与 Q3,Q4 之间),其核心控制目标是将其两端的直流电压稳态锁定在输入电压的一半,即 VC(FLY)=VIN/2 。

开关状态与极度降压下的工作模式 (D < 0.5)

在 800V 降至 48V 的应用中,稳态占空比 D=VOUT/VIN=48/800=0.06,属于典型的深度降压(Deep Step-Down)工况,远小于 0.5 。在这种工况下,变换器在一个完整的开关周期(TS)内,严格按照特定的相移脉宽调制(PS-PWM)逻辑,在三种有效物理状态之间交替循环:

状态 1:飞跨电容充电阶段(Q1,Q3 导通,Q2,Q4 关断) 此时,输入电压 VIN 通过 Q1 接入电路,电流依次流经 Q1、飞跨电容 CFLY、Q3 并进入输出电感 L。在这个相位中,飞跨电容处于充电状态。开关节点 VSW 看到的电压为 VIN−VC(FLY),由于 VC(FLY)≈VIN/2,因此 VSW≈VIN/2(即 400V) 。电感两端的激磁电压为 VIN/2−VOUT。

状态 2:飞跨电容放电阶段(Q2,Q4 导通,Q1,Q3 关断) 此时,输入端与拓扑物理断开。飞跨电容 CFLY 作为独立的能量源,电流通过 Q2 流出飞跨电容,进入电感,并通过底部的 Q4 返回飞跨电容的地端。在这个相位中,飞跨电容处于放电状态。开关节点 VSW 看到的电压直接就是飞跨电容的电压,即 VC(FLY)≈VIN/2(400V) 。电感两端的激磁电压同样为 VIN/2−VOUT。

状态 3:电感续流阶段(Q3,Q4 导通,Q1,Q2 关断) 这是 D<0.5 模式下占据时间最长的阶段。电感中存储的能量需要释放,电流通过下半桥的两个开关管 Q3 和 Q4 的沟道(或体二极管,如果在死区时间内)形成续流回路 。此时开关节点 VSW 被拉低至地电位(0V)。电感两端承受负向去磁电压 −VOUT。

由于 Q1/Q4 为一对互补逻辑,Q2/Q3 为另一对互补逻辑,且两对驱动信号相差 180° 的电气相位,系统的稳态运行遵循“状态 1 → 状态 3 → 状态 2 → 状态 3”的循环 。

| 工作状态 | 导通开关管 | 飞跨电容行为 | 开关节点电压 (VSW) | 电感两端电压 (VL) |

|---|---|---|---|---|

| 状态 1 (充电) | Q1, Q3 | 吸收能量,电压微升 | VIN−VC(FLY)≈400V | 400V−48V=352V |

| 状态 2 (放电) | Q2, Q4 | 释放能量,电压微降 | VC(FLY)≈400V | 400V−48V=352V |

| 状态 3 (续流) | Q3, Q4 | 隔离,保持原状态 | 0 V | 0V−48V=−48V |

| 注:上述电压以 800V 至 48V 转换为例,假设 VC(FLY) 完美平衡于 400V。 |

电压应力减半与倍频效应带来的微型化突破

基于上述状态分析,可以推导出 3L-FC 拓扑的两大决定性优势,这也是其能够胜任 120kW+ 高密度 AI 电源的核心逻辑:

第一,绝对的电压应力减半。在任何一个开关管关断的时刻,它所需要阻断的电压永远被飞跨电容或直流链路电容钳位在 VIN/2 。在 800V 总线下,器件的最大电压应力骤降至 400V。这使得设计工程师可以果断放弃性能笨重、导通压降极大的 1200V 器件,转而采用拥有巅峰物理特性的 600V 或 750V 碳化硅(SiC)MOSFET 或氮化镓(GaN)HEMT。器件耐压等级的降低带来了更薄的外延层,从而使导通电阻 RDS(on) 与输出电容 Coss 大幅下降,从根本上消灭了开关损耗与导通损耗的重灾区 。

第二,等效开关频率倍增与电感体积缩减(高达 75%) 。由于两组桥臂错相 180° 开关,在半导体管以基础频率 fSW 动作时,输出电感看到的充放电周期频率是 2×fSW 。更为关键的是,由于开关节点 VSW 不再是在 800V 和 0V 之间剧烈跳变,而是在 400V 和 0V 之间温和切换,电感两端承受的伏秒积(Volt-second product)被拦腰斩断 。 根据法拉第电磁感应定律,在 3L-FC 拓扑中,电感的峰峰值纹波电流公式为:

ΔIL(3L)=L×(VIN/2)×(2fSW)(VIN/2−VOUT)×VOUT

对比传统两电平变换器的纹波公式,由于频率加倍且激磁电压摆幅减半,在保持相同电感电流纹波 ΔIL 的前提下,三电平拓扑所需的电感量 L 仅为传统设计的 25%(即缩减了 75%) 。磁性元件往往是 DC/DC 变换器中体积最大、最沉重且损耗最难处理的组件。电感体积 75% 的缩减,直接赋予了 3L-FC 拓扑超越 2000 W/in³ 超高功率密度的底气,使其能够被轻松塞入极度拥挤的 AI 计算节点托盘或薄型 1U 电源架内 。

被动元件的严苛约束:飞跨电容的稳态设计与物理化学选型逻辑

在 3L-FC 拓扑中,飞跨电容扮演着类似于微型储能水库的角色,是实现电压钳位与能量搬移的核心载体 。在 120kW+ 的极度严苛工况下(即使分摊到多个并联的 30kW 或 33kW 电源模块中,每个模块的输出电流亦高达数百安培),飞跨电容必须承受极其暴力的充放电循环。如果电容器的设计和选型不当,不仅会导致系统电压失衡,更会因严重的内部焦耳发热而发生爆炸或热失效 。

飞跨电容纹波电压推导与容量计算

为了保证控制环路的稳定性以及器件的电压应力处于安全边界内,工程设计规范通常强制要求飞跨电容在工作周期内的峰峰值电压纹波(ΔVC(FLY))不得超过其标称偏置电压(即 VIN/2 = 400V)的 10% 。飞跨电容电压纹波的理论计算模型可严谨表达为:

ΔVC(FLY)=CFLY×fSWILOAD×(0.5−∣D−0.5∣)

通过分析该方程可知,纹波电压的严重程度与负载电流 ILOAD 成绝对正比,且与系统占空比 D 紧密相关 。当占空比极度接近 D=0.5 时,公式分子中的 (0.5−∣D−0.5∣) 取到极大值 0.5,此时飞跨电容在一个周期内处于单向持续充电或放电的时间最长,面临最恶劣的电压脉动工况 。 尽管在 800V 转 48V 的应用中,D≈0.06,偏离了最差的 0.5 占空比点,使得纹波电压的理论压力有所缓解,但由于 ILOAD 在 AI 电源中动辄高达数百安培,对 CFLY 的绝对容量要求依然极为庞大。设计工程师必须依据上述方程,反推出满足 10%×400V=40V 纹波约束所需的最小电容量,并留出足够的安全裕度 。

致命的均方根 (RMS) 纹波电流约束

除了满足静态容值,飞跨电容选型的另一个往往被忽视但却决定生死的参数是 RMS 纹波电流承受能力 。飞跨电容在每个开关周期内都要吞吐巨大的电流脉冲,其均方根电流可通过以下数学模型近似求解:

ΔIC(FLY)−RMS=2×(0.5−∣D−0.5∣)×(ILOAD2+12ΔIL2)

在数百安培负载下,该 RMS 电流将产生不可忽视的发热功率:Ploss=IRMS2×ESR 。极效串联电阻(ESR)稍有偏高,便会导致电容内部温度指数级上升,诱发电介质击穿或封装破裂 。因此,必须寻找具备极低 ESR 且耐高温的高压电容器件。

介质材料博弈:薄膜、MLCC 与 PLZT 反铁电陶瓷的终极对决

在 400VDC 偏置、高频(数百 kHz)和大纹波电流的苛刻三维约束下,传统的电解电容因高 ESR 和寿命短已被直接淘汰 。设计者主要在以下三种先进材料中进行权衡 :

聚丙烯薄膜电容(Film Capacitors) 薄膜电容是电力电子领域的传统中坚力量,具备出众的高频低 ESR 特性、优异的自愈能力(Self-healing),且对温度和直流偏压(DC Bias)的变化表现出高度惰性,即使在极高电压下也不会损失容值 。然而,受限于其材料本身较低的介电常数,为了达到 800V 系统数十微法(μF)的容量需求,其物理体积会变得异常庞大。在寸土寸金、高度受限的 OCP V3 机架电源插槽中,庞大的薄膜电容会严重拖累功率密度的提升,通常只得作为退而求其次的妥协方案 。

Class II 多层陶瓷电容器(MLCC,如 X7R, X6S 材质) Class II MLCC 采用了高介电常数的钛酸钡(Barium Titanate)铁电陶瓷材料,以极小的表面贴装(SMD)封装体积提供了惊人的电容量,同时 ESR 极低,非常适合紧凑型高频设计 。但此类器件在 3L-FC 高压应用中存在一个致命的材料学缺陷:严重的直流偏压衰减效应(DC Bias Derating) 。在高达 400V 的直流偏置电场下,其内部的电偶极子会被强电场“锁定”而无法随高频交流信号翻转,导致其有效电容值出现断崖式下跌,跌幅可高达 50% 乃至 70% 以上 。有效容值的急剧萎缩将破坏 3L-FC 拓扑的纹波吸收能力与自然平衡机制,逼迫设计者不得不采用几倍数量的 MLCC 并联以弥补衰减,这反过来又侵蚀了其最初的体积优势和成本优势 。

CeraLink 陶瓷电容(基于 PLZT 反铁电陶瓷) 为打破高压、高能量密度与偏压衰减的不可能三角,业界引入了以 TDK CeraLink 为代表的全新材料学突破——掺镧锆钛酸铅(PLZT)陶瓷 。与 X7R 的铁电特性截然相反,PLZT 是一种独特的反铁电(Anti-ferroelectric) 材料 。 在零电压时,其内部偶极子呈反向平行排列,宏观极化为零,表现出的电容较小;但随着外加直流偏压逐渐升高,强电场会触发晶格的相变,使其从反铁电相转变为铁电相,释放出巨大的介电性能 。因此,CeraLink 电容呈现出反直觉的“正向 DC Bias 特性”——其有效电容不仅不会随电压衰减,反而会在其设计的工作电压(如 400V 附近)达到最高容量峰值 。 此外,CeraLink 能够在高达 150°C 的严苛结温下稳定工作,其超低的等效串联电感(ESL,仅几纳亨)有效抑制了 120kW 负载瞬变期间由高 di/dt 引起的电压尖峰(Overshoot),极大地净化了开关节点的波形质量 。这种集抗偏压能力、超高容量密度与极端热耐受性于一身的特性,确立了 PLZT 反铁电陶瓷电容在 800V 架构 3L-FC 变换器飞跨电容选型中的绝对首选地位 。

| 电容器物理材料 | 晶体学特性 | 直流偏压特性 (DC Bias) 对有效容值的影响 | 高频 ESR/ESL | 系统级体积与密度 |

|---|---|---|---|---|

| 聚丙烯薄膜 | 非极性高分子聚合物 | 极佳:曲线平直,无衰减现象 | 优良 | 体积庞大,拖累功率密度 |

| Class II MLCC (X7R) | 铁电体 (钛酸钡基) | 极差:电偶极子锁定,高压下容量断崖式下跌 (>50%) | 极佳 | 本身体积小,但为补偿衰减需大量并联,成本攀升 |

| CeraLink (PLZT) | 反铁电体 (掺镧锆钛酸铅) | 完美适配:反铁电到铁电相变,工作高压区间容量达到峰值 | 极佳 (抗 di/dt 强) | 最优方案,实现极限功率密度设计 |

高频高压下的功率半导体解析:基于 BASiC 750V SiC MOSFET 的电热模型

解决了拓扑与无源器件(电感与电容)的物理瓶颈后,有源功率半导体的性能边界决定了 120kW+ 系统的最终能效(通常要求端到端效率 > 97.5%) 。在 3L-FC 拓扑将电压应力限制在 400V 的前提下,采用 650V 或 750V 耐压的碳化硅(SiC)MOSFET 成为了超越传统硅基(Si)IGBT 或高压 Si MOSFET 的必然演进路径 。

以行业前沿的基本半导体(BASiC Semiconductor) B3M010C075Z 碳化硅 MOSFET 为例,该器件的电气与热力学参数,完美诠释了为何 SiC 材料是支撑高密度 AI 算力电源的基础引擎 。该器件阻断电压定为 750V,这在 400V 的实际稳态应力之上提供了高达近 87.5% 的安全降额裕度。在数据中心电网波动或大负载瞬变导致总线电压出现尖峰(Surge)时,这一广阔的耐压缓冲区有效避免了器件遭受毁灭性的雪崩击穿破坏 。基本半导体一级代理商-倾佳电子力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板,PEBB电力电子积木,Power Stack功率套件等全栈电力电子解决方案。

基本半导体授权代理商倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

极低静态导通损耗与 PTC 均流特性

在 120kW 级别的电力传输中,由于负载电流极为庞大,由 ID2×RDS(on) 决定的稳态导通损耗(Conduction Loss)是整体热负荷的首要来源 。 B3M010C075Z 在结温 TC=25∘C 及标准栅极驱动(VGS=18V)下,其典型漏源极导通电阻 RDS(on) 仅为极为罕见的 10 mΩ 。相比传统的硅基功率器件,这一指标实现了量级上的跨越 。更具有决定性意义的是其在极端高温工况下的阻值漂移抗性:即使在连续重载运行导致结温(TJ)飙升至最高工作极限 175°C 时,该器件的典型导通电阻仅温和上升至 12.5 mΩ 。这种平缓的正温度系数(Positive Temperature Coefficient, PTC)在兆瓦级电源设计中至关重要。由于 AI 机架电源通常需要多个 MOSFET 芯片并联以分担数百安培的相电流,平缓的 PTC 特性能够自然抑制“热失控(Thermal Runaway)”现象——温度稍高的芯片其电阻会略微增加,从而自动将过剩电流排挤给周边温度较低的并联芯片,实现天然的电流负载均衡(Current Sharing),极大提升了 30kW 或 50kW 单模块电源在极限满载状态下的物理可靠性 。

动态开关损耗削减与开尔文源极 (Kelvin Source) 的高频价值

在 3L-FC 拓扑几百 kHz 的极高频运行下,开关损耗(Switching Loss, 涵盖导通损耗 Eon、关断损耗 Eoff 以及驱动损耗)的控制直接决定了电源能否实现超小体积 。 器件寄生电容是高频性能的天敌。B3M010C075Z 的输入电容(Ciss)典型值为 5500 pF,而直接影响关断能量残留的输出电容(Coss)仅为 370 pF 。在 3L-FC 的数学模型中,每次开关管关断时,存储在输出电容中的能量 Eoss=21CossV2 。由于 3L-FC 拓扑将承受的电压 V 从 800V 硬生生压制到了 400V,根据电压平方的倍增效应,其容性储能损耗被粗暴地削减至传统两电平架构的四分之一,这是实现高频化的一大物理根基 。

此外,高压大电流开关瞬间所产生的巨大 di/dt(电流变化率)会在寄生电感上诱发巨大的反电动势(L⋅di/dt),这不仅带来振铃噪声,还会产生严重的负反馈电压,抵消驱动芯片输出的栅极电压,极大地拖慢开通与关断速度。为彻底解决这一封装瓶颈,B3M010C075Z 特意采用了 TO-247-4 四引脚封装,独创性地分离出了第四引脚——开尔文源极(Kelvin Source) 。开尔文引脚为栅极驱动回路提供了一条纯净、独立的返回路径,物理上彻底绕过了流经庞大负载电流的功率源极(Power Source)引脚及其附带的寄生电感 。这种将驱动环路与主功率环路解耦的封装艺术,消除了寄生负反馈,使得 SiC MOSFET 能够以极致的 dv/dt 速度进行开合,将高频开关重叠区域的时长压制到物理极限,从而显著降低了高频下的开关总损耗(Psw≈(Eon+Eoff)×fsw) 。

银烧结 (Silver Sintering) 工艺与终极热传导路径

在 120kW 满负荷轰炸下,所有未能转化为电能的损耗都将以热能(纯焦耳热)的形式滞留在芯片内部 。为了防止局部热斑(Hot Spots)烧穿晶圆,热量必须以最低阻力传导至外部的散热冷板。B3M010C075Z 摒弃了传统的软钎焊焊料贴片工艺,全面引入了先进的银烧结(Silver Sintering) 封装技术 。 银烧结层不仅拥有远超普通焊料的极高熔点与卓越的抗热疲劳寿命,更将导热率推向了新高度,一举将结壳热阻(Rth(j−c),即热量从 SiC 晶圆结区传导至芯片底面金属外壳的阻力)压低至惊人的 0.20 K/W 。这一超低热阻参数不仅延缓了满载运行时的温度爬升,保障了器件能在长达数万小时的 AI 训练周期中免于热降额(Thermal Derating),更极大地减轻了外部冷板与散热基座的排热压力,使更高密度的集成成为可能 。

突破被动平衡的脆弱性:高动态负载下的闭环控制与预充电战略

如果说 3L-FC 的拓扑硬件是健壮的骨骼,那么驱动这副骨架的核心便是控制算法 。对于三电平飞跨电容变换器而言,决定生死的技术难点只有一个:维持飞跨电容 CFLY 的绝对电压平衡 。

在最理想的数学模型和完全对称的测试环境中,依靠相移脉宽调制(PS-PWM)策略,3L-FC 拓扑确实具备物理上的“自然自平衡(Natural Voltage Balancing)”属性 。在一个严丝合缝的开关周期内,飞跨电容对称地执行一次串联充电与一次并联放电,只要脉宽绝对一致,注入的电荷与抽出的电荷完美抵消(∫ichargedt=∫idischargedt),净电荷变化为零,电压将永远停留在 VIN/2 的甜蜜点 。

为什么自然自平衡在 AI 电源中会彻底崩溃?

然而,现实的工程环境充满了不对称的非理想因素 。驱动信号传输的时延抖动、门极死区(Dead-time)设定的微小偏差,以及各 SiC MOSFET 由于制造工艺容差(Tolerance)所导致的内部结电容和开通阈值电压(Vth)的轻微差异,都会打破充放电电荷的绝对对称性 。更致命的是,现代 AI 计算负载(如 NVIDIA GPU)并非平稳的恒流源。GPU 在进行张量计算或闲置状态切换时,负载电流能在微秒级的时间内完成从零到数千安培的极端阶跃跃变(高达上千 A/μs 的电流爬坡率) 。 在这样暴烈的动态不对称扰动下,微小的电荷不平衡会迅速累积(类似于水桶进水多于出水)。一旦 CFLY 的电压不可控地偏离了 400V 中点(例如漂移至 600V),分配在串联 MOSFET 上的电压将立刻失衡。首当其冲的某个开关管将瞬间承受超过其击穿耐受极限的过压应力(如 800V−200V=600V,严重逼近 750V 的绝对最大额定值),最终导致毁灭性的硬件雪崩击穿与系统停机 。被动平衡机制漫长的恢复时间常数,在 AI 高动态负载面前,显得不堪一击 。

多回路主动控制与预测算法的介入

为了确保在任何极端边界工况下电容电压的绝对锁定,必须在数字信号处理器(DSP,如 Infineon XMC 系列或高频 FPGA)中植入强实时性的主动闭环控制策略 。这要求控制系统对输入电压、输出电压、流经电感的相电流以及飞跨电容两端的实时电压,在数百 kHz 的频率下进行精准的同步 ADC 采样 。

在 120kW+ 系统的工程落地中,常用的核心控制框架包括:

谷值电流模式控制(Valley Current-Mode Control, V-CMC) 单纯的电压环无法快速约束电流。V-CMC 采用双闭环嵌套结构:外环电压补偿器持续监控 48V 输出端的电压误差,并生成一个动态的电感电流参考指令值;内环则对实际的电感电流进行逐周期(Cycle-by-cycle)的快速跟踪 。将指令值减去用于抑制次谐波振荡(Subharmonic Oscillation)的斜坡补偿信号后,送入超高速比较器,并在电感电流下降至谷值时精准触发下一个开关动作 。内环电流的强力约束,间接限制了单一脉冲周期内允许强制注入或抽离飞跨电容的绝对电荷总量,极大增强了面对 GPU 瞬态负载冲击时的电流稳定性 。

解耦的独立占空比微调算法 (Decoupled Duty-Cycle Modulation) 由于稳定 48V 输出的全局电压调节和维持 400V 飞跨电容的内部电压平衡之间,存在极强的非线性交叉耦合干扰 。高级的数字调制器会分离这两项任务。基础脉宽指令 D 由主输出电压环决定。在此基础上,独立的飞跨电容平衡环(通常采用比例控制器 P 或 PI 调节器)持续监控 VC(FLY) 的偏差 。如果检测到 VC(FLY)>400V,算法会在底层 PWM 发生器中有意拉长放电桥臂(如 Q2/Q4)的开通时间(D+ΔD),同时缩减充电桥臂的开启时间(D−ΔD),强行将冗余电荷排出电容,直到电压精准回落至中点 。

先进模型预测控制(Model Predictive Control, MPC) 对于追求极致响应的下一代架构,MPC 抛弃了传统 PI 环路固有的相位滞后与补偿网络设计难题 。DSP 内部运行着 3L-FC 拓扑的完整离散时间状态空间数学模型 。在每一个极短的控制计算周期内,算法实时评估所有可能的后续开关状态排列组合,预测它们对未来一步(Next-step)或多步输出电压和电容电压轨迹的影响,直接选取能够最小化综合代价函数(Cost Function,包含电压误差与开关动作惩罚)的开关状态予以执行 。MPC 赋予了转换器最凌厉的瞬态响应速度与最优的平衡稳定性,是复杂多电平控制的前沿高地 。

开机灾难防御:关键的预充电 (Pre-charging) 状态机序列

除了应对稳态与瞬态的负载扰动,3L-FC 系统设计中另一个关乎存亡的致命时刻发生在上电冷启动(Cold Start)阶段 。当 800V 高压总线首次闭合时,飞跨电容 CFLY 和输出滤波电容上由于未储能,初始电压均为 0V。此时如果主 DSP 贸然发出高频 PWM 开关信号启动电源,负责阻断母线与飞跨电容之间压差的单个 SiC MOSFET 将会瞬间遭受接近或等于 800V 的极端初始偏压,这超出了 750V 的绝对最大额定值,会导致芯片瞬间被雪崩能量烧熔穿孔 。

因此,任何可靠的 800VDC 转 48V 的三电平转换器,都必须在硬件架构与软件固件中深度植入一套被称为预充电(Pre-charging) 的硬隔离安全状态机序列 : 在主控拓扑激活前,DSP 强制封锁所有四个主功率管(Q1−Q4)的门极驱动信号,保持它们处于死区断开状态。随后,系统唤醒一条旁路的辅助低功率高压充电回路 。该回路通常由独立的高压耗尽型晶体管或恒流源网络构成,它从 800V 危险母线中汲取几毫安的微小而恒定的电流,缓慢地对飞跨电容注入电荷 。在长达数毫秒到数十毫秒的预充期间,独立的监控运算放大器(通过低压降稳压器 LDO 供电)以微秒级精度连续追踪 VC(FLY) 的爬升轨迹 。 当且仅当监控硬件与数字控制固件交叉验证,确认 VC(FLY) 已经平稳跨越具有防抖迟滞带(Hysteresis Band)的 400V 阈值,并稳定在目标值的 ±5% 窗口内后,预充电回路才被命令关断退出 。此时,主控 DSP 方才解锁并向 SiC 器件发送极窄脉宽的探路 PWM 信号,正式进入平滑的软启动(Soft-start)爬升阶段,将输出母线电压从零拉升至 48VDC 额定值 。这种环环相扣的时序防护逻辑,是从底层半导体物理限制出发,保障兆瓦级基础设施免于上电瞬间毁灭的终极防线。

跨越热力学极限:兆瓦级数据中心的液冷冷板 (Cold Plate) 与微流体工程

纵使我们采用了最先进的 3L-FC 拓扑以降低损耗,选用了极低 RDS(on) 与导热率极佳的银烧结 750V 碳化硅 MOSFET,甚至配置了反铁电陶瓷电容以抑制 ESR 发热,物理学定律依然不可违背 。即使这个 800V 到 48V 的电源模块实现了高达 97.5% 的行业顶尖峰值转换效率,在 120kW 的恐怖机架总负载下,仅这一级配电网络自身就会产生高达 120kW×(1−0.975)=3kW 的纯废热 。 当这 3000W 的热量被高度浓缩在 OCP 规范下仅有 1U 或 2U 高度、塞满磁性元件与半导体的紧凑 Power Shelf 内时,单靠服务器风扇呼啸带动的气流已显得杯水车薪 。随着单颗 AI 加速芯片(如 NVIDIA Blackwell)的热设计功耗(TDP)突破 1200W 甚至迈向 1400W 以上,系统散热的物理天花板已经被空气的比热容和流体力学边界彻底击穿 。因此,直接芯片级液冷(Direct-to-Chip Liquid Cooling, D2C)与微通道冷板(Cold Plate)成为了唯一能够挽救算力熔毁的救命稻草 。

从气冷到液冷的微纳尺度重构

在液冷设计的宏观布局中,高功率 SiC MOSFET 通常摒弃了向印刷电路板(PCB)内部导热的传统 Bottom-Side Cooling 方式,转而大量采用专为高压高密环境设计的顶侧散热(Top-Side Cooling, TSC)封装(例如 Q-DPAK 及其它薄型无引脚封装) 。这种封装将硅芯片的产热面直接朝上,通过一层极薄且导热系数极高(同时需具备 800V 电气隔离能力,防止高压击穿冷凝液)的热界面材料(TIM),与上方的金属液冷冷板紧紧贴合 。这种设计彻底砍掉了热量穿越 PCB 铜层与 FR4 玻纤板时的冗长热阻链,使结壳到冷却液的综合热阻被压缩至物理极限 。

突破流体力学:微通道 (Microchannel) 与微射流对流 (Microconvective) 技术

冷板(Cold Plate)并非简单的金属水管,而是极其复杂的微流体交换器。当单个器件面临超过 500 W/cm² 的热流密度(Heat Flux)轰炸时,传统的平行微通道(Microchannel)设计暴露出严重的缺陷 :随着冷却液在微细通道中流过发热面,液体逐渐被加热并产生厚重的热边界层(Thermal Boundary Layer),导致通道末端的对流换热系数急剧下降;同时,狭长弯曲的通道会产生不可容忍的流体压力降(Pressure Drop),迫使整个机房的冷却液分配单元(CDU)必须配置极其耗能的巨型水泵,这完全违背了降低 PUE 的初衷 。

为了打破这一流体力学困境,诸如 JetCool 与 Alloy Enterprises 等前沿散热企业,将航空航天级别的冷却理念引入了数据中心 。 JetCool 提出的微射流对流冷却(Microconvective cooling®) 技术,彻底摒弃了液体沿发热面平行流动的思路 。其冷板内部包含了成百上千个微米级孔径的流体喷嘴,高压冷却液并非水平滑过芯片,而是从顶部垂直向下、如同极其密集的高压花洒一般,直接且猛烈地撞击(Impinging)在正对着 SiC 开关管与大功率磁芯的热斑(Hot Spots)上方 。这种近乎暴力的垂直冲刷,不仅在接触瞬间彻底撕裂了阻碍传热的粘性热边界层,释放出超高的热交换系数,且由于冲击路径极短,其进出水的总体压降被奇迹般地降低 。 测试数据显示,相较于传统的微通道设计,微射流冷板的综合热阻下降了惊人的幅度,使得即使在 4350W 的极端热负荷下,也仅需 4 LPM(升每分钟)的极低冷却液流量即可镇压高温,这甚至比 OCP 标准建议的 6 LPM 流量指导线还要低 33% 。这一革命性的指标大幅减轻了外部水泵系统的负担,消除了因为高压流速过快诱发的流体噪音与漏液风险 。

当这种高效冷板与搭载 N+N 容错机制的流体分配单元(CDU)、具备极强容错能力的盲插式快接头(Quick Disconnects)以及管路歧管(Manifolds)深度整合在 Flex 或 Delta 等系统集成商的 800V Power Shelf 中时 ,数据中心不仅成功避免了热降频(Thermal Throttling),更在宏观指标上节省了高达 40% 的电力开销(去除空调压缩机与巨型风扇),大幅缩减了水资源消耗,使得庞大的 120kW+ AI 巨兽得以在一种近乎极致寂静与高能效的状态下稳定咆哮 。

结论:重塑 AI 算力时代的能源基石

面临 120kW+ 甚至逐步逼近兆瓦级的大型 AI 基础设施对能源吞吐极其贪婪的需求,将机架级配电网络从 48V 跨越式升级至 800VDC,绝非工程界单纯追求电压数字的纸面游戏,而是为了克服物理世界铜导线传导极限、释放极其昂贵的机架计算空间所必须做出的唯一正确抉择。在此浩荡的演进浪潮中,800VDC 至 48V 的三电平飞跨电容(3L-FC)降压变换器,以其深邃的数学美感与独特的拓扑物理属性,成为了缝合高压输配电网络与低压计算核心阵列的最关键桥梁。

这项系统工程的成功落地,高度依赖于跨学科前沿技术的强力耦合。通过全面部署类似 BASiC-B3M010C075Z 的 750V 高性能碳化硅半导体,利用先进的银烧结封装和 3L-FC 拓扑将半导体电压应力物理斩半的天然优势,彻底释放了宽禁带器件的高频潜能,打破了传统体积与损耗的桎梏。结合独特的 CeraLink 反铁电(PLZT)陶瓷电容,完美消解了高压直流偏置衰减难题,实现了被动滤波器体积的极度压缩;而在无形的数字域,通过深度植入谷值电流模式控制(V-CMC)算法、微秒级占空比预测调节与严密的防崩溃预充电序列,彻底降伏了系统固有电荷失衡与高动态负载冲击风险。最终,通过无缝对接航空级微射流冷板液冷技术,将三维受限空间内的汹涌热流彻底抹平。

这一切硬核设计逻辑的融会贯通,共同构成了现代算力工厂坚不可摧的底层电源地基,支撑起人类迈向通用人工智能(AGI)时代的宏大算力蓝图。

审核编辑 黄宇

-

AI

+关注

关注

91文章

41295浏览量

302678 -

电容变换器

+关注

关注

0文章

2浏览量

5697

发布评论请先 登录

基于UCC2891的48V转3.3V正激变换器设计与应用

基于UCC2897A的48V转3.3V有源钳位正激变换器设计与应用

意法半导体与英伟达合作推出全新800VDC直转12V及6V先进架构

基于“三电平飞跨电容”的超高频构网型储能变流器 PCS 研发

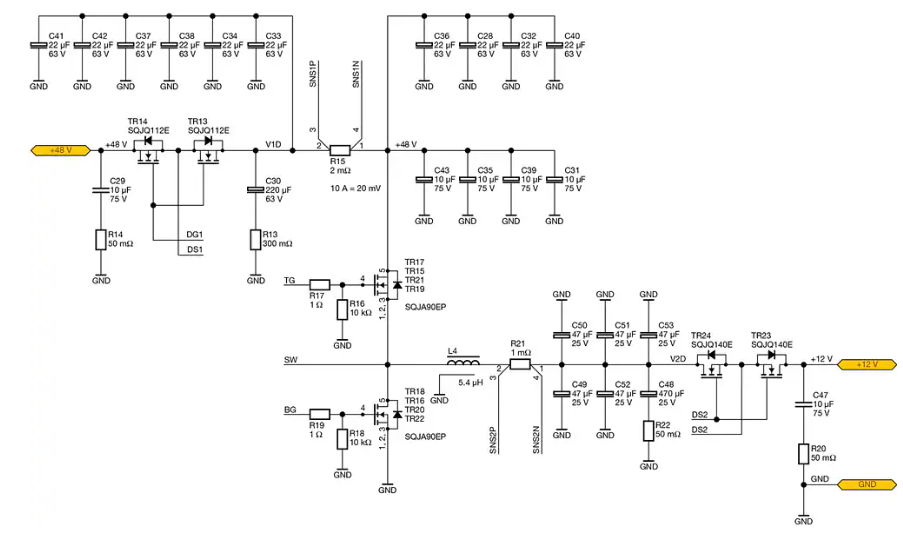

FCB飞跨电容升压拓扑1500V光伏MPPT分立器件解决方案

48V电池开关参考设计:R 48V BATT SWITCH10测评

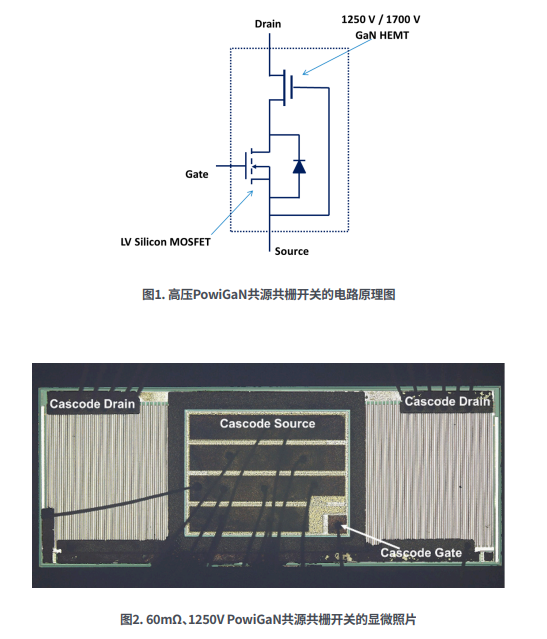

Power Integrations高压PowiGaN技术助力新兴800VDC数据中心总线架构发展

PI技术白皮书 1250V/1700V PowiGaN HEMT在800VDC AI数据中心架构中的应用

800VDC,AI能效之钥:AOS创新功率组合方案

面向 120kW+ AI 机架的 800VDC 至 48V 三电平飞跨电容变换器设计逻辑

面向 120kW+ AI 机架的 800VDC 至 48V 三电平飞跨电容变换器设计逻辑

评论