随着新能源汽车800V高压平台广泛应用,PCB层间耐压要求从常规50V提升至500V-2000V,层间绝缘可靠性成为保障高压电子设备长效稳定运行的核心瓶颈。当前行业普遍将CAF失效管控重点放在材料选型,却忽视图形设计对层间电场分布的调控作用,导致部分高端耐CAF板材产品仍无法通过高压CAF测试。

本文聚焦PCB图形设计与层间高电压CAF测试的内在关联,深入剖析核心图形设计要素对CAF失效的影响机制,打破“材料决定一切”的认知误区,为设计工程师提供从“材料依赖”向“图形主动防御”转型的可落地设计思路,助力提升高压PCB的层间绝缘可靠性,推动高压电子设备的技术升级。

误区澄清:

高电压CAF失效不是“材料问题”,而是“图形问题”

传统中低压CAF失效,主要沿玻纤纱束缓慢漏电,材料界面结合性能是核心因素。但电压达到 500V 及以上高压场景时,失效机理发生本质改变,图形设计影响远超材料选型。

●失效主因迭代:

从“通道形成”转向“电场畸变”。

高压场景下,介质绝缘性能的局部劣化会引发电场集中,形成局部高场强区域,进而加速离子迁移和绝缘击穿,这与传统中低压场景下的渐进式离子迁移有本质区别;即便选用耐CAF性能优异的板材,若图形设计不合理导致电场畸变,仍会触发CAF失效,无法发挥材料的耐CAF优势。

●材料与图形的角色定位

材料是基础,图形是“开关”。

实验数据显示,同一种耐CAF板材在不同图形设计方案下,高压CAF测试通过率相差可达3倍以上。其中,导体间距、线路拐角形态、残铜分布、玻纱取向及过孔阵列排布,已成为决定高压CAF测试成败的关键变量,直接决定了材料耐CAF性能的发挥上限。

四大图形设计要素对层间高压CAF测试的影响

●导体间距:

从“满足最小电气间隙”到“追求电场均匀性”

IPC 标准仅规定不同电压的最小电气间隙,多层板高压层间仅满足最小间距,无法通过 CAF 测试。内层大面积孤立铜块未接地,会形成耦合电容,抬升局部电位差,导致电场超标、介质击穿,触发CAF失效。

设计建议:

严格满足 IPC 最小间距,高压层间间距比标准值提升 20%-30%;

内层孤立铜块必须可靠接地,降低局部电位差,优化电场分布。

●线路拐角:

被忽视的“尖端放电重灾区”

线路拐角是电场集中薄弱区,直角或尖锐拐角会产生尖端效应,电场强度为平滑区域的2-3倍,加剧电场畸变,加速介质劣化和CAF通道的形成。

设计建议:

高压线路优先用圆角,圆角半径≥线路宽度1.5倍;

禁止锐角、直角拐角,蚀刻后充分钝化,降低尖端效应风险。

●过孔阵列:

从“并列排布”到“斜列排布”的降维打击

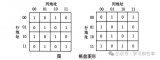

传统过孔并列排布,沿同一玻纤束形成CAF快速导通通道,大幅缩短失效时间。斜列式排布可破坏连续导电路径,增加离子迁移阻力,同等孔距下高压耐受时间提升40%以上。

设计建议:

高压层间过孔阵列采用斜列排布,避免沿玻纤束平行排列;

相邻过孔间距≥过孔直径3倍,控制过孔密度,减少电场耦合。

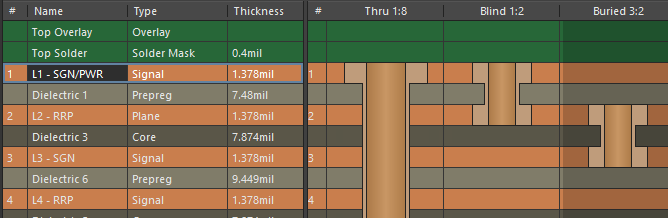

●残铜率与叠构:

被低估的“介质实际厚度”

内层残铜率不均会导致压合后PP填胶不足,介质实际厚度变薄,电场强度超标,引发CAF击穿;玻纤布取向与导体走向平行,会提升离子迁移概率,进一步提升CAF失效风险。

设计建议:

同一内层残铜率波动≤10%,保证均匀性;

高压层间选用薄型PP,确保介质厚度达标;

玻纤布取向与导体走向呈45°夹角,降低离子迁移速率。

高压PCB设计需围绕拉大关键间距、优化孔位排列、管控电场分布、均衡铜箔结构四大核心,从图形设计源头降低CAF风险,保障产品通过严苛的层间高电压可靠性测试。后续我们将结合实际案例,深入验证线路拐角设计对高压测试的具体影响,敬请期待!

-

新能源汽车

+关注

关注

141文章

11458浏览量

105469 -

pcb

+关注

关注

4415文章

23955浏览量

426009 -

电子设备

+关注

关注

2文章

3266浏览量

56231

原文标题:干货分享 | 探析PCB图形设计对层间高电压CAF测试的影响

文章出处:【微信号:SGS半导体服务,微信公众号:SGS半导体服务】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

09. 如何把PCB上的图形快速切换到不同的层? | 芯巧Allegro PCB 设计小诀窍

工程师必看:PCB 6层板打样高品质揭秘

从8层到30层:AI服务器PCB层数进阶,PCle 5.0高速传输需求成关键

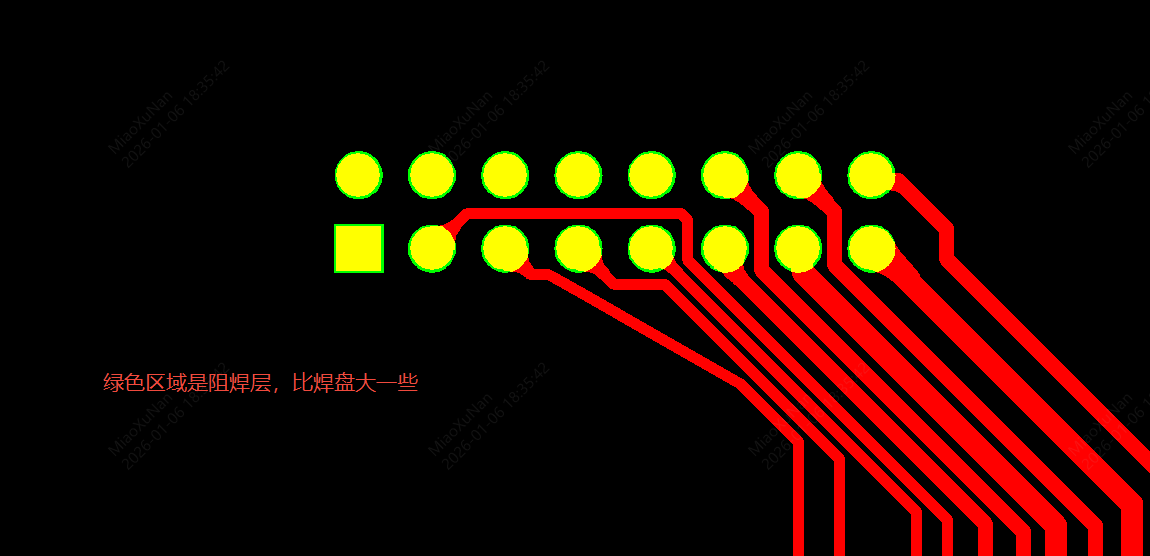

PCB阻焊层与助焊层的本质区别

PCB板ATE测试探针卡设计和生产的核心技术要求,你知道多少?

PCB叠层设计避坑指南

PCB叠层设计避坑指南

Micro OLED 阳极像素定义层制备方法及白光干涉仪在光刻图形的测量

PCB的EMC设计(一):层的设置与排布原则

半导体存储器测试图形技术解析

探析PCB图形设计对层间高电压CAF测试的影响

探析PCB图形设计对层间高电压CAF测试的影响

评论