RZ/V2N Group芯片:功能、特性与设计考量

在当今的电子设计领域,芯片的性能和功能对于产品的成功至关重要。RZ/V2N Group芯片以其丰富的功能和出色的性能,成为众多工程师关注的焦点。本文将详细介绍RZ/V2N Group芯片的特性、引脚、电气特性等方面,为电子工程师在设计过程中提供全面的参考。

文件下载:r01ds0466ej0120-rzv2n.pdf

一、概述

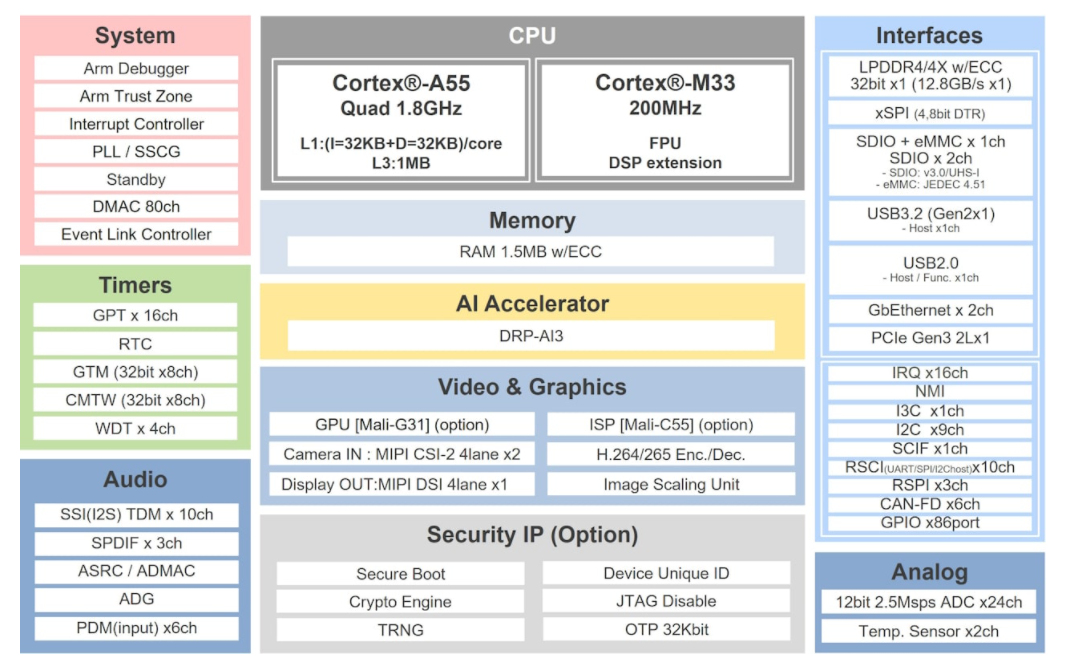

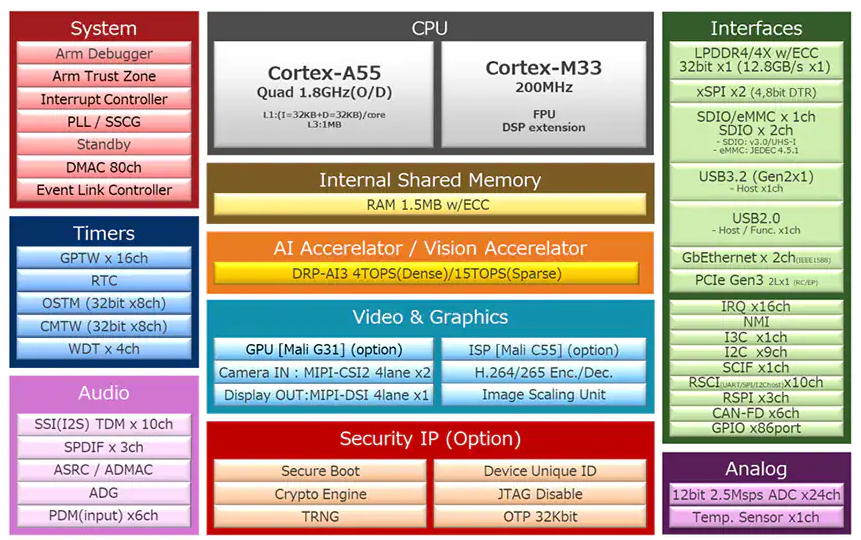

RZ/V2N Group芯片集成了多种强大的功能,包括高性能的CPU、丰富的加速器引擎、多种通信和存储接口等。

(一)产品特性

- CPU:具备1.8 GHz Quad Arm® Cortex® - A55和200MHz Arm® Cortex® - M33处理器。其中,Cortex - A55用于应用处理,最高可达1.8 GHz;Cortex - M33用于系统管理,最高可达200 MHz。这种组合使得芯片能够在高性能计算和系统管理方面实现高效协作。

- 加速器引擎:包含AI加速器(DRP - AI)、3D图形引擎(GE3D)、图像信号处理器(ISP)、图像缩放单元(ISU)和视频编解码器单元(VCD)等。例如,DRP - AI最高可达4 dense TOPS和15 sparse TOPS,为AI计算提供强大的支持。

- 内存接口:拥有1.5 MB的片上SRAM和外部DDR内存接口,支持LPDDR4 - 3200或LPDDR4X - 3200,总线宽度为32位,为数据存储和处理提供了充足的空间和高效的传输速度。

- 通信接口:集成了2ch GbEthernet MAC、1ch USB2.0、USB3.2 Gen 2x1、2 - MIPI® CSI - 2相机输入接口、1 - MIPI® DSI®视频输出接口、PCIE® Gen3 2Lane(EP/RC)等多种接口,满足了不同应用场景下的通信需求。

(二)产品阵容

RZ/V2N Group提供了多种型号的产品,不同型号在3D图形引擎(GE3D)和安全功能等方面有所差异,工程师可以根据具体的应用需求进行选择。

二、引脚说明

(一)引脚分配

芯片采用840 - pin FCBGA封装,引脚分配详细且复杂。通过详细的引脚图和表格,我们可以清晰地了解每个引脚的功能和用途。例如,DDR相关引脚用于与外部DDR内存进行数据交互,而时钟引脚则为芯片提供稳定的时钟信号。

(二)外部引脚

外部引脚具有多种功能,包括时钟输入、启动模式控制、系统控制、中断输入、电源控制等。每个引脚都有特定的电压要求、输入输出类型和初始值。例如,BOOTSELCPU引脚用于选择冷启动CPU,低电平选择CM33,高电平选择CA55。

(三)复用功能引脚

许多引脚具有复用功能,可以根据不同的应用场景选择不同的功能。例如,P00引脚既可以作为GPIO/TINT_GP00使用,也可以用于PDMDAT00或GTETRGA等功能。

三、电气特性

(一)绝对最大额定值

为了确保芯片的安全运行,需要严格遵守绝对最大额定值。不同的电源引脚有不同的电压范围,如CA55的VDD09_CA55电压范围为 - 0.4 V至1.2 V。超出这些范围可能会导致芯片永久损坏。

(二)推荐工作范围

在推荐工作范围内使用芯片,可以保证芯片的性能和稳定性。例如,CA55的VDD09_CA55在0.86 - 0.94 V(0.9 V时为OD模式,0.8 V时为ND模式)范围内工作。

(三)电源开关序列

芯片的电源开关序列非常重要,不同的启动模式(CM33启动模式和CA55启动模式)有不同的电源开启和关闭顺序。在设计电源电路时,需要严格按照这些顺序进行操作,以确保芯片正常启动和运行。

(四)DC特性

DC特性包括最大供电电流、标准I/O特性等。了解这些特性可以帮助工程师合理设计电源电路和I/O接口。例如,不同单元的最大供电电流不同,CA55的0.8 - V(或0.9 - V)电源供应电流最大为3031 mA。

(五)AC特性

AC特性涵盖了时钟时序、各种接口的访问时序等。例如,时钟输入频率和周期有严格的要求,QEXTAL时钟输入频率为24 ± 50 ppm MHz,周期为41.67 ns。这些特性对于确保芯片在高速运行时的稳定性至关重要。

(六)模拟特性

模拟特性主要涉及ADC和温度传感器的特性。ADC具有12位分辨率,模拟输入范围为0至ADAVDD18,转换时间为0.4 - 4.0 μs。温度传感器在 - 40°C至125°C范围内的精度为±3.0 - ±5.0°C。

四、设计考量

(一)电源设计

根据芯片的电气特性,合理设计电源电路。确保电源的稳定性和纹波符合要求,避免电源波动对芯片性能产生影响。同时,要注意不同电源引脚的电压范围和启动顺序。

(二)时钟设计

时钟信号的稳定性对于芯片的正常运行至关重要。选择合适的晶体谐振器,并合理布局时钟电路,减少时钟信号的干扰和抖动。例如,在连接晶体谐振器时,要将其和相关电容尽量靠近引脚,确保接地良好。

(三)接口设计

根据具体的应用需求,合理选择和设计通信接口。注意接口的电气特性和时序要求,确保数据的准确传输。例如,在设计USB接口时,要遵循USB 2.0或USB 3.2的标准规范。

(四)ESD防护

由于芯片对静电放电(ESD)比较敏感,需要采取有效的ESD防护措施。例如,使用防静电容器存储和运输芯片,操作人员佩戴防静电手腕带等。

五、总结

RZ/V2N Group芯片以其丰富的功能和出色的性能,为电子工程师提供了强大的设计平台。在设计过程中,工程师需要深入了解芯片的特性和要求,合理设计电源、时钟、接口等电路,同时注意ESD防护等问题。只有这样,才能充分发挥芯片的优势,设计出高性能、稳定可靠的电子产品。

作为电子工程师,我们需要不断学习和掌握新的芯片技术,结合实际应用需求,进行创新设计。在使用RZ/V2N Group芯片时,你是否遇到过一些特殊的设计挑战呢?欢迎在评论区分享你的经验和见解。

发布评论请先 登录

15TOPS、双摄像头、高能效 四核视觉AI MPU RZ/V2N数据手册

瑞萨新款RZ/V2N视觉AI MPU产品介绍

RZ/V2N中档嵌入式AI MPU 数据手册和产品介绍

Banana Pi 最新边缘 AI 系统模块 BPI-AI2N 采用瑞萨电子 RZ/V2N

RZ/V2N Group芯片:功能、特性与设计考量

RZ/V2N Group芯片:功能、特性与设计考量

评论