文章来源:十二芯座

原文作者:Lychee

FinFET(鳍式场效应晶体管)自 2011 年由 Intel 商业化以来,统治了半导体先进制程超过 15 年。

它通过三维鳍状结构克服了平面 MOSFET 的短沟道效应,支撑了从 22nm 到 3nm 的摩尔定律延续。

然而,随着制程进入 2nm 关口,FinFET 物理极限凸显,静电控制能力达到饱和。近年,行业正处于从 FinFET 向 GAAFET(环绕栅极晶体管)转型的关键拐点。

三维物理逻辑

在平面 MOSFET 时代,栅极仅从上方控制沟道。当沟道长度缩短至 20nm 以下时,漏电流会通过沟道下方“流走”,导致严重的短沟道效应(SCE)。

FinFET 的核心创新在于将沟道从平面“提起”成为垂直的鳍片(Fin),让栅极(Gate)从三个侧面包围沟道。

Source: AMAT

1.1几何参数与电学性能

FinFET 的性能由以下关键维度定义:

Fin Height (Hfin):鳍片高度决定了驱动电流(Ion)。由于鳍片是垂直的,增加高度可以在不增加水平面积的情况下提升电流,实现更高的功率密度。

Fin Width (Wfin):鳍片宽度是控制漏电的关键。Wfin 越窄,栅极对沟道的静电控制力越强,亚阈值摆幅(SS)越接近理想的 60mV/dec。

Gate Pitch:栅极间距。在 5nm/3nm 节点,栅极间距已缩减至极限,导致寄生电容剧增。

1.2 物理极限的红线:量子隧穿与散热陷阱

进入 3nm 节点后,FinFET 面临两大瓶颈:

静电控制饱和:三面包裹已不足以抑制电子在亚纳米尺度下的量子隧穿,漏电流(Ioff)急剧上升。

鳍片深宽比挑战:为了维持电流,鳍片需要做得更高、更薄,但在制造工艺中,极细高的鳍片极易发生倒塌或刻蚀不均。

FinFET的有效宽度

在传统的平面晶体管中,宽度仅仅是硅表面上的一个平面尺寸。而在 FinFET 中,栅极(Gate)是包裹在垂直“鳍片”(Fin)的三个侧面上的。因此,电流可以流动的总宽度是这三个侧面的总和:

结合图片中的标注来看:

W1:鳍片顶部的宽度。

H1 & H2:鳍片两个垂直侧面的高度。

公式:有效宽度 = W1 + H1 + H2

增加晶体管宽度的方法

由于 FinFET 是 3D 结构,“W”并不像平面设计那样是一个可以随意改变的连续变量。通常通过以下两种方式来增加宽度:

多鳍片设计:这是最常用的方法。为了获得更大的驱动电流,只需设计栅极跨越多个并联的鳍片即可。这使得 FinFET 的设计变得“量子化”(即宽度是离散的,不是连续的)。

增加鳍片高度:把鳍片做得更高,可以在不占用芯片更多水平空间的情况下增加表面积(从而增加有效宽度)。

权衡与取舍

正如文中所述,鳍片高度与宽度的比例至关重要:

性能:更高的鳍片能提供更高的驱动电流,但制造难度更大(刻蚀深而窄的沟槽是很困难的)。

稳定性:如果鳍片太高且太细,在制造过程中结构会变得不稳定(可能会“倒塌”或倾斜)。

静电特性:鳍片的宽度必须足够薄,以便栅极能够对沟道保持“栅极控制”,从而防止漏电。这也是 FinFET 优于平面晶体管的一大优势。

Report cover:

-

MOSFET

+关注

关注

151文章

10759浏览量

234834 -

晶体管

+关注

关注

78文章

10434浏览量

148543 -

FinFET

+关注

关注

12文章

262浏览量

92353

原文标题:FinFET 技术的深度演进与 2nm 时代的架构交接

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

串口协议的深度剖析

LLC谐振变换器:物理本质、演进历程与SiC碳化硅技术的深度融合

重磅研究:7nm FinFET 性能优化的隐藏密码 —— 栅极与鳍片间距调控

电镀电源拓扑架构演进与SiC功率模块及驱动技术的深度价值分析报告

技术报告 | Gate 和 Fin Space Variation 对应力调制及 FinFET 性能的影响

负热膨胀材料的发展与未来:ULTEA® 背后的技术演进

从手工到自动:焊球剪切测试的技术演进与科学原理

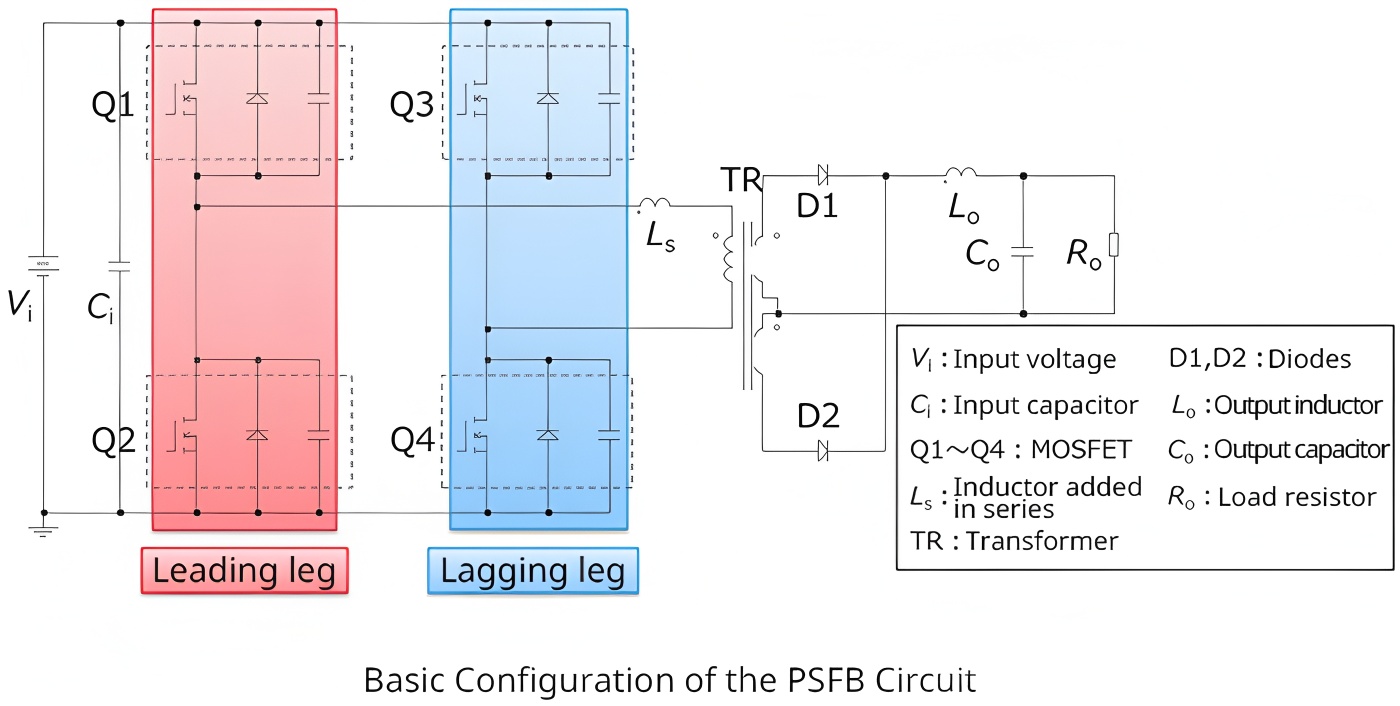

深度解析:移相全桥拓扑的演进、技术瓶颈与SiC碳化硅的应用价值

浅谈三维集成封装技术的演进

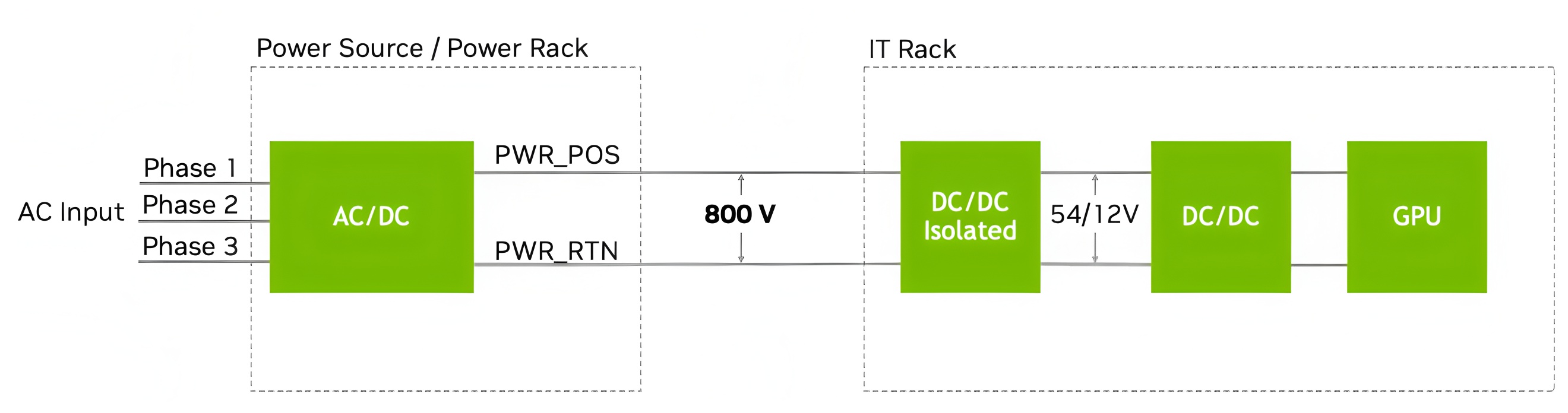

倾佳电子深度洞察AIDC电源系统技术演进与SiC MOSFET应用价值分析

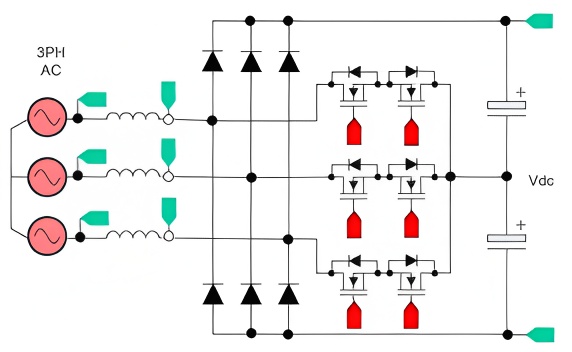

维也纳整流器技术深度解析:起源、演进与SiC碳化硅应用

OpenTenBase技术创新与演进分论坛成功举办

体硅FinFET和SOI FinFET的差异

浅谈FinFET技术的深度演进

浅谈FinFET技术的深度演进

评论