文章来源:学习那些事

原文作者:小陈婆婆

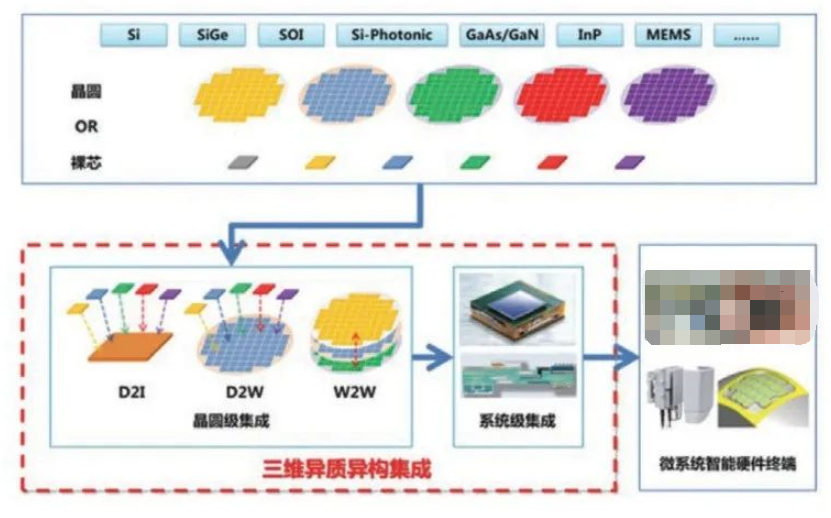

本文介绍了三维集成封装技术的进展。

三维集成封装技术演进

在半导体封装领域,堆叠技术作为推动高集成度与小型化的核心趋势,正通过垂直堆叠芯片或封装实现更紧凑的封装尺寸及优化的电气性能——其驱动力不仅源于信号传输与功率分布路径的缩短,更体现在对系统级封装(SiP)与三维集成(3D IC)的深度探索中。

尽管散热挑战与制造成本仍是主要瓶颈,但通过硅/芯片积极减薄、垂直互连技术(如TSV、TGV、TMV及引线键合)的创新应用,以及通孔形成(湿/干化学刻蚀、激光钻孔等)与金属化(CVD/PVD沉积、电镀铜等)工艺的优化,堆叠封装正逐步突破技术限制。

本文分述如下:

多芯片模块封装

叠片封装和叠层封装

三维集成电路(3D IC)

多芯片模块封装

多芯片模块(MCM)作为早期高集成度封装的典范,通过将多个半导体芯片与无源元件集成于统一基板,形成单一封装体,实现了体积缩减与电气性能的双重优化,其起源可追溯至半导体封装对邻近部件间电气路径缩短的需求驱动。基于基板技术,MCM分为MCM-L(层压基板)、MCM-D(沉积基板)和MCM-C(陶瓷基板)三类。

早期代表如Intel奔腾Pro的陶瓷多芯片组件,通过双空腔结构集成微处理器与高速缓存芯片,配合多层金线键合与外置散热器设计,在512KB二级缓存场景下验证了散热与电气互连的可行性。相较于传统分立封装,MCM的优势显著:封装体积缩小、开发周期缩短、设计错误率降低、物料清单简化,并通过减少PCB层数、批量采购组件及提升装配效率,实现系统成本优化——以Acme Systems的FOX Board嵌入式系统为例,其ETRAX100LX MCM4+16模块集成CPU、4MB闪存、16MB SDRAM及以太网收发器等组件,采用256引脚PBGA封装,尺寸27mm×27mm×2.76mm。

在保持与纯CPU封装相同占地面积的同时,通过高密度互连(HDI)基板技术实现系统级功能整合,仅需外置3.3V电源与晶体振荡器即可构建全功能Linux计算机,广泛应用于网关、门禁及工业控制器领域。当前,MCM技术正与先进封装趋势深度融合,例如在高性能计算(HPC)芯片中采用硅基板与混合键合技术实现亚微米级互连密度,结合嵌入式液冷通道与石墨烯散热材料提升热管理能力;在5G通信模块中,通过有机基板与微凸点技术实现射频前端与基带芯片的垂直集成,降低信号延迟并提升功率效率。

这些创新不仅延续了MCM在系统小型化与性能优化上的核心价值,更通过新材料与新工艺的引入,拓展了其在人工智能、自动驾驶等新兴领域的应用边界,持续推动半导体封装向更高集成度、更低损耗的智能集成方向发展。

叠片封装和叠层封装

在半导体封装技术演进路径中,叠片封装与叠层封装作为实现高集成度与空间优化的核心手段,正通过工艺创新与材料突破持续拓展应用边界。早期芯片堆叠多芯片模块(MCM)以金丝键合技术为基石,依托晶圆减薄至25μm级、超薄硅芯片处理、低轮廓反向引线键合及低拉丝树脂注入等工艺,在DRAM存储器模块中实现多芯片垂直堆叠——典型如2007年量产的20芯片堆叠MCP,整体封装高度仅1.4mm,显著提升了存储密度。

然而,该技术面临层间间隙控制、导线间距精度及故障成本高等挑战:层间需预留空间避免导线短路,基板需数百微米水平间距容纳导线,且单根导线失效可能导致整个模块报废,对工艺精度与良率提出严苛要求。为突破传统金丝键合限制,行业探索了混合堆叠方案,如结合倒装芯片与引线键合的复合结构,但消费电子领域对成本与性能的平衡需求使其在批量生产中应用受限。

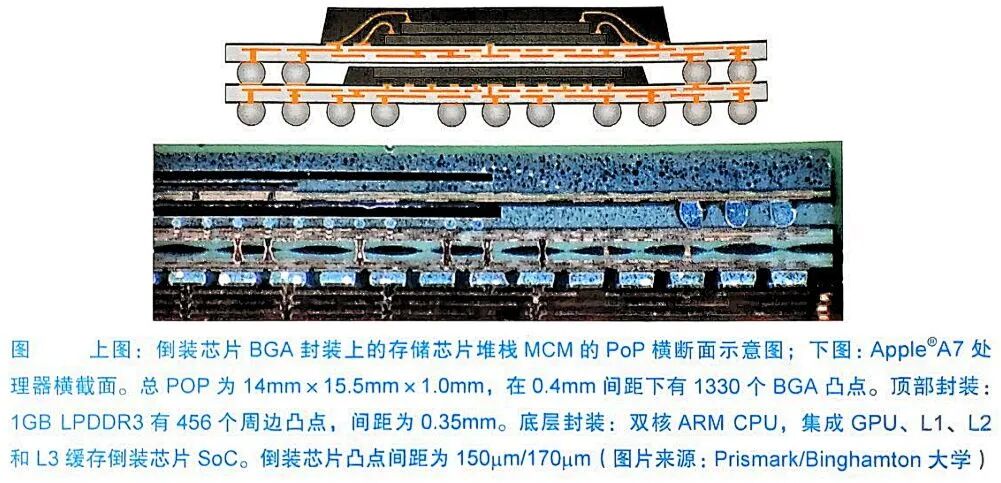

与此同时,叠层封装技术(PoP)通过将成品封装垂直堆叠,有效规避了堆叠芯片封装中的已知良好芯片(KGD)验证、工艺损伤及混合逻辑-存储器SiP组装测试复杂度等问题,早期代表如Tessera开发的uZTM球形PoP,在DRAM模块中验证了其空间节省与良率优势。PoP的典型配置包括纯内存堆叠与混合逻辑-内存堆叠(底部为逻辑芯片如CPU,顶部为存储器),后者因逻辑芯片需更多BGA连接而采用底部布局。在工艺优化方面,底部封装采用倒装芯片技术可释放X/Y方向空间,避免引线键合所需的隔离区域,配合下填充材料提升可靠性,同时降低顶部与底部封装间的间隙高度,支持更小焊球与更紧密互连间距,从而实现对整体封装高度的精准控制,该方案在移动电子设备中已广泛应用,如Apple A7微处理器与内存的PoP堆栈。

当前,叠片与叠层封装技术正与前沿创新深度融合:3D堆叠技术如硅通孔(TSV)与混合键合(铜-铜直接键合)的应用,显著提升了互连密度与电气性能;高密度互连(HDI)基板与有机基板的引入,结合人工智能驱动的布局布线优化算法,进一步提高了PoP的信号完整性与良率;新型材料如碳纳米管、石墨烯在堆叠结构中的集成,不仅增强了导电性与热管理能力,还为高频、高功率场景下的性能提升提供了新路径。这些进展持续推动着叠片与叠层封装向更高集成度、更低损耗、更优热管理的方向发展,在5G通信、人工智能计算、自动驾驶等新兴领域展现出广阔的应用前景。

三维集成电路(3D IC)

三维集成电路(3D IC)作为芯片级集成的终极形态,通过垂直与水平方向的多层有源电子元件集成,推动半导体技术向更高密度、更低功耗演进。

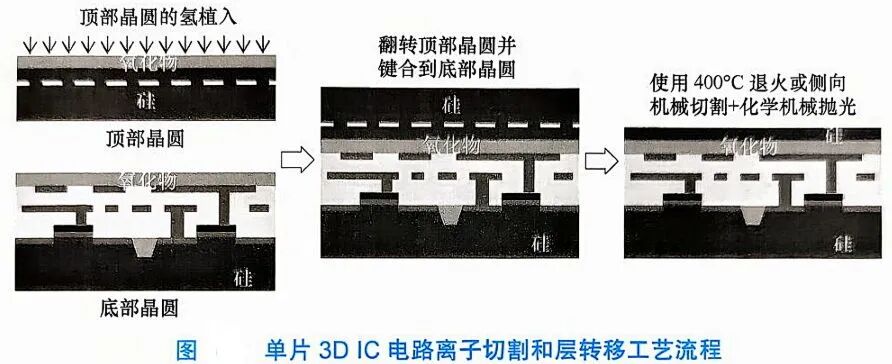

其核心构建路径分为单片3D IC与TSV 3D IC两大体系:单片3D IC依托单晶圆分层制造技术,通过离子切割与氢注入实现薄硅层转移,结合高温(>800℃)与低温(<400℃)双阶段工艺,在基板晶圆顶部形成多层无缺陷硅层,完成晶体管布线与层间连接,无需硅通孔即可实现有源层零间隙集成,该技术由DARPA资助的斯坦福大学研究团队及Monolithic 3D公司推进,已在SOI晶圆生产中验证其可行性;TSV 3D IC则通过晶圆堆叠(WoW)、芯片-晶圆堆叠(CoW)及芯片-芯片堆叠(CoC)三种工艺实现垂直互连——WoW需在独立晶圆上预制组件层后键合切割,面临晶圆尺寸匹配与缺陷导致的成品率挑战;CoW与CoC通过已知良好芯片(KGD)堆叠优化产量,支持混合匹配以适配移动设备等场景的功耗性能需求。当前,TSV技术已突破金属-金属直接键合瓶颈,配合铜互连与硅通孔微凸点,实现亚微米级互连密度,在高性能计算(HPC)芯片中验证了信号延迟降低与热管理提升的实效。

同时,3D IC正与硅光子集成、碳纳米管导热材料等前沿技术融合,例如在光通信模块中实现光电协同集成,或在人工智能加速器中通过3D堆叠提升内存带宽与计算效率。这些创新不仅延续了3D IC在系统集成与性能优化上的核心价值,更通过新材料与新工艺的引入,拓展了其在自动驾驶、量子计算等新兴领域的应用边界,持续推动半导体封装向更高集成度、更低损耗的智能集成方向发展。

-

半导体

+关注

关注

336文章

29977浏览量

258224 -

三维

+关注

关注

1文章

523浏览量

29833 -

集成封装

+关注

关注

0文章

14浏览量

10150

原文标题:三维集成封装技术演进

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

三维封装工艺流程与技术

世界级专家为你解读:晶圆级三维系统集成技术

三维触控技术突破“二向箔”的束缚

三维快速建模技术与三维扫描建模的应用

广西扫描服务三维检测三维扫描仪

三维设计应用案例

基于LTCC技术的三维集成微波组件

浅谈三维集成封装技术的演进

浅谈三维集成封装技术的演进

评论