AD9861:宽带应用的混合信号前端基带收发器

在当今的通信领域,对于高性能、低功耗且小尺寸的混合信号前端(MxFE)器件的需求日益增长。ADI公司的AD9861就是这样一款出色的产品,它为宽带应用提供了一个集成度高、功能强大的解决方案。今天,我们就来深入了解一下AD9861这款器件。

文件下载:AD9861.pdf

AD9861概述

AD9861是MxFE系列的一员,专为通信市场设计。它集成了双路10位模数转换器(ADC)和双路10位数模转换器(TxDAC),有-50和-80两种速度等级可供选择。-50型号针对50 MSPS及以下的ADC采样进行了优化,而-80型号则适用于50 MSPS至80 MSPS的ADC采样率。双路TxDAC的工作速度最高可达200 MHz,并配备了可旁路的2×或4×插值滤波器。此外,还有三个辅助转换器,可用于提供系统级控制电压或监测系统信号。

AD9861的设计目标是实现高性能、低功耗和小尺寸,为宽带通信市场提供经济高效的解决方案。它采用单输入时钟引脚(CLKIN)生成所有系统时钟,通过灵活的20位I/O总线与各种数字后端或DSP进行接口,并且可以通过寄存器编程或模式引脚进行配置。

关键特性

1. 收发路径设计

- 接收路径:包含双路10位ADC,具有内部或外部参考选项。ADC采用9级差分流水线开关电容架构,并带有输出误差校正逻辑,采样发生在输入时钟的下降沿。这种架构允许第一级处理新的输入样本,而其余级处理先前的样本,从而提高了处理效率。同时,差分输入级具有直流自偏置功能,可接受差分或单端输入。

- 发送路径:集成双路10位、200 MSPS的TxDAC,支持1×、2×或4×插值和可编程增益控制。TxDAC核心提供双差分互补电流输出,通过可编程增益放大器(TxPGA)、粗增益控制、偏移调整和细增益控制来补偿系统失配,提高了信号的调制精度和镜像抑制能力。

2. 时钟分布与控制

内部时钟分布块包含可编程锁相环(PLL)和时序生成电路,支持单参考时钟操作。PLL可以提供1×、2×、4×、8×和16×的乘法功能,并且可以通过寄存器进行旁路和电源管理。此外,芯片还包含时钟占空比稳定器(DCS)电路,可在输入时钟频率超过40 MHz时提供标称50%的占空比,以满足高速应用的需求。

3. 灵活的I/O接口

20位灵活I/O数据接口支持半双工模式下的各种交错或非交错数据传输,以及全双工模式下的交错数据传输。这种灵活性使得AD9861能够适应不同的数据接口需求,同时减少了引脚数量和封装尺寸。接口可以通过模式引脚或串行可编程接口(SPI)进行配置,SPI提供了更多的可编程选项,包括TxDAC路径的粗、细增益控制和偏移控制,以及ADC路径的内部占空比稳定器和二进制补码数据格式。

4. 低功耗设计

AD9861具有独立的Rx和Tx功率控制引脚,可以分别对接收和发送路径进行功率管理。此外,还提供了低功耗ADC模式和TxDAC功率缩放功能,通过电源控制、低功耗模式设置和半双工模式,可以进一步优化功耗,以满足不同应用场景的需求。

5. 辅助转换器

芯片集成了三个8位电压输出辅助数模转换器(AuxDAC)和两个10位逐次逼近寄存器(SAR)辅助模数转换器(AuxADC)。AuxDAC可用于提供各种系统控制电压,而AuxADC则可用于监测系统外部信号。这些辅助转换器可以通过串行可编程寄存器进行启用和控制,为系统设计提供了更多的灵活性。

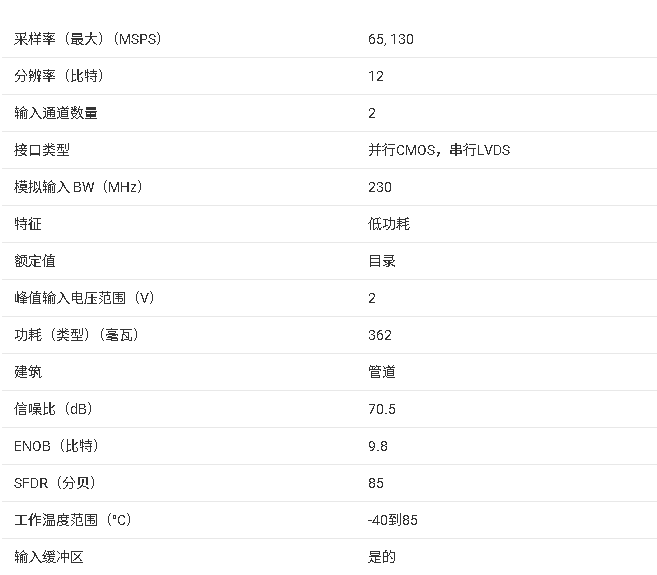

性能指标

1. 发送路径

在特定测试条件下(如(F{DAC}=200 MSPS),4x插值,(R{SET}=4.02 k Omega) ,差分负载电阻为(100 Omega) ,(TxPGA =20 dB) ,(AVDD=DVDD=3.3 V) ),AD9861的发送路径具有以下性能指标:

- 分辨率:10位

- 最大DAC更新速率:200 MHz

- 最大满量程输出电流:20 mA

- 满量程误差:1%

- 增益失配误差:±3.5% FS

- 偏移失配误差:±0.1% FS

- 参考电压:1.23 V

- 输出电容:5 pF

- 相位噪声(1 kHz偏移,6 MHz音调):-115 dBc/Hz

- 输出电压合规范围:-1.0 V至+1.0 V

- TxPGA增益范围:20 dB

- TxPGA步长:0.10 dB

2. 接收路径

对于AD9861-50,(F{ADC}=50 MSPS) ;对于AD9861-80,(F{ADC}=80 MSPS) ,在内部参考、差分模拟输入和(ADC_AVDD = DVDD = 3.3 V) 的条件下,接收路径的性能指标如下:

- 分辨率:10位

- 最大ADC采样率:50/80 MSPS

- 增益失配误差:±30% FS

- 偏移失配误差:±0.1% FS

- 参考电压:1.0 V

- 参考电压(REFT–REFB)误差:±6 mV

- 输入电阻(差分):2 kΩ

- 输入电容:5 pF

- 输入带宽:30 MHz

- 差分模拟输入电压范围:2 V p-p差分

3. 功耗

在模拟和数字电源为3.3 V,(F_{CLKIN}=50 MHz) ,PLL 4x设置和正常时序模式下,AD9861的功耗指标如下:

- 电源电压范围:模拟电源(AVDD)和数字电源(DVDD)为2.7 V至3.6 V,驱动电源(DRVDD)为2.7 V至3.6 V

- 模拟电源电流:发送路径(20 mA满量程输出)为70 mA,发送路径(2 mA满量程输出)为20 mA,接收路径(AD9861-80,80 MSPS)为165 mA等

- 数字电源电流:不同采样率和插值模式下有所不同,如双DAC 50 MSPS DAC更新半双工模式为50 mA等

应用领域

由于其高性能、低功耗和小尺寸的特点,AD9861适用于多种宽带应用,包括但不限于:

- 宽带接入:如DSL、Cable Modem等高速数据接入系统

- 宽带局域网(LAN):支持高速数据传输和通信

- 通信调制解调器:用于各种无线和有线通信系统的调制和解调

设计考虑

1. 输入信号驱动

AD9861的接收路径模拟输入具有独特的结构,将输入采样保持放大器(SHA)和第一级流水线残差放大器合并为一个紧凑的开关电容电路。这种结构在降低噪声和功耗方面具有优势,但对输入驱动源提出了一定的要求。在设计时,需要考虑输入驱动源的能力,确保能够在半个时钟周期内以10位精度对电容进行充电或放电。可以通过在信号源输出和VIN引脚之间添加串联电阻来降低对信号源的驱动要求,同时根据应用带宽选择合适的电阻和电容值,以实现低通滤波和降低交流负载阻抗的目的。

2. 时钟质量

高速、高分辨率的ADC对时钟输入的质量非常敏感。时钟抖动会导致SNR下降,特别是在欠采样应用中。因此,建议使用低抖动的晶体控制振荡器作为时钟源,并确保时钟驱动电源与ADC输出驱动电源分离,以避免数字噪声对时钟信号的调制。此外,当输入时钟频率超过40 MHz时,可以启用时钟占空比稳定器(DCS)电路,以提供稳定的50%占空比时钟。

3. 电源管理

AD9861提供了多种电源管理选项,包括独立的Rx和Tx功率控制引脚、低功耗ADC模式和TxDAC功率缩放功能。在设计时,需要根据具体应用场景合理配置这些电源管理选项,以优化功耗。例如,在不需要发送或接收数据时,可以使用功率控制引脚将相应路径置于低功耗模式;在低速采样时,可以启用低功耗ADC模式以降低功耗。

4. 接口配置

AD9861的灵活I/O接口可以通过模式引脚或SPI寄存器进行配置。在选择配置方式时,需要考虑系统的需求和设计复杂度。使用SPI寄存器可以提供更多的可编程选项,但需要额外的软件编程;而使用模式引脚则相对简单,但配置选项有限。在配置接口时,还需要注意数据的传输模式(如并行、交错)、时钟频率和时序要求等因素。

总结

AD9861是一款功能强大、性能优异的混合信号前端基带收发器,适用于各种宽带应用。它的集成度高、功耗低、尺寸小,为工程师提供了一个便捷、高效的解决方案。在设计过程中,需要充分考虑输入信号驱动、时钟质量、电源管理和接口配置等因素,以确保芯片能够发挥最佳性能。希望本文对大家了解和应用AD9861有所帮助。你在使用AD9861的过程中遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

AD9861

+关注

关注

0文章

6浏览量

7606

发布评论请先 登录

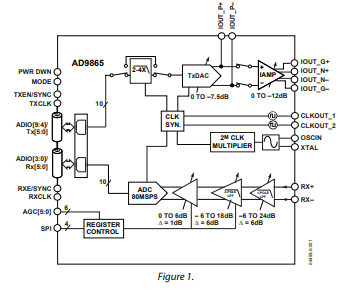

AD9865宽带调制解调器混合信号前端芯片全解析

AD9869宽带调制解调器混合信号前端芯片深度解析

MAX2980:高性能电力线通信模拟前端收发器

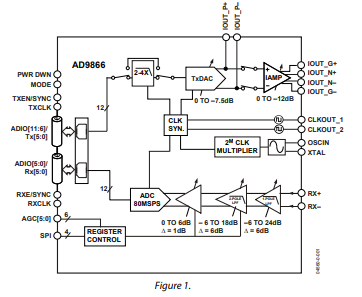

AD9866宽带调制解调器混合信号前端芯片深度剖析

AFE7222 宽带混合信号收发器技术文档总结

AFE7222/AFE7225 宽带混合信号收发器技术文档总结

AFE8092八通道RF收发器技术解析与应用指南

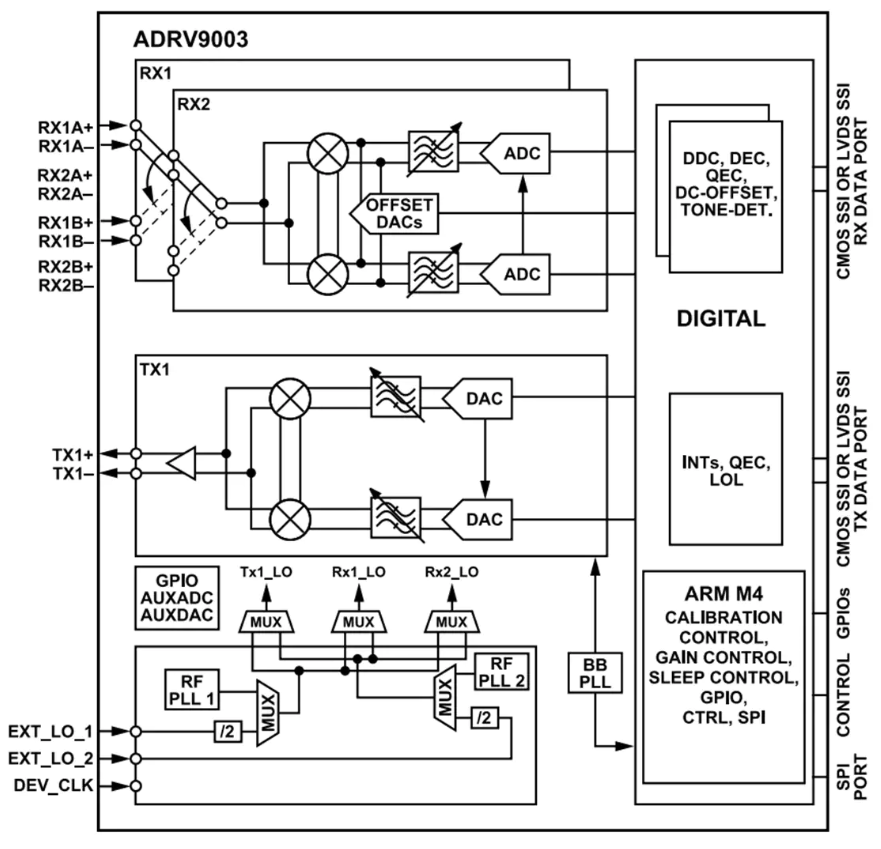

Analog Devices Inc. ADRV9003窄带/宽带射频收发器数据手册

CAN收发器:总线信号的“翻译官”

光模块与光纤收发器可以互连吗?

AD9865宽带调制解调器混合信号前端技术手册

AD9866 12位宽带调制解调器混合信号前端技术手册

AD9861:宽带应用的混合信号前端基带收发器

AD9861:宽带应用的混合信号前端基带收发器

评论