概述

AD9861是面向通信市场的集成转换器MxFE系列产品之一。它集成双通道10位模数转换器(ADC)和双通道10位数模转换器(TxDAC®)。可提供-50和-80两种速度等级。-50等级针对50 MSPS及以下的ADC采样速率进行了优化,-80等级则针对50 MSPS到80 MSPS之间的ADC采样速率进行了优化。双通道TxDAC在最高200 MHz频率下工作,并内置一个可旁路的2倍或4倍插值滤波器。同时提供三个辅助转换器,以提供所需的系统级控制电压或用来监控系统信号。AD9861针对高性能、低功耗、小尺寸而优化,为宽带通信市场提供高性价比的解决方案。

数据表:*附件:AD9861混合信号前端基带收发器,适合宽带应用技术手册.pdf

AD9861使用一个输入时钟引脚(CLKIN)产生所有系统时钟。ADC和TxDAC时钟在时序产生模块内产生,提供分频电路、PLL乘法器和开关等用户可编程选项。

灵活的双向20位I/O总线支持各种定制的数字后端或开放市场DSP。

在半双工系统中,接口支持20位并行传输或10位交错传输。在全双工系统中,接口支持交错传输的10位ADC总线以及交错传输的10位TxDAC总线。灵活的I/O总线减少了引脚数量,进而缩小了AD9861及其连接器件的封装尺寸。

AD9861可以利用MODE引脚或串行可编程接口(SPI)配置接口总线,在低功耗模式下运行ADC,配置TxDAC插值速率,并控制ADC及TxDAC关断。SPI可为TxDAC路径(例如为通道匹配而进行的粗调和精调增益控制以及失调控制)与ADC路径(例如,内部占空比稳定器和二进制补码数据格式)提供更多可编程方案。

AD9861采用64引脚LFCSP封装(薄型、细间距芯片级封装)。外形尺寸仅为9 mm × 9 mm,高度小于0.9 mm,适合PCMCIA卡等空间紧凑的应用。

应用

- 宽带接入

- 宽带局域网(LAN)

- 通信(调制解调器)

特性

- 接收路径内置双通道10位模数转换器,支持内部或外部基准电压源接入,提供50 MSPS和80 MSPS两种型号

- 发射路径内置双通道10位、200 MSPS数模转换器,提供1倍、2倍或4倍插值和可编程增益控制

- 内部时钟分配模块包括可编程锁相环(PLL)与时序产生电路,允许单一基准时钟操作

- 灵活的20引脚I/O数据接口,允许在半双工模式下进行各种交错或非交错数据传输,以及在全双工模式下进行交错数据传输

- 通过寄存器可编程性或可选MODE引脚的有限可编程性可配置

- 独立的接收(Rx)与发送(Tx)关断控制引脚

- 64引脚LFCSP封装(9 mm × 9 mm尺寸)

- 3个可配置辅助转换器引脚

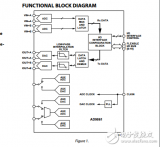

框图

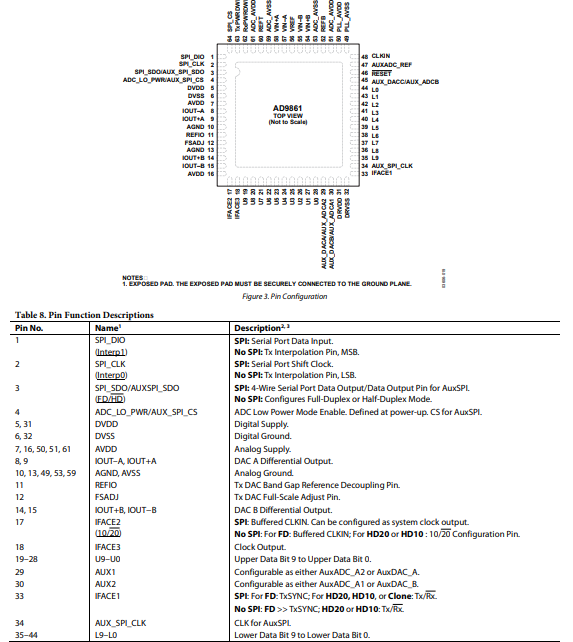

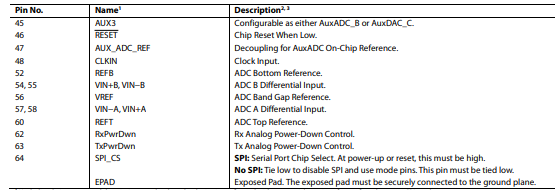

引脚配置描述

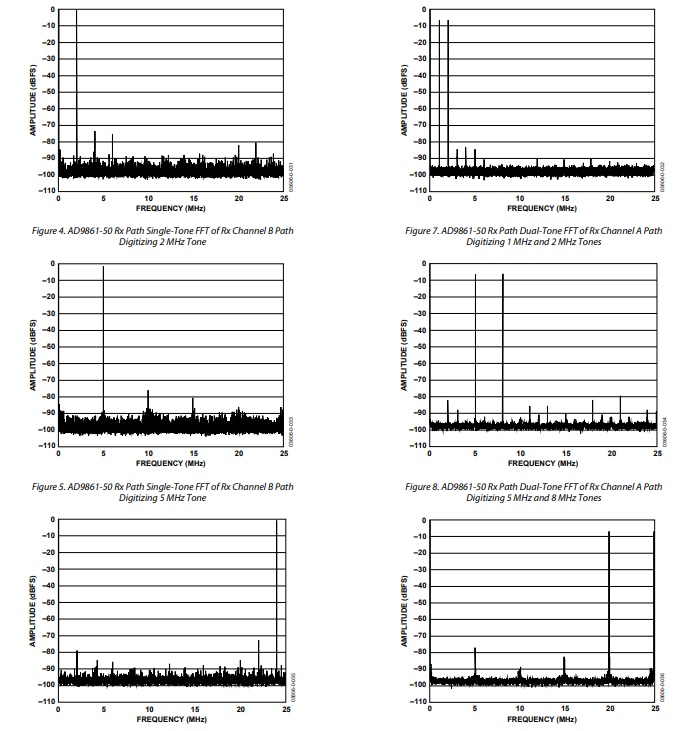

典型性能特征

系统模块

AD9861旨在满足多种无线通信的混合信号前端需求。它具备一个接收路径,该路径由双路10位接收ADC组成;还具有一个发射路径,由双路10位发射DAC(TxDAC)组成。AD9861集成了额外的功能,这些功能在大多数系统中通常是必需的,比如电源可扩展性、额外的辅助转换器、发射增益控制以及时钟乘法电路。

AD9861在尺寸和功耗方面进行了优化,以满足从低功耗便携式设备到高性能基站等广泛应用的需求。它采用64引脚无铅小型芯片级封装(LFCSP),尺寸仅为9 mm × 9 mm。功耗可以根据具体应用进行优化,不仅可以通过速度等级选项,还能通过集成电源关断控制、ADC模式、TxDAC电源缩放以及半双工模式来实现,这些模式会自动禁用未使用的数字路径。

AD9861使用两个10位总线来传输接收路径数据和发射路径数据。这些总线支持20位并行数据传输以及10位交织数据传输。总线可通过外部模式引脚或内部寄存器设置进行配置。寄存器允许对设备的整个功能进行多种选择。

以下部分将讨论AD9861的各个模块:接收路径模块、发射路径模块、辅助转换器模块、数字模块、可编程寄存器模块以及时钟分配模块。

接收路径模块

接收路径概述

AD9861的接收路径由两个10位、50 MSPS(对于AD9861 - 50)或80 MSPS(对于AD9861 - 80)的模数转换器(ADC)组成。双ADC路径共享相同的时钟和基准电路,以提供最佳的匹配特性。每个ADC采用9级差分流水线开关电容架构,并带有输出误差校正逻辑。

流水线架构使第一级能够基于新的输入样本运行,其余各级则对前一个样本进行处理,在时钟下降沿进行采样。流水线的每一级(最后一级除外)都包括一个低分辨率闪存ADC、一个剩余乘法器,用于控制流水线中下一级的数模转换器(DAC)。DAC输出(与该级输入信号相减)被放大(或乘以倍数)后,传输到下一级流水线。剩余乘法器级也被称为乘法DAC(MDAC)。每一级都有一位冗余,用于校正闪存误差。最后一级仅由闪存ADC组成,以促进闪存误差的数字校正。

差分输入级具有直流自偏置功能,支持差分或单端输入。输出暂存模块将数据与输出缓冲器对齐,校正误差,并将数据传输到输出缓冲器。

接收路径的延迟为5个时钟周期。

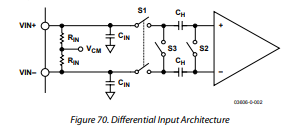

接收路径模拟输入等效电路

AD9861的接收路径模拟输入采用了一种新颖的结构,将采样保持放大器(SHA)和第一级流水线剩余放大器的功能进行了整合,采用紧凑的开关电容电路实现。这种结构在实现相当噪声和功率性能的同时,通过省去流水线中原本单独的放大器,减少了一个放大器。

图70展示了AD9861的等效模拟输入(开关电容输入)。将CLK逻辑电平拉高会打开开关S3,并闭合开关S1和S2,此时为输入电路的采样模式。在此模式下,连接到VIN+和VIN - 的输入电容Cs会被充电。将CLK逻辑电平拉低会闭合S2,然后打开S1,接着闭合S3,此时输入电路进入保持模式。

输入SHA的结构对输入驱动提出了一定要求。差分输入电阻通常为2 kΩ。Cs、Ch和输入源的组合需要满足一定条件。Cs通常小于5 pF,输入源必须能够在半个时钟周期内,以10位精度对Cs进行充电或放电。当SHA进入采样模式时,输入源必须通过开关S1的Ron(通常为100 Ω)提供充电电流,以在半个ADC采样周期内将电容充电至设定电压。这种情况对应于驱动低输入阻抗。另一方面,当源电压等于Ch上先前存储的值时,保持电容无需输入电流,等效输入阻抗极高。

-

收发器

+关注

关注

10文章

3838浏览量

111459 -

混合信号

+关注

关注

0文章

542浏览量

65935 -

ADC

+关注

关注

0文章

227浏览量

16845 -

AD9861

+关注

关注

0文章

6浏览量

7606

发布评论请先 登录

捷变频收发器AD936X的特点和优势

RadioVerse生态系统中的宽带收发器分享!

什么是用于RF收发器的简单基带处理器?

AD9861,pdf datasheet (Transcei

ad9861混合信号前端(MxFE™)宽带应用基带收发器数据表

AD9861 混合信号前端(MxFE™)基带收发器,适合宽带应用

AD9861混合信号前端基带收发器,适合宽带应用技术手册

AD9861混合信号前端基带收发器,适合宽带应用技术手册

评论