ADSP - 21369 SHARC处理器:高性能音频处理的理想之选

在电子工程领域,高性能处理器对于实现复杂的音频处理等任务至关重要。ADSP - 21369 SHARC处理器就是这样一款具有卓越性能的产品,下面我们就来详细了解一下它的特点、架构以及应用。

文件下载:ADSP-21369.pdf

一、产品概述

ADSP - 21369是一款高性能的32位/40位浮点处理器,专为高性能音频处理进行了优化。它采用单指令多数据(SIMD)计算架构,拥有2M位的片上SRAM和6M位的片上掩膜可编程ROM,并且与SHARC系列的其他成员代码兼容。其核心指令速率可达400 MHz,还配备了如数字应用接口、S/PDIF收发器、串口、8通道异步采样率转换器、精密时钟发生器等独特的以音频为中心的外设。

产品特性

| 特性 | ADSP - 21369 |

|---|---|

| 频率 | 400 MHz |

| RAM | 2M位 |

| ROM | 6M位 |

| 脉冲宽度调制 | 支持 |

| S/PDIF | 支持 |

| SDRAM内存总线宽度 | 32位/16位 |

| 串口 | 8个 |

| IDP | 支持 |

| DAI | 支持 |

| UART | 2个 |

| DPI | 支持 |

| S/PDIF收发器 | 1个 |

| AMI接口总线宽度 | 32位/16位/8位 |

| SPI | 2个 |

| TWI | 支持 |

| SRC性能 | 128 dB |

| 共享内存支持 | 仅256球BGA |

| 封装 | 256球BGA、208引脚LQFP_EP |

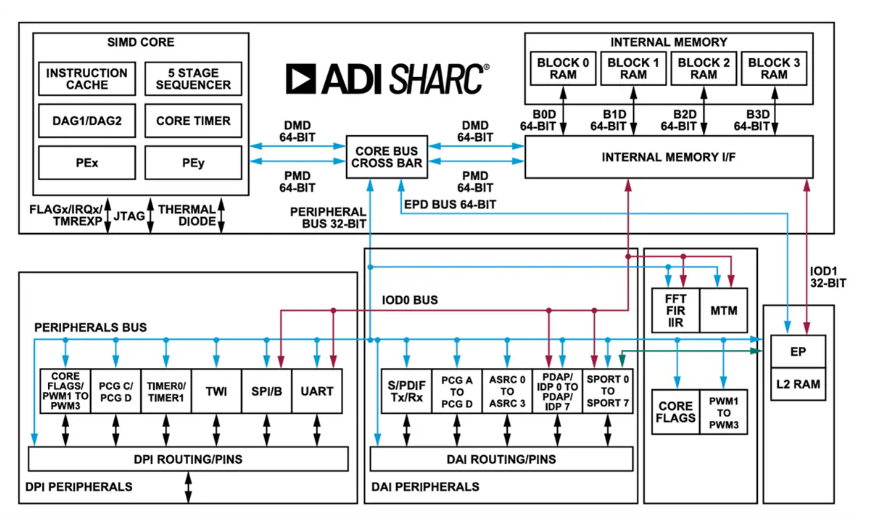

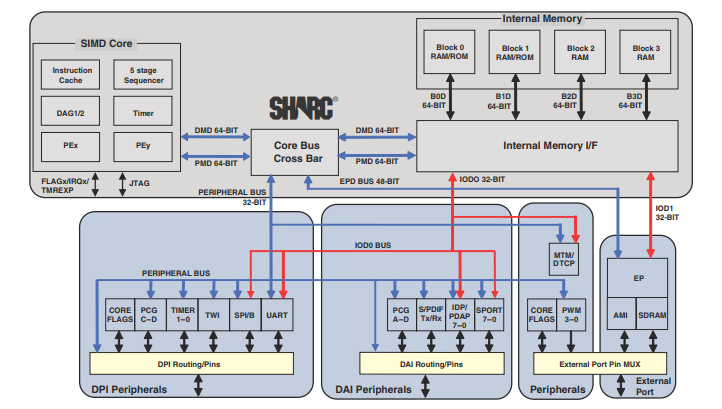

二、核心架构

SIMD计算引擎

该处理器包含两个计算处理单元,作为单指令多数据(SIMD)引擎运行。处理单元PEX和PEY各自包含一个ALU、乘法器、移位器和寄存器文件。PEX始终处于活动状态,PEY可通过设置MODE1寄存器中的PEYEN模式位来启用。进入SIMD模式后,两个处理单元执行相同的指令,但处理不同的数据,这对于执行数学密集型的DSP算法非常高效。同时,进入SIMD模式会使内存与处理单元之间的数据带宽翻倍。

独立并行计算单元

每个处理单元内都有一组计算单元,包括算术逻辑单元(ALU)、乘法器和移位器。这些单元在单个周期内执行所有操作,并且三个单元并行排列,最大限度地提高了计算吞吐量。在SIMD模式下,并行的ALU和乘法器操作会在两个处理单元中同时发生,并且支持IEEE 32位单精度浮点、40位扩展精度浮点和32位定点数据格式。

数据寄存器文件

每个处理单元都包含一个通用数据寄存器文件,用于在计算单元和数据总线之间传输数据,并存储中间结果。这些10端口、32寄存器(16个主寄存器,16个辅助寄存器)的寄存器文件,结合ADSP - 21369处理器的增强哈佛架构,允许计算单元和内部内存之间无约束的数据流。

上下文切换

处理器的许多寄存器都有辅助寄存器,可在中断服务期间激活以实现快速上下文切换。数据寄存器、DAG寄存器和乘法器结果寄存器都有辅助寄存器,主寄存器在复位时激活,辅助寄存器由模式控制寄存器中的控制位激活。

通用寄存器

USTAT(4)寄存器允许对核心的所有系统寄存器(控制/状态)进行简单的位操作(设置、清除、切换、测试、异或)。数据总线交换寄存器(PX)允许在64位PM数据总线和64位DM数据总线之间,或在40位寄存器文件和PM数据总线之间传递数据。

定时器

核心定时器可以生成周期性软件中断,并可配置为使用FLAG3作为定时器过期信号。

单周期取指令和四个操作数

处理器采用增强哈佛架构,数据内存(DM)总线传输数据,程序内存(PM)总线传输指令和数据。通过独立的程序和数据内存总线以及片上指令缓存,处理器可以在单个周期内同时获取四个操作数(每个数据总线两个)和一条指令(从缓存中)。

指令缓存

片上指令缓存支持三总线操作,用于获取一条指令和四个数据值。缓存仅对与PM总线数据访问冲突的指令进行缓存,允许核心循环操作(如数字滤波器乘法累加和FFT蝶形处理)全速执行。

数据地址生成器

处理器有两个数据地址生成器(DAGs),用于间接寻址和在硬件中实现循环数据缓冲区。循环缓冲区允许高效编程数字信号处理中所需的延迟线和其他数据结构,常用于数字滤波器和傅里叶变换。两个DAGs包含足够的寄存器,可创建多达32个循环缓冲区(16个主寄存器集,16个辅助寄存器集),并自动处理地址指针回绕,减少开销,提高性能,简化实现。

灵活的指令集

48位指令字可容纳各种并行操作,实现简洁编程。例如,ADSP - 21369处理器可以在两个处理单元中有条件地执行乘法、加法和减法,同时分支并从内存中获取多达四个32位值,所有这些都在一条指令中完成。

三、片上内存

处理器包含2M位的内部RAM和6M位的内部掩膜可编程ROM,每个块都可以配置为不同的代码和数据存储组合。每个内存块支持核心处理器和I/O处理器的单周期独立访问,内存架构结合独立的片上总线,允许在单个周期内从核心进行两次数据传输,从I/O处理器进行一次数据传输。

内存带宽

内部内存架构允许程序同时对四个块中的任何一个进行四次访问(假设没有块冲突)。总带宽通过DMD和PMD总线(2 × 64位,核心CLK)和IOD0/1总线(2 × 32位,PCLK)实现。

ROM安全特性

处理器具有ROM安全特性,通过防止在启用时从内部代码进行未经授权的读取来为用户软件代码提供硬件支持。使用此功能时,处理器不会加载任何外部代码,仅从内部ROM执行。此外,处理器不能通过JTAG端口自由访问,每个客户将分配一个唯一的64位密钥,必须通过JTAG或测试访问端口扫描输入,设备将忽略错误的密钥,只有在扫描正确的密钥后,仿真功能和外部引导模式才可用。

四、外设架构

外部端口

外部端口接口支持通过核心和DMA访问外部内存,外部内存地址空间分为四个银行。任何银行都可以编程为异步或同步内存。外部端口由异步内存接口(AMI)、SDRAM控制器、仲裁逻辑和共享内存接口组成。

SDRAM控制器

SDRAM控制器提供与多达四个独立的行业标准SDRAM设备或DIMM的接口,速度可达 (f_{SCLK }) 。每个银行有自己的内存选择线(MS0 - MS3),可以配置为包含16M字节到128M字节的内存。

外部内存

外部端口提供与各种行业标准内存设备的高性能、无胶合接口。32位宽的总线可通过其独立的内部内存控制器连接到同步和/或异步内存设备。

共享外部内存

ADSP - 21369处理器支持与其他ADSP - 21369处理器连接到公共共享外部内存,以创建共享外部总线处理器系统。支持分布式、片上仲裁、固定和旋转优先级总线仲裁、总线超时逻辑和总线锁定。

脉冲宽度调制(PWM)

PWM模块是一个灵活的、可编程的PWM波形发生器,可编程为生成各种与电机和发动机控制或音频功率控制相关的应用所需的开关模式。整个PWM模块有四组,每组四个PWM输出,共生成16个PWM输出。PWM发生器可以生成中心对齐或边缘对齐的PWM波形,并在生成中心对齐的PWM波形时可以在单更新模式或双更新模式下运行。

数字应用接口(DAI)

DAI提供了将各种外设连接到DSP的DAI引脚的能力。通过信号路由单元(SRU),程序可以在软件控制下互连DAI提供的外设。DAI包括八个串口、一个S/PDIF收发器、四个精密时钟发生器(PCG)、八个通道的同步采样率转换器和一个输入数据端口(IDP)。

串口

处理器具有八个同步串口(SPORTs),提供与各种数字和混合信号外设设备的低成本接口。串口由两条数据线、一个时钟和帧同步组成,数据线可以编程为发送或接收,每个数据线都有一个专用的DMA通道。串口可以在标准DSP串行模式、多通道(TDM)模式、I2S模式、打包I2S模式和左对齐样本对模式下运行。

S/PDIF兼容数字音频收发器

S/PDIF收发器没有单独的DMA通道,它接收串行格式的音频数据并将其转换为双相编码信号。串行数据输入可以格式化为左对齐、I2S或右对齐,字宽为16、18、20或24位。

同步/异步采样率转换器(SRC)

SRC包含四个SRC块,与AD1896 192 kHz立体声异步采样率转换器使用相同的核心,提供高达128 dB的SNR。SRC块可用于在独立立体声通道上执行同步或异步采样率转换,而无需使用内部处理器资源。

输入数据端口(IDP)

IDP提供多达八个串行输入通道,每个通道都有自己的时钟、帧同步和数据输入。八个通道自动复用为一个32位、深度为8的FIFO。数据始终格式化为64位帧,并分为两个32位字。

精密时钟发生器(PCG)

PCG由四个单元组成,每个单元从时钟输入信号生成一对信号(时钟和帧同步)。这些单元功能相同且相互独立,生成的两个信号通常用作串行位时钟/帧同步对。

数字外设接口(DPI)

DPI提供与两个串行外设接口端口(SPI)、两个通用异步接收器 - 发送器(UARTs)、一个2线接口(TWI)、12个标志和三个通用定时器的连接。

五、I/O处理器特性

DMA控制器

处理器的片上DMA控制器允许在无需处理器干预的情况下进行数据传输。DMA控制器独立于处理器核心运行,允许在核心同时执行程序指令时进行DMA操作。ADSP - 2136x处理器有34个DMA通道,可用于处理器内部内存与串口、SPI兼容端口、IDP、并行数据采集端口(PDAP)或UART之间的数据传输。

延迟线DMA

处理器提供延迟线DMA功能,允许处理器以有限的核心交互读写外部延迟线缓冲区(在外部内存、SRAM或SDRAM中)。

六、系统设计

程序引导

处理器的内部内存可以在系统上电时从8位EPROM通过外部端口、SPI主设备或从设备或内部引导启动。引导模式由引导配置(BOOT_CFG1 - 0)引脚确定。

电源供应

处理器有独立的内部( (V{DDOST }) )、外部( (V{DDEXT }) )和模拟( (A{VDD} / A{Vss}) )电源供应连接。内部和模拟电源必须满足400 MHz设备的1.3 V要求,333 MHz和266 MHz设备的1.2 V要求,外部电源必须满足3.3 V要求。

七、开发工具

Analog Devices为其处理器提供了完整的软件和硬件开发工具,包括集成开发环境(如CrossCore® Embedded Studio和VisualDSP++®)、评估产品、仿真器和各种软件插件。

集成开发环境(IDEs)

CrossCore Embedded Studio基于EclipseTM框架,支持大多数Analog Devices处理器系列,是未来处理器(包括多核设备)的首选IDE。VisualDSP++支持在CrossCore Embedded Studio发布之前推出的处理器系列。

EZ - KIT Lite评估板

Analog Devices提供各种EZ - KIT Lite评估板,包括处理器和关键外设,支持片上仿真功能和其他评估和开发功能。

软件插件

Analog Devices提供与CrossCore Embedded Studio无缝集成的软件插件,包括评估硬件的板支持包、各种中间件包和算法模块。

八、引脚功能描述

文档详细描述了ADSP - 21369处理器的引脚功能,包括外部地址、数据、内存选择、写使能、标志、中断、JTAG等引脚的功能和状态。

九、规格参数

工作条件

文档提供了不同频率下的电源电压、输入输出电压、结温等工作条件参数。

电气特性

包括高电平输出电压、低电平输出电压、高电平输入电流、低电平输入电流等电气特性参数。

最大功耗

可参考“Estimating Power Dissipation for ADSP - 21368 SHARC Processors”(EE - 299)获取详细的热和功率信息。

绝对最大额定值

包括内部(核心)电源电压、模拟(PLL)电源电压、外部(I/O)电源电压、输入电压、输出电压摆幅、负载电容、存储温度范围和偏置下的结温等绝对最大额定值。

时序规格

详细描述了核心时钟要求、电源上电时序、时钟输入、复位、中断、定时器、SDRAM接口、内存读写等的时序规格。

输出驱动电流

文档提供了输出驱动的典型I - V特性曲线。

测试条件

AC信号规格(时序参数)基于特定的电压参考电平,输出延迟和保持基于标准电容负载。

电容负载

输出延迟和保持与负载电容的关系通过图形展示。

热特性

提供了256球BGA_ED和208引脚LQFP_EP封装的热特性参数,可用于确定设备的结温。

引脚排列

详细列出了256球BGA_ED和208引脚LQFP_EP封装的引脚名称和默认功能。

封装尺寸

给出了256球BGA_ED和208引脚LQFP_EP封装的尺寸信息。

表面贴装设计

提供了BGA_ED数据,用于表面贴装设计参考。

订购指南

列出了不同型号的ADSP - 21369处理器的温度范围、指令速率、片上SRAM、ROM、封装描述和封装选项等信息。

ADSP - 21369 SHARC处理器凭借其强大的性能、丰富的外设和完善的开发工具,为电子工程师在音频处理等领域的设计提供了一个优秀的选择。在实际应用中,我们需要根据具体需求合理配置和使用该处理器,以充分发挥其优势。大家在使用过程中有没有遇到什么特别的问题或者有什么独特的应用经验呢?欢迎在评论区分享交流。

-

SHARC处理器

+关注

关注

0文章

57浏览量

7927 -

音频处理

+关注

关注

0文章

205浏览量

18332

发布评论请先 登录

剖析ADSP - BF512/BF514/BF516/BF518:高性能嵌入式处理器的卓越之选

ADSP-21593/21594/ADSP-SC592/SC594处理器:高性能与多功能的完美融合

ADSP-SC57x/ADSP-2157x处理器:高性能数字信号处理的理想之选

高性能音频处理利器:ADSP - 21477/ADSP - 21478/ADSP - 21479处理器深度解析

ADSP - 21467/ADSP - 21469 SHARC处理器:高性能音频处理的理想之选

探索ADSP - 21371/ADSP - 21375 SHARC处理器:高性能音频处理的利器

深度解析ADSP-2126x:高性能音频处理的理想之选

Analog Devices Inc. ADSP1802 SHARC®处理器数据手册

ADSP-21371/ADSP-21375面向汽车音频的32位高性能浮点SHARC处理器技术手册

ADSP - 21369 SHARC处理器:高性能音频处理的理想之选

ADSP - 21369 SHARC处理器:高性能音频处理的理想之选

评论