解析ADN4670:可编程低电压1:10 LVDS时钟驱动器

引言

在电子系统设计中,时钟信号的精确分配至关重要。ADN4670作为一款可编程低电压1:10 LVDS时钟驱动器,为时钟分配网络提供了高效、可靠的解决方案。本文将深入解析ADN4670的特性、工作原理、技术参数以及应用场景,帮助电子工程师更好地了解和使用这款产品。

文件下载:ADN4670.pdf

产品特性与优势

1. 低输出偏斜

ADN4670具有典型值小于30ps的低输出偏斜,能够确保时钟信号在传输过程中的同步性,减少信号延迟差异对系统性能的影响。这对于对时钟同步要求较高的应用,如高速数据通信、数据采集系统等尤为重要。

2. 灵活的可编程性

通过简单的串行接口,该器件可以实现从两个差分时钟输入(CLK0、CLK1)中选择一个,并能单独启用或禁用10个差分时钟输出。这种灵活性使得工程师可以根据具体应用需求进行定制化配置,提高系统的适应性。

3. 高信号速率

其典型的信号速率高达1.1 GHz,能够满足高速时钟信号的传输需求,适用于高速数字电路和通信系统。

4. 宽电源电压范围

电源电压范围为2.375 V至2.625 V,这使得ADN4670在不同的电源环境下都能稳定工作,增强了其在各种应用场景中的兼容性。

5. 故障安全设计

在电源关闭((V_{DD}=0V))时,I/O引脚具有故障安全功能,确保在异常情况下系统的稳定性。

6. 多种封装形式

提供32引脚的LFCSP和LQFP封装,方便工程师根据不同的PCB布局和设计要求进行选择。

7. 宽工作温度范围

工业级的工作温度范围为 -40°C至 +85°C,适用于各种恶劣的工业环境。

工作原理

信号处理流程

ADN4670接收来自源(如双绞线电缆)的差分电流信号,该信号在100 Ω终端电阻上产生典型值为±350 mV的电压。信号通过差分多路复用器传输到10个驱动器,每个驱动器输出差分电流信号,从而将一个差分时钟输入扩展为10个差分时钟输出。

可编程控制

通过三个控制输入(EN、SI、CK)实现可编程功能。EN为使能输入,高电平时允许编程;SI为串行数据输入;CK为串行时钟输入,在时钟从低到高的转换时将数据时钟输入到器件中。

技术参数详解

电气特性

| 参数 | 符号 | 最小值 | 典型值 | 最大值 | 单位 | 条件/注释 |

|---|---|---|---|---|---|---|

| 输入高阈值 | (V_{TH}) | - | - | - | mV | - |

| 输入低阈值 | (V_{TL}) | - | - | - | mV | - |

| 差分输入电压 | (V_{ID}) | -100 | - | +100 | mV | - |

| 输入共模电压 | (V_{IC}) | - | - | - | mV | - |

| 输入电流 | (I{IH}, I{IL}) | - | - | - | μA | - |

| 输入电容 | (C_{I}) | - | - | 3 | pF | - |

| 差分输出电压 | (V_{OD}) | 250 | 450 | 600 | mV | (R_{L}=100Ω), -40°C至 +85°C |

| 差分输出电压幅度变化 | (Delta V_{OD}) | - | - | 50 | mV | - |

| 偏移电压 | (V_{OS}) | 0.95 | 1.2 | 1.45 | V | - |

| 偏移电压幅度变化 | (Delta V_{OS}) | - | - | - | mV | - |

| 输出短路电流 | (I_{OS}) | - | - | 350 | mA | - |

| 参考输出电压 | (V_{BB}) | - | - | - | V | - |

| 输出电容 | (C_{O}) | - | - | - | pF | - |

| 电源电流 | (I_{DD}) | - | 100 | 150 | mA | 所有输出三态,(f = 0Hz) |

| 电源电流 | (I_{DD}) | - | 110 | 160 | mA | 所有输出启用并加载,(R_{L}=100Ω),(f = 100MHz) |

| 电源电流 | (I_{DD}) | - | - | - | mA | 所有输出启用并加载,(R_{L}=100Ω),(f = 800MHz) |

抖动特性

| 参数 | 符号 | 最小值 | 典型值 | 最大值 | 单位 | 条件/注释 |

|---|---|---|---|---|---|---|

| 从输入到LVDS输出(Q3和Q3)的附加相位抖动 | (t_{JITTER LVDS}) | - | 281 | - | (f_{S} rms) | 12 kHz至5 MHz,(f_{OUT}=30.72MHz) |

| 从输入到LVDS输出(Q3和Q3)的附加相位抖动 | (t_{JITTER LVDS}) | 111 | - | - | (f_{S} rms) | 12 kHz至20 MHz,(f_{OUT}=125MHz) |

LVDS开关特性

| 参数 | 符号 | 最小值 | 典型值 | 最大值 | 单位 | 条件/注释 |

|---|---|---|---|---|---|---|

| 低到高传播延迟 | (t_{PLHx}) | - | 2 | 3 | ns | 从CLK0/CLK0或CLK1/CLK1到任何Qx/Qx |

| 高到低传播延迟 | (t_{PHLx}) | - | 2 | 3 | ns | 从CLK0/CLK0或CLK1/CLK1到任何Qx/Qx |

| 占空比 | (t_{DUTY}) | 45 | - | 55 | % | 从CLK0/CLK0或CLK1/CLK1到任何Qx/Qx |

| 输出偏斜 | (t_{SK(O)}) | - | 30 | - | ps | 任何Qx/Qx |

| 脉冲偏斜 | (t_{SK(P)}) | - | - | 50 | ps | 任何Qx/Qx |

| 器件间输出偏斜 | (t_{SK(PP)}) | - | - | 600 | ps | 任何Qx/Qx |

| 输出上升时间 | (t_{r}) | - | - | 350 | ps | 任何Qx/Qx,20%至80%,(R{L}=100Ω),(C{L}=5pF) |

| 输出下降时间 | (t_{f}) | - | - | 350 | ps | 任何Qx/Qx,80%至20%,(R{L}=100Ω),(C{L}=5pF) |

| 最大输入频率 | (f_{CLK}) | 900 | 1100 | - | MHz | 从CLK0/CLK0或CLK1/CLK1到任何Qx/Qx |

编程逻辑交流特性

| 参数 | 符号 | 最小值 | 典型值 | 最大值 | 条件/注释 |

|---|---|---|---|---|---|

| CK输入的最大频率 | (f_{MAX}) | 100 | 150 | - | - |

| SI到CK的建立时间 | (t_{SU}) | - | - | 2 | SI在CK从0到1转换前必须保持不变的时间 |

| CK到SI的保持时间 | (t_{H}) | - | - | 1.5 | SI在CK从0到1转换后必须保持不变的时间 |

| EN到CK的移除时间 | (t_{REMOVAL}) | - | - | 1.5 | EN到CK的移除时间 |

| 启动时间 | (t_{STARTUP}) | - | - | 1 | 通过SI禁用后启动时间 |

| 最小时钟脉冲宽度 | (t_{W}) | 3 | - | - | - |

| 逻辑输入高电平 | (V_{IH}) | 2 | - | - | (V_{DD}=2.5V) |

| 逻辑输入低电平 | (V_{IL}) | - | - | 0.8 | (V_{DD}=2.5V) |

| 高电平逻辑输入电流(CK) | (I_{IH}) | -5 | - | +5 | (V{I}=V{DD}) |

| 高电平逻辑输入电流(SI和EN) | - | +10 | - | -30 | (V{I}=V{DD}) |

| 低电平逻辑输入电流(CK) | (I_{IL}) | -10 | - | +30 | (V_{I}=GND) |

| 低电平逻辑输入电流(SI和EN) | - | -5 | - | +5 | (V_{I}=GND) |

应用场景

时钟分配网络

ADN4670非常适合用于时钟分配网络,能够将一个时钟信号精确地分配到多个负载,确保各个部分的时钟同步,提高系统的稳定性和可靠性。例如,在数据中心的服务器集群中,需要为多个处理器和芯片提供同步的时钟信号,ADN4670可以满足这一需求。

编程与配置

编程步骤

- 使能编程:将EN引脚置为高电平,允许编程操作。

- 数据输入:在CK引脚的每个从0到1的转换时,将SI引脚上的数据时钟输入到器件中。数据必须在时钟转换前的建立时间((t{SU}))内保持稳定,并在转换后的保持时间((t{H}))内保持不变。

- 数据传输:需要11位数据进行编程,从第0位开始,依次决定输出Q9/Q9到Q0/Q0的启用或禁用,第10位选择输入时钟(0 = CLK0/CLK0,1 = CLK1/CLK1)。然后,需要第12个时钟脉冲将数据从移位寄存器传输到控制寄存器。

控制逻辑真值表

| CK | EN | SI | CLKO | CLKO | CLK1 | CLK1 | Q0 to Q9 | Q0 to Q9 |

|---|---|---|---|---|---|---|---|---|

| L | L | L | L | H | X | X | L | H |

| L | L | L | H | L | X | X | H | L |

| L | L | L | Open | Open | X | X | L | H |

| L | L | H | X | X | L | H | L | H |

| L | L | H | X | X | H | L | H | L |

| L | L | H | X | X | Open | Open | L | H |

注意事项

绝对最大额定值

使用时应注意器件的绝对最大额定值,如电源电压范围((V{CC})到GND为 -0.3 V至 +2.8 V)、输入电压范围(输入电压到GND为 -0.2 V至 ((V{DD}+0.2) ) V)等。超过这些额定值可能会导致器件永久性损坏。

ESD防护

ADN4670是静电放电(ESD)敏感器件,尽管产品具有专利或专有保护电路,但在操作过程中仍需采取适当的ESD防护措施,以避免性能下降或功能丧失。

输入终端匹配

为了确保信号的质量,应在时钟输入引脚CLK0到CLK0和CLK1到CLK1之间使用100 Ω电阻进行终端匹配,并尽量靠近输入引脚放置。

总结

ADN4670作为一款高性能的可编程低电压1:10 LVDS时钟驱动器,凭借其低输出偏斜、灵活的可编程性、高信号速率等特性,为电子工程师在时钟分配网络设计中提供了一个优秀的解决方案。在实际应用中,工程师需要根据具体的设计需求,合理配置器件的参数,并注意相关的使用注意事项,以充分发挥其性能优势。

你在使用ADN4670的过程中遇到过哪些问题呢?或者对于时钟驱动器的设计,你有什么独特的见解吗?欢迎在评论区分享你的经验和想法。

-

时钟分配

+关注

关注

0文章

21浏览量

8259 -

ADN4670

+关注

关注

0文章

5浏览量

7711

发布评论请先 登录

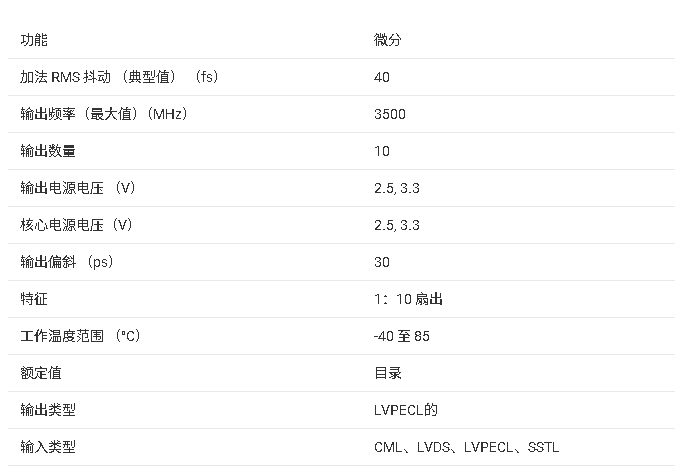

探索MAX9310:高性能1:5时钟驱动器的设计与应用

CDC391时钟驱动器:特性、参数与应用解析

CDC340:高性能1线转8线时钟驱动器的深度解析

CDC2516:高性能锁相环时钟驱动器的深度解析

CDC319:高性能1线转10线时钟驱动器

CDCVF2509:高性能PLL时钟驱动器的深度解析

CDCLVP110:高性能低电压时钟驱动器的卓越之选

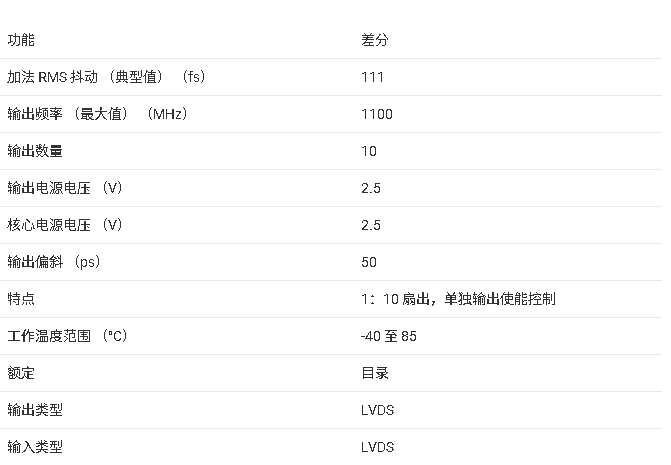

CDCLVD110A可编程低压1:10 LVDS时钟驱动器详解

深入剖析 CDCLVP215:低电压双差分 1:5 LVPECL 时钟驱动器

CDCLVP111:高性能低电压时钟驱动器的卓越之选

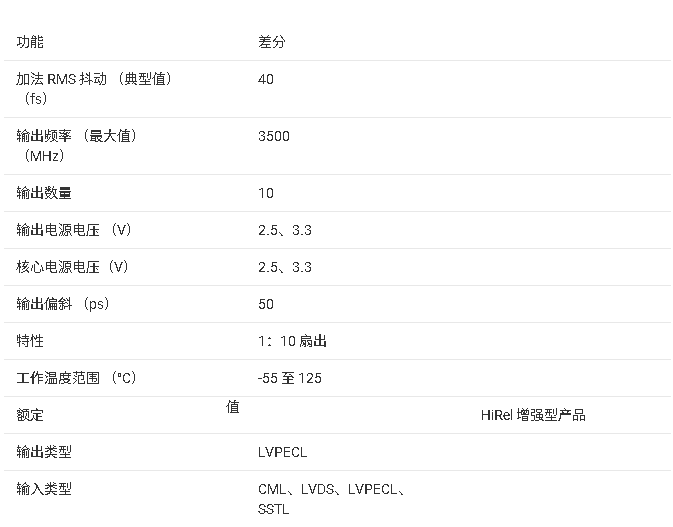

低电压 1:10 LVPECL 可选择输入时钟驱动器 CDCLVP111-EP 深度解析

深入解析CDCLVP111-SEP:低电压1:10 LVPECL时钟驱动器

CDCLVP111 低电压1:10 LVPECL时钟驱动器技术文档总结

CDCLVP111-EP 低电压1:10 LVPECL时钟驱动器技术文档总结

解析ADN4670:可编程低电压1:10 LVDS时钟驱动器

解析ADN4670:可编程低电压1:10 LVDS时钟驱动器

评论