低电压 1:10 LVPECL 可选择输入时钟驱动器 CDCLVP111-EP 深度解析

在电子设计领域,时钟驱动器的性能优劣对整个系统的稳定性和可靠性起着至关重要的作用。今天,我们就来深入探究 Texas Instruments 公司推出的低电压 1:10 LVPECL 可选择输入时钟驱动器 CDCLVP111-EP。

文件下载:cdclvp111-ep.pdf

1. 产品特性亮点

信号分配与兼容性

CDCLVP111-EP 能够将一路差分时钟输入对从 LVPECL 转换并分配到 10 路差分 LVPECL 输出。这一功能使得它在处理时钟信号分配时表现出色,而且完全兼容 LVECL 和 LVPECL 标准,大大增强了其在不同电路环境中的适用性。

电源电压与输入选择

该驱动器支持 2.375 V 至 3.8 V 的宽电源电压范围,为设计人员在电源配置上提供了更多的灵活性。同时,通过 CLK_SEL 引脚可以实现时钟输入的选择,方便在不同时钟源之间进行切换。

低输出偏斜与抖动控制

在时钟分配应用中,低输出偏斜是非常关键的指标。CDCLVP111-EP 的典型输出偏斜仅为 15 ps,并且附加抖动小于 1 ps,传播延迟小于 355 ps。这些优秀的性能指标确保了时钟信号能够准确、稳定地传输到各个输出端口。

其他特性

它还提供了 (V_{BB}) 参考电压输出,用于单端时钟操作;具备开放输入默认状态,并且与 LVDS、CML、SSTL 输入兼容。此外,产品采用 32 引脚 LQFP 封装,频率范围从 DC 到 3.5 GHz,还与 MC100 系列等部分产品引脚兼容,方便进行替换和升级。

2. 应用领域广泛

传输线驱动

CDCLVP111-EP 专门设计用于驱动 50 Ω 传输线,能够有效地将时钟信号传输到较远的距离,并且保持信号的完整性。这在一些需要长距离传输时钟信号的系统中非常有用,比如通信基站和工业自动化设备。

高性能时钟分配

在高性能时钟分配系统中,对时钟信号的精度和稳定性要求极高。该驱动器凭借其低输出偏斜和抖动控制的优势,能够满足这些严苛的要求,确保各个模块都能接收到准确一致的时钟信号。

特定领域应用

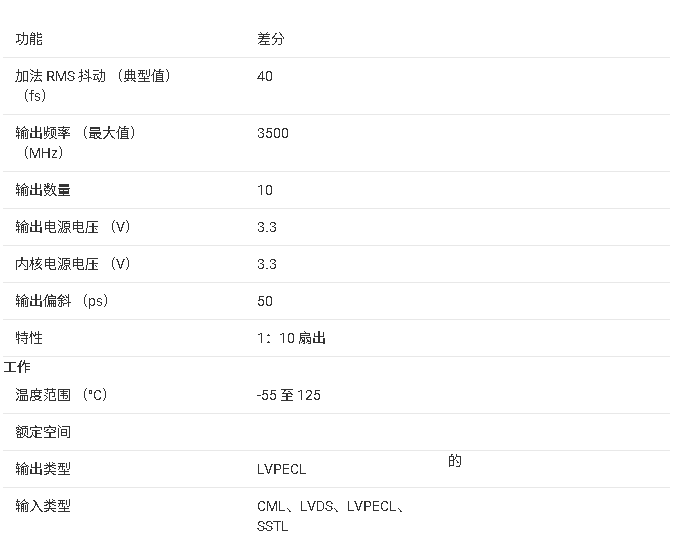

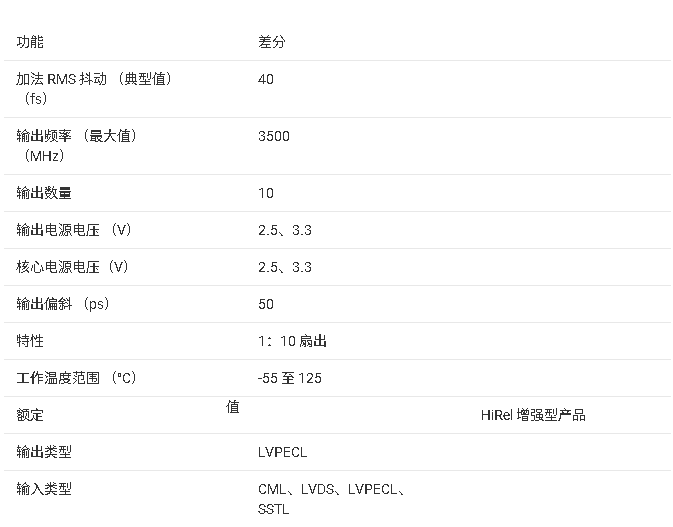

它还适用于国防、航空航天和医疗等对产品可靠性和性能要求极高的领域。产品具有受控基线、单一组装和测试地点、单一制造地点等特点,并且可在 -55°C 至 125°C 的军事温度范围内工作,同时具备延长的产品生命周期和产品变更通知,以及产品可追溯性等优势。

3. 功能与引脚解析

功能选择

通过 CLK_SEL 引脚可以选择不同的时钟输入。当 CLK_SEL 为 0 时,选择 CLK0 作为有效时钟输入;当 CLK_SEL 为 1 时,选择 CLK1 作为有效时钟输入。

引脚功能

该驱动器的引脚功能明确,CLK0 和 CLK1 为差分 LVECL/LVPECL 输入对;Q[9:0] 和 Q[9:0] 分别为 LVECL/LVPECL 时钟输出和互补时钟输出;VBB 为单端输入操作的参考电压输出;VCC 为电源电压;VEE 为设备接地或 ECL 模式下的负电源电压。同时,需要注意 CLKn、CLK_SEL 等引脚的上拉和下拉电阻值。

4. 电气特性分析

绝对最大额定值

在使用 CDCLVP111-EP 时,需要注意其绝对最大额定值,如电源电压(相对于 VEE)范围为 -0.3 至 4.6 V,输入电压范围为 -0.3 至 VCC + 0.5 V 等。超过这些额定值可能会对器件造成永久性损坏。

推荐工作条件

推荐的电源电压(相对于 VEE)范围为 2.375 至 3.8 V,推荐的工作结温范围为 -55°C 至 125°C。在这些条件下使用,能够确保器件的性能和可靠性。

直流电气特性

分别介绍了 LVECL 和 LVPECL 模式下的直流电气特性,包括电源内部电流、输出和内部电源电流、输入电流、内部生成的偏置电压、高低电平输入电压、输入幅度、共模电压、高低电平输出电压以及差分输出电压摆幅等参数。这些参数在不同的温度条件下会有所变化,设计人员需要根据实际应用场景进行合理选择。

交流电气特性

交流电气特性包括差分传播延迟、输出到输出偏斜、部件到部件偏斜、附加相位抖动、最大频率以及输出上升和下降时间等。其中,部分规格通过工作台表征保证,但在生产中不进行测试,设计人员在使用时需要特别关注。

5. 封装与订购信息

封装形式

产品采用 32 引脚 LQFP(VF)封装,同时提供了封装的热阻信息,如热阻结到环境(θJA)和热阻结到外壳(θJC)等,这些信息对于散热设计非常重要。

订购信息

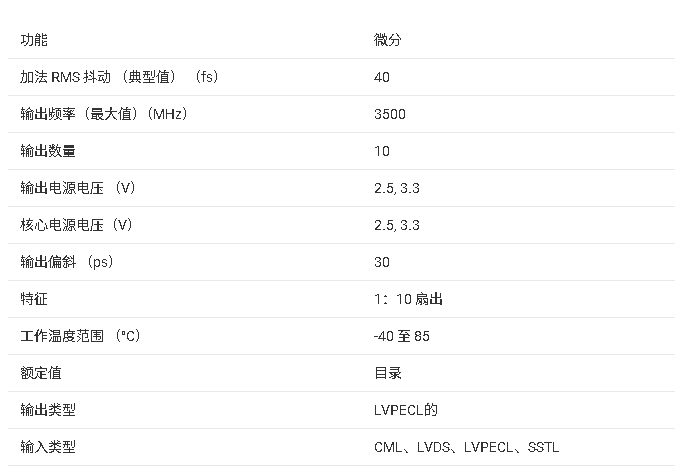

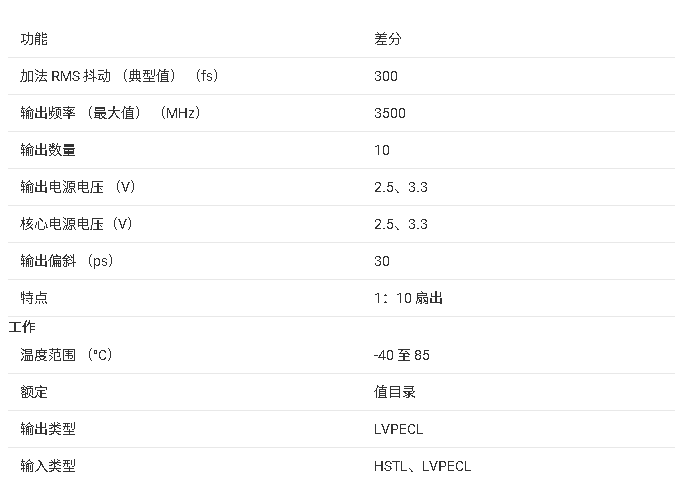

提供了特定温度范围(-55°C 至 125°C)下的可订购部件编号、顶部标记和 VID 编号等信息。同时,还给出了其他合格版本,如目录版 CDCLVP111 和太空版 CDCLVP111 - SP,它们分别适用于不同的应用场景。

6. 设计注意事项

ESD 保护

由于该器件内置的 ESD 保护有限,在存储或处理时,应将引脚短路在一起或将器件放置在导电泡沫中,以防止 MOS 栅极受到静电损坏。

输出引脚处理

当输出引脚不使用时,建议将其开路以降低功耗。如果只使用差分对中的一个输出引脚,则另一个输出引脚必须同样端接到 50 Ω。

工作模式选择

对于高达 3.5 GHz 的高速性能,强烈建议使用差分模式。如果需要单端输入操作,则使用 (V_{BB}) 参考电压输出,并将 VBB 引脚连接到 CLK0 并通过 10-nF 电容器旁路到 GND。

CDCLVP111-EP 作为一款高性能的时钟驱动器,具备多种优秀的特性和广泛的应用领域。电子工程师在进行硬件设计时,需要充分了解其特性和参数,结合实际应用场景进行合理设计和选择,以确保系统的稳定性和可靠性。大家在使用这款驱动器的过程中遇到过哪些问题呢?欢迎在评论区分享交流。

-

电子设计

+关注

关注

42文章

2954浏览量

49921 -

时钟驱动器

+关注

关注

0文章

124浏览量

14410

发布评论请先 登录

CDCLVP111-SP CDCLVP111-SP 具有可选输入时钟驱动器的低电压 1:10 LVPECL

CDCLVP111-EP 具有可选输入的 1:10 LVPECL 缓冲器

CDCLVP111-SP具有可选输入时钟驱动器的低电压1:10 LVPECL数据表

CDCLVP111低压1:10 LVPECL,内置可选输入时钟驱动器数据表

低电压 1:10 LVPECL 可选择输入时钟驱动器 CDCLVP111-EP 深度解析

低电压 1:10 LVPECL 可选择输入时钟驱动器 CDCLVP111-EP 深度解析

评论