芯片测试的本质是 “在原子级精度下,验证每一个晶体管的可靠性”。早年 28nm 及以上成熟制程,测试核心是 “筛选坏片”,流程相对简单;但随着制程进入 14nm 及以下,尤其是 3nm、2nm 节点,测试早已不是 “筛选” 那么简单,而是要应对工艺复杂度、工具一致性、公差极限等多重挑战,难度呈指数级攀升。

工艺复杂度的飙升,是测试难度增加的核心根源。正如 Onto Innovation 应用工程总监 PeiFen Teh 所说,先进节点需要数百道紧密关联的工艺步骤,从多重图案化、高介电常数 / 金属栅极,到选择性沉积、埋入式电源轨,每一步的微小缺陷都可能累积成良率灾难。一枚晶圆三个月内要经过 600-800 道工序,测试系统必须精准捕捉每一道工序的偏差,这对测试精度的要求已达到亚纳米级别 —— 比如 3nm 节点,套刻精度需要控制在 0.3nm 以内,相当于一根头发丝直径的百万分之一,这种极限精度,早已逼近测试设备的物理极限。

更棘手的是工具匹配(TTTM)的难度翻倍。芯片制造需要多台同型号设备协同工作,测试的前提是 “所有设备的输出结果一致”,这就是工具匹配的核心意义。但先进制程下,设备的 “个体差异” 被无限放大 —— 每台设备的腔室磨损、光学元件偏差、环境影响,都会导致测试结果出现非线性偏差。更关键的是,工具匹配并非一劳永逸:设备安装、工艺迭代、维护换件后,都需要重新匹配,先进节点甚至需要每天、每班多次匹配。

更具挑战的是,供应链的分散化让工具匹配雪上加霜。泰瑞达智能制造产品经理 Eli Roth 提到,如今半导体供应链遍布全球,不同晶圆厂、不同生产线的设备,需要实现测试结果的完全一致,这就要求不仅要匹配单厂内的设备,还要跨厂、跨区域匹配。更苛刻的是,先进封装技术将多颗芯片集成在一起,测试需要兼顾不同芯片的兼容性,误差来源呈几何级增加,对测试重复性的要求达到了前所未有的高度。

公差收紧与随机效应的凸显,让测试陷入 “两难困境”。随着特征尺寸缩小,芯片的线宽、线边缘粗糙度等随机效应,成为影响测试准确性的关键。Fractilia 联合创始人 Chris Mack 坦言,现在的测试很难达到 NIST 标准下的 “绝对准确”,只能追求极致的 “精度”—— 通过多次测量减少变异,但亚纳米级的公差的下,哪怕是微小的环境波动,都可能导致测试结果偏差,这也是英特尔 “完全复制” 晶圆厂流程,却仍出现差异的核心原因。

数据激增与机器学习的局限性,进一步加剧了测试难度。先进节点的测试会产生海量高分辨率数据,包括波形特征、时序测量、连续遥测数据等,传统的统计方法已无法处理这些高维数据。虽然机器学习能捕捉工具的细微非线性行为,辅助工具指纹识别和异常检测,但它并非 “万能解药”—— 它需要大量标注数据训练,且无法完全替代人工对复杂缺陷的判断,更多是传统测试方法的补充,而非替代。

除此之外,产品生命周期缩短、良率提升速度加快,也给测试带来了额外压力。新品导入(NPI)的时间不断压缩,工程师需要在更短的时间内完成测试方案验证、工具匹配和流程稳定,容错空间被无限压缩。同时,Chiplet、3D 堆叠等先进封装技术的普及,让测试从 “单一芯片测试” 转向 “系统级测试”,需要兼顾芯片间的互连可靠性、热稳定性等,测试维度大幅增加。

其实,芯片测试难度的飙升,本质上是半导体产业向 “原子级制造” 迈进的必然代价。测试不再是 “后端辅助”,而是贯穿制造全流程的 “良率守门员”—— 它既要捕捉工艺缺陷,也要保障设备一致性,还要应对供应链和技术迭代的挑战。

-

测试

+关注

关注

9文章

6374浏览量

131639 -

晶体管

+关注

关注

78文章

10434浏览量

148543 -

芯片测试

+关注

关注

6文章

181浏览量

21178

发布评论请先 登录

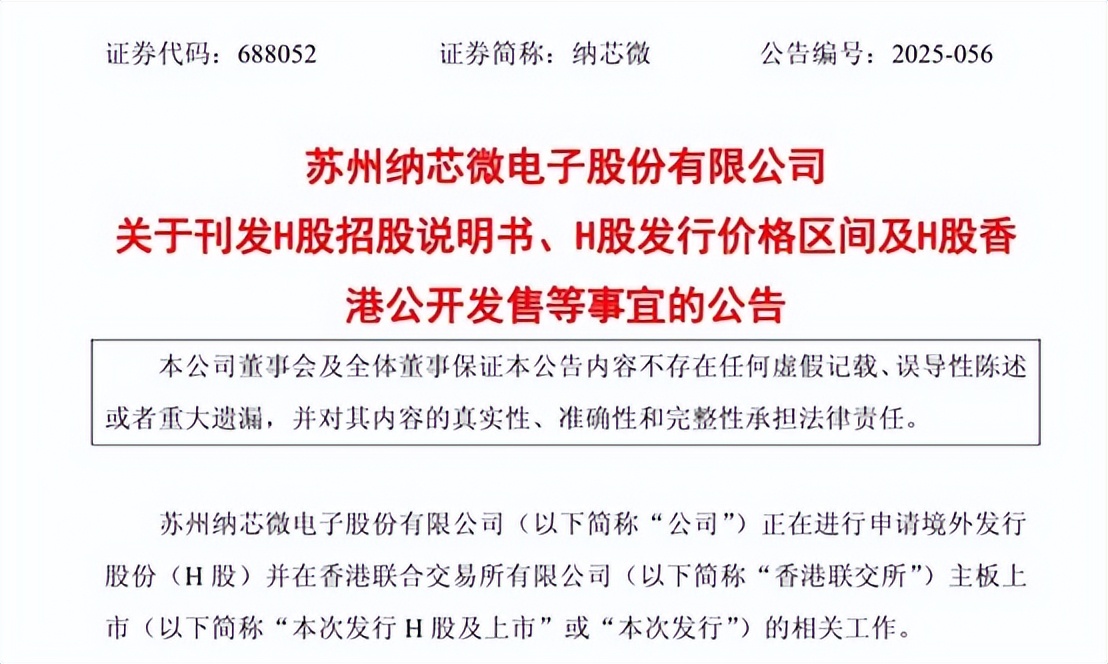

重磅来袭 | 纳芯微NS800RT7P65D评测活动开放,新品直播预约!

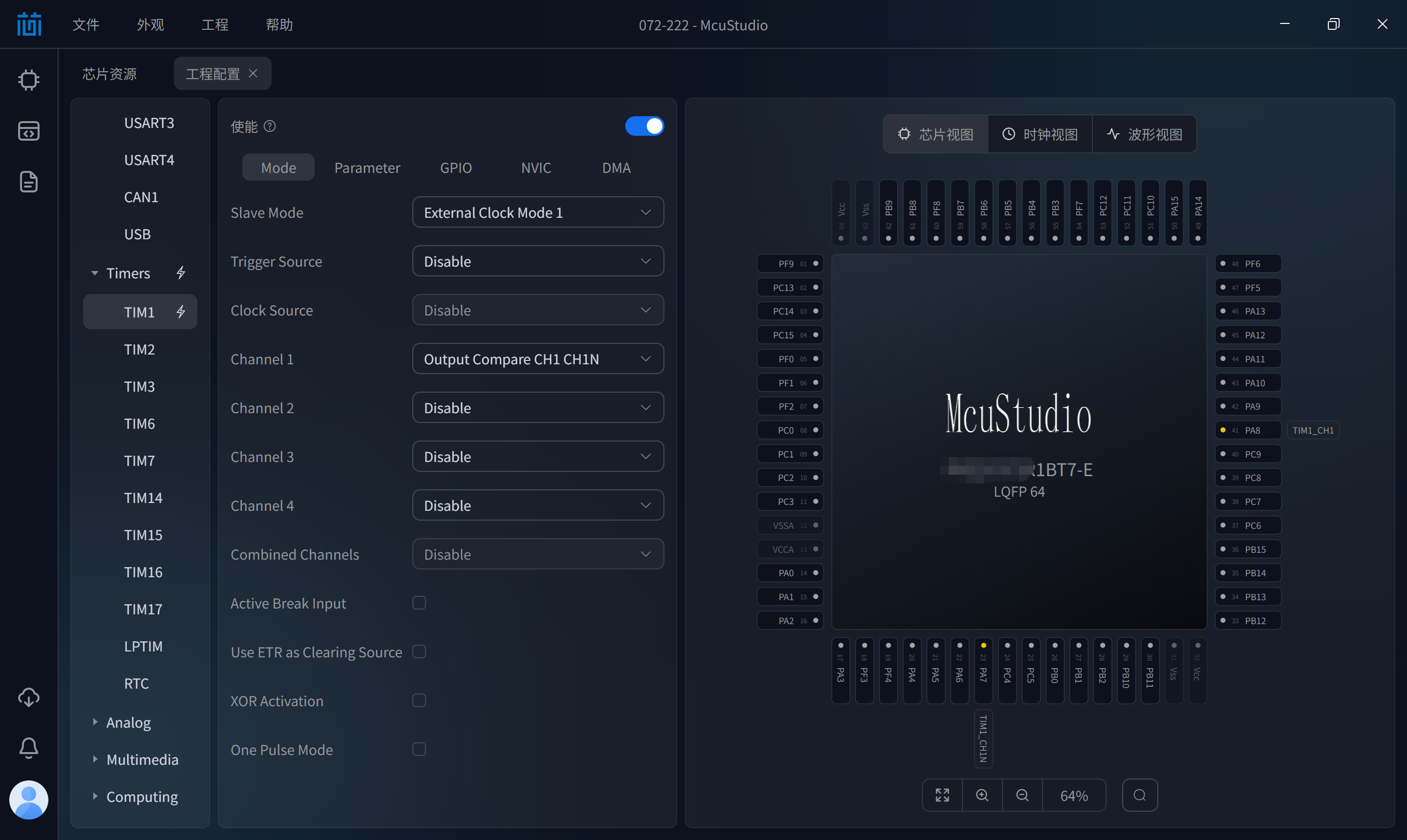

为什么原厂越来越需要一套自己的 Studio

为什么原厂越来越需要一套自己的 Studio

为什么机器人控制器越来越偏爱 RK3588?

纳芯微:不只产品领先,更以体系致胜

后摩尔时代:芯片不是越来越凉,而是越来越烫

全桥LLC的上管驱动芯片14、15总是短路,驱动芯片是那纳芯微的NSI6602A,请问各位前辈该怎么解决,感谢!!

芯片的验证为何越来越难?

【微纳谈芯】芯片测试越来越难的背后

【微纳谈芯】芯片测试越来越难的背后

评论