在智能手机、笔记本电脑、服务器,尤其是AI加速器芯片上,我们正在见证一个时代性的趋势:计算力不断攀升,芯片的热也随之“失控”。NVIDIA的Blackwell架构GPU芯片,整卡TDP功耗超过1500W,而在消费领域,旗舰显卡RTX 5090也首次引入了液态金属这一更高效但成本更高的热界面材料(TIM)。

为什么芯片越来越热?它的热从哪里来?芯片内部每一个晶体管在开关动作时的能量损耗,汇聚成了最终“无处安放的热量”。随着晶体管数量的飞涨和面积不断压缩,我们正面临着一个关键指标的持续抬升:热流密度(Heat Flux Density)。

虽然摩尔定律正在放缓,但芯片集成度却并未因此降低,尤其在台积电CoWoS、英特尔Foveros等先进封装技术的推动下,多芯粒堆叠和超高带宽互连正推动芯片走向前所未有的“热集中”时代。

那么,热是怎么产生的?过去这些年晶体管密度和热流密度如何变化?先进制程和封装是否会让芯片更热?这一期,我们来系统聊一聊。

01

热从哪里来?晶体管为什么发热

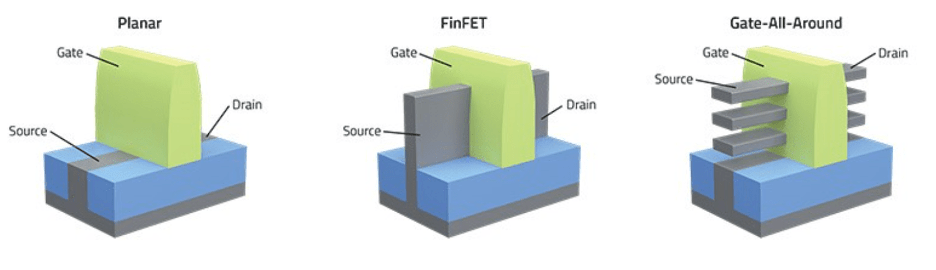

芯片之所以会发热,根源在于其内部成千上亿个晶体管在不断地“开”和“关”。在这个过程中,一部分电能不可避免地转化成热能。一个芯片中可能包含数十亿、甚至超过一万亿个晶体管。下图是当前常用的FinFET晶体管的结构,FinFET全称Fin Field-Effect Transistor,中文名叫鳍式场效应晶体管,是一种新的互补式金氧半导体晶体管。1999年,胡正明教授及其团队成员成功制造出第一个p型FinFET,它的栅长度只有18nm,沟道宽度15nm,鳍的高度50nm。这些万亿晶体管被集成在芯片里每天“开关自如”,运行着从搜索推荐到AI训练的复杂任务。

但每当晶体管切换状态时,它就消耗能量并释放热量。这个过程中主要涉及两个方面的功耗来源:

(1)动态功耗:当晶体管从关闭状态切换到打开状态,或从打开切换到关闭状态时,内部的电荷重新分布或复合,产生能量损耗,并以热的形式释放出来。这种过程称为动态功耗,是芯片运行时最主要的热量来源。它可以近似表示为:它可以被近似地表示为:P = α · C · V² · f;其中:α 是活动因子(代表多少晶体管在同时工作);C 是负载电容;V 是电压;f 是频率。可以看到,电压越高、频率越高,芯片的动态发热就越严重。这也是为何芯片“超频”时温度急剧上升。

(2)静态功耗:即使不工作也会漏电。即便晶体管处于“静止状态”,也仍有微弱电流泄漏,形成所谓的“静态功耗”,其来源包括:亚阈值漏电流(Subthreshold leakage)、闩锁电流(Gate leakage)、PN结反向偏置漏电(Junction leakage)。随着晶体管尺寸不断缩小,漏电流显著增加,成为芯片发热的“隐性杀手”。这也是当前制程演进中越来越难压低功耗的原因之一。

电能在晶体管工作中损耗后,大部分以热能的形式散发。这种能量转换不可逆,最终导致芯片温度升高。也就是说,不论是开关还是静止状态,晶体管都会发热,只是程度不同。

02

晶体管密度提升,热流密度同步飙升

1965年,英特尔创始人之一的戈登·摩尔提出了经典的摩尔定律, “每18个月性能提升一倍,价格降低一半”。过去几十年间,摩尔定律推动芯片性能飞速发展,这背后依赖的是制造工艺的不断进步,使晶体管的尺寸越来越小、密度越来越高。但随之而来的,是一个不可忽视的问题——热流密度的快速上升。

早期节点(比如130nm、90nm)时,晶体管密度和功耗提升是相对线性的,但进入65nm之后,漏电流的急剧上升让静态功耗成为了大问题。虽然工艺不断推进,但功耗墙(Power Wall)逐渐显现。

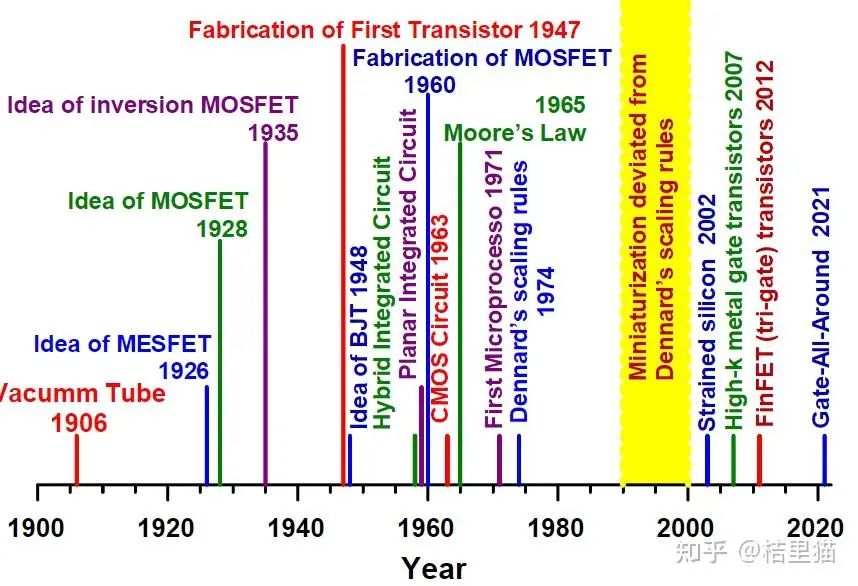

图3. 晶体管发展历史(图源:桔里猫)

与此同时,为了追求性能,芯片主频也不断升高——这意味着单位时间内的动态功耗暴增。而晶体管越密、芯片面积增长受限,结果就是:单位面积上的热功耗密度不断上升,热管理难度迅速加剧。

这里我们要明确两个概念:功耗(Power):整个芯片的总能耗,单位是瓦(W);热流密度(Power Density):单位面积上的功耗,单位是W/cm²或W/mm²。举个简单的例子:一块100W的CPU,面积为2cm²,则热流密度为50 W/cm²。

| 制程节点 | 晶体管密度 | 功耗密度 | 主频(GHz) |

|---|---|---|---|

| 90nm | ~10M | <30 | ~3 |

| 45nm | ~100M | ~80 | ~3.5 |

| 7nm | ~1000M | >100 | ~3.5-4 |

特别在7nm及之后,即使主频不再大幅提升,但密度和功耗依旧在上涨,热流密度成为设计瓶颈。如A100/A800 TDP是400W,芯片热流密度 50W/cm²;H100/H800 TDP是700W,热流密度87.5W/cm²,当下芯片热流密度已经远超风冷极限。

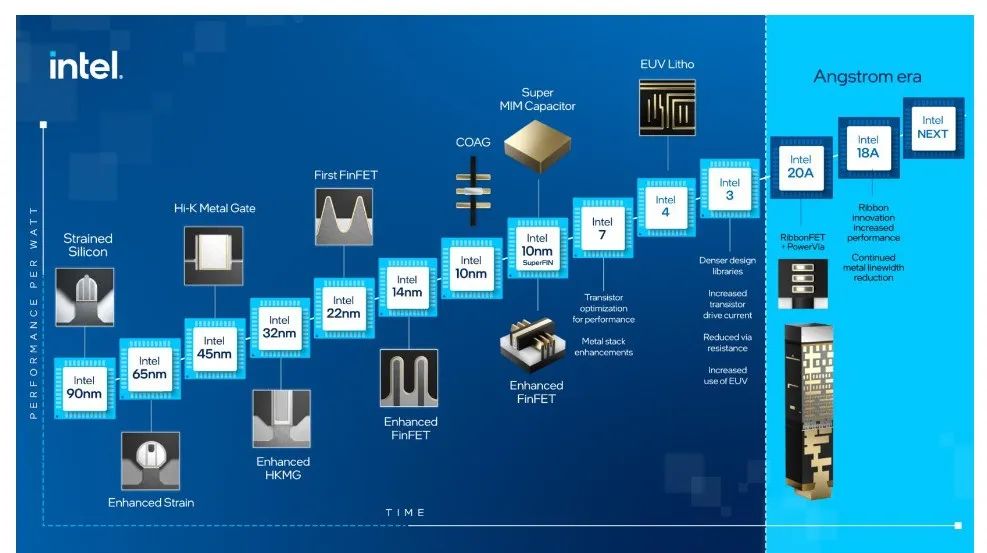

图4. Intel晶体管发展计划

早在20年前,英特尔前CTO和CEO帕特·盖尔辛格就放话说,如果芯片耗能和散热的问题得不到解决,当芯片上集成了2亿个晶体管时,就会热得像“核反应堆”,2010年时会达到火箭发射时高温气体喷射的水平,而到2015 年就会与太阳的表面一样热。

英伟达的B200芯片则达到了2080亿晶体管,功耗高达1000W+。如果按单位面积换算,芯片的热流密度早已超过核反应堆冷却板、钢铁冶炼炉,逼近火箭喷嘴。

03

GAA与先进封装:热流密度会再度飙升吗?

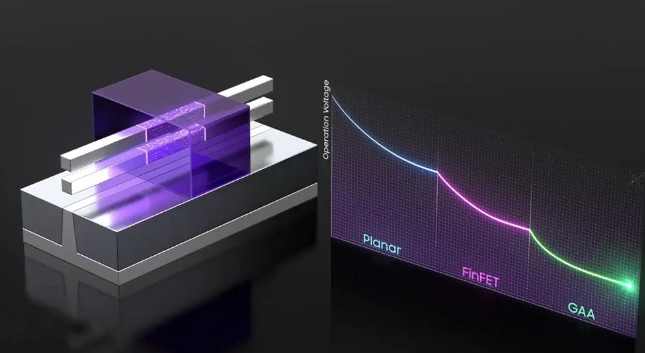

3.1从FinFET到GAA,热管理走入“精细博弈”

摩尔定律放缓后,热流密度会下降吗?在摩尔定律不断逼近物理极限的背景下,晶体管结构也在经历代际更替。FinFET(鳍式场效应晶体管)已经在10年内主导了芯片工艺的主流。但从2025年台积电N2、Intel18A以及三星SF2最新的产品架构看,几家头部大厂都开始转型GAA(全环绕栅极)晶体管。

图6. 从平面晶体管到FinFET再到GAA晶体管的转变(图源:Lam Research)

GAA的优势在于能更有效地控制漏电流、提升开关性能,是功耗控制的一大利器。但这项结构创新也带来了新的热挑战:

GAA晶体管单元结构更复杂、更精密,单位体积内的功耗密度更高;

多根纳米片堆叠形成通道,栅极完全包覆,热扩散路径更短、更局限;

晶体管栅长进一步缩小,亚阈值泄漏和量子穿隧效应成为主要发热来源。

总结:GAA让“每一个晶体管”都更高效了,但也更热了。

3.2 先进封装:热不再是“平均值”,而是“热点集中”与GAA晶体管技术几乎同步推进的,还有近年来蓬勃发展的先进封装技术。台积电的CoWoS、英特尔的Foveros、三星的I-Cube,都试图将多个芯粒(chiplets)以2.5D或3D方式进行堆叠、集成,提升带宽、降低延迟。但热管理难度也随之翻倍:

热点集中:AI芯片、HPC芯片往往在中间集成一颗大算力芯粒,形成局部极端高温区域;

热路径增长:上下堆叠的芯片彼此遮挡,芯片底部的热量更难传导到外部;

材料不匹配:封装中的TIM(热界面材料)、载板、芯粒之间存在热膨胀系数差异,导致界面热阻增大。

在B200这类AI芯片中,一颗核心芯粒+多颗HBM堆叠组成的“热岛”,不仅考验散热能力,也正在倒逼产业链重新设计整个热结构。

进入先进封装时代后多个高功耗芯片裸片被集成到同一封装基板上,在空间不变的情况下,热源集中度进一步提高,热流密度陡增。如果在先进封装中,热源面积被进一步“压缩”。这意味着传统的风冷方式可能无法满足需求,必须引入液冷、热管、3D冷却、甚至微射流等更激进的热管理方案。台积电已经开始在晶圆上尝试微射流的液冷方案,感兴趣的同学可以看上一期的文章。

AI芯片热到极限?CoWoS封装里藏着怎样的“散热”难题

04

结语与讨论:热管理,正在变成芯片设计的“第一门槛”?

曾经热设计是最后一公里的工程问题。而今天,在GAA+3D封装加持下的先进芯片,热设计已然走到产品开发的最前沿。

很多人以为,摩尔定律趋缓、频率不再提升,芯片的热密度问题应该会“缓一缓”。但事实上,进入3D异构集成时代后,热问题从“全局扩散”转向“局部灾难”:

提问:面对GAA与先进封装的双重推进,下一代热管理材料和冷却技术该如何跟上?欢迎大家在评论区分享你的看法同时留下你感兴趣的话题?

参考资料[1] 芯片热量如何产生的?,大米的老爹;[2] 芯片功耗是否都转换为热量,百科;[3] 一文了解晶体管发展历程,半导体全解;[4] FinFET交棒GAA?关于GAA制程技术必须知道的事,EDN电子技术设计;

[4]半导体制程从180nm到14nm技术演进总结,半导体小马;

-

芯片

+关注

关注

463文章

54441浏览量

469425 -

晶体管

+关注

关注

78文章

10441浏览量

148616 -

后摩尔时代

+关注

关注

0文章

13浏览量

9343

发布评论请先 登录

电源“免疫力”决定芯片稳定性:PSRR测试为何越来越关键

【微纳谈芯】芯片测试越来越难的背后

为什么AI数据中心越来越依赖电流监测?

为什么原厂越来越需要一套自己的 Studio

为什么原厂越来越需要一套自己的 Studio

为什么机器人控制器越来越偏爱 RK3588?

为何Type-C越来越受欢迎?

负载越来越大,传统互感器为什么开始拖企业用电管理的后腿?

Windows 在工厂里为什么越来越少见?答案只有两个字:Linux

FPGA技术为什么越来越牛,这是有原因的

PCB为啥现在行业越来越流行“浅背钻”了?

后摩尔时代破局者:物元半导体领航中国3D集成制造产业

芯片的验证为何越来越难?

后摩尔时代:芯片不是越来越凉,而是越来越烫

后摩尔时代:芯片不是越来越凉,而是越来越烫

评论