数字信号处理(DSP)是FPGA和SoC的常见应用领域。为了在此领域为客户提供最优服务,Enclustra积累了深厚的DSP专业知识,不仅能提供纯粹的实现服务,更能从零开始支持架构与算法设计,甚至在项目初期阶段提供需求工程支持及全程咨询服务。如果您已有目标构想却尚未确定架构或具体规格?无需担忧。Enclustra可与您紧密协作,共同定义最优架构方案!

我们将与您深入探讨各类实现方案(滤波架构、数值格式等)及其权衡取舍,确保所有决策均有充分依据,避免项目后期出现遗憾。Enclustra精通各类主流开发工具与编程语言。无论您偏好Python、MATLAB、Simulink、SciLab、C/C++还是.NET/C#:我们皆能驾轻就熟。

DSP开发流程

标准的Enclustra DSP开发流程包括在开始FPGA/SoC实现之前创建Python或MATLAB位真模型。通过自检单元测试验证模型与实现的匹配性。位真模型使您能在项目早期(甚至FPGA/SoC实现启动前)评估精确的处理行为与性能。由此可避免在实际FPGA/SoC实现阶段进行高成本的迭代,显著降低项目风险。若客户有特殊需求,我们亦可遵循其定义的开发流程。

DSP应用领域

为什么选择Enclustra?

100%项目成功率

基于位真模型的流程确保低项目风险

从理论到实践的深厚DSP技术积淀

我们开发——您拥有!

-交付全部源代码及知识产权

-项目结束时进行技术知识转移

灵活高效的客户紧密协作模式

瑞苏盈科DSP交钥匙FPGA设计解决方案

Enclustra将数字信号处理与FPGA/SoC技术专长独特结合。由此实现算法的优化设计部署,有效降低资源消耗与功耗,最终实现整体成本节约。我们还具备将定制算法以RTL或HLS形式手工编码的专业技术与经验。同时,针对通用操作采用专有及开源库,实现低开发成本。

我们提供从概念到实施的交钥匙项目,同时也乐于在整个项目过程中与客户紧密协作,以实现最佳灵活性。Enclustra可专注于概念设计、现有算法的实现,或两者兼顾。

您的成功就是我们的目标。没有人比您更了解您的应用场景,我们的使命是协助您将专业知识以最优方式转化为代码行、LUT和DSP切片。

-

dsp

+关注

关注

561文章

8269浏览量

368143 -

FPGA

+关注

关注

1663文章

22493浏览量

638939 -

算法

+关注

关注

23文章

4800浏览量

98502 -

soc

+关注

关注

40文章

4619浏览量

230079

发布评论请先 登录

Enclustra将亮相2026年美国FPGA Horizons展

Altera Agilex FPGA与SoC实现更智能的AI

倒计时开始!Embedded World 2026,Enclustra邀你见证FPGA/SoC与物理AI的未来

基于DSP与FPGA异构架构的高性能伺服控制系统设计

如何用FPGA控制ADV7513实现HDMI画面显示和音频播放

Altera Agilex 5 D系列FPGA和SoC家族全面升级

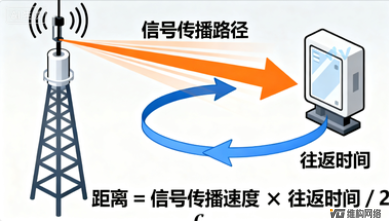

蓝牙定位技术原理:从BLE信号到高精度定位的实现逻辑

Altera Agilex 3 FPGA和SoC产品家族的性能分析

【技术讨论】智能戒指手势交互:如何优化PCBA成本与实现<20ms低延迟?

基于FPGA的压缩算法加速实现

从算法到部署:Enclustra如何用DSP+FPGA/SoC专长,实现功耗与成本双优化?

从算法到部署:Enclustra如何用DSP+FPGA/SoC专长,实现功耗与成本双优化?

评论