说起来,FPGA功耗优化这个话题,在圈子里属于那种"都知道重要,但真到实战又不知道从哪下手"的类型。每次项目收尾,看到功耗报告里那些数字,很多工程师朋友估计跟我一样——头皮发麻。

今天想跟大伙儿聊聊一个相对冷门但效果显著的角度:翻转率(Toggle Rate)。这玩意儿听起来挺学术,但理解透了之后,你对功耗的把控能力会上一个台阶。

功耗到底花在哪了?先搞清楚这个

在说翻转率之前,咱们得先把FPGA功耗的账算清楚。FPGA的功耗主要由两部分构成:静态功耗和动态功耗。静态功耗说白了就是"漏电"——芯片上电了但没干活,晶体管照样有漏电流在跑。这部分跟工艺、温度关系比较大,咱们今天不重点聊。

重点是动态功耗,这玩意儿占到总功耗的60%~80%,是真正的"用电大户"。动态功耗的来源就是信号翻转——当电平在0和1之间跳来跳去的时候,FPGA内部的电容在反复充放电,这就要耗电。

有个经典公式,大家可以记一下:

动态功耗 = α × C × V² × f

其中:

·α(Alpha)= 翻转率,也就是每个时钟周期信号翻转的平均次数

·C= 负载电容,跟布线长度、资源用量有关

·V= 供电电压

·f= 工作频率

FPGA功耗中,动态功耗占比高达60%~80%

从公式可以看出,翻转率α是跟功耗成正比的。如果能把翻转率降下来,功耗就能直接降下来。这事儿说着简单,做起来其实有不少门道。

翻转率是个什么鬼?

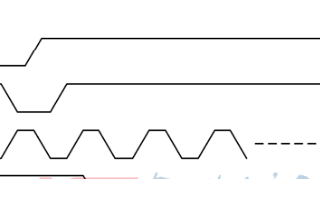

翻转率描述的是信号在单位时间内翻转(0→1或1→0)的次数。举个例子:一个信号每个时钟周期都翻转一次,那它的翻转率就是100%;如果每两个周期才翻一次,翻转率就是50%。

在FPGA里,不同信号的翻转率差异巨大:

| 信号类型 | 典型翻转率 | 功耗贡献 |

|---|---|---|

| 时钟信号 | 100%(每个周期都翻) | 极高(占动态功耗20%+) |

| 高频计数器高位 | 50%~100% | 高 |

| 数据总线 | 取决于数据模式 | 中等 |

| 控制信号 | 通常较低 | 低 |

| 空闲模块输入 | 不可控(毛刺!) | 容易被忽略的"电老虎" |

翻转率与动态功耗呈线性正相关关系

有意思的是,时钟信号虽然只占信号总数的很小一部分,但因为它每个周期都在翻,而且时钟网络的扇出极大、负载很重,所以时钟本身的功耗能占到整个FPGA动态功耗的20%以上。这就是为什么时钟管理是低功耗设计的"七寸"。

实战技巧一:状态机编码的门道

状态机可以说是FPGA设计里最常见的结构了,但很多人在写状态机的时候,根本没考虑过编码方式对功耗的影响。

咱们来对比一下三种常见的编码方式:

| 编码方式 | 状态跳转时翻转位数 | 功耗表现 | 适用场景 |

|---|---|---|---|

| 二进制编码 | 多位同时翻(如0111→1000会翻4位) | 高 | 状态少、低频简单控制 |

| 格雷码编码 | 固定1位 | 低 | 状态多、异步系统、计数器 |

| 独热码(One-Hot) | 固定2位(1→0 + 0→1) | 低 | 高速场景、状态数≤16 |

不同状态编码方式的翻转位数对比

我之前踩过一个坑:有个项目需要实现一个16状态的状态机,我图省事直接用了二进制编码。结果一跑功耗分析,光状态寄存器就吃了不少功耗。后来改成格雷码,单是状态跳转这一块,功耗就降了将近30%。

格雷码的好处在于相邻状态之间永远只有1位翻转,不会像二进制编码那样出现多位同时跳变的情况。对于状态数比较多的场景,这个优化效果非常明显。

小提示:如果状态数刚好是2的幂(比如8、16、32),格雷码实现起来最自然。如果不是2的幂,可能需要做一些额外处理,但值得。

实战技巧二:时钟使能,别再用组合逻辑门控了

说到降低翻转率,时钟门控是个绕不开的话题。但我发现有些工程师朋友还在用这种写法:

// 这种写法看起来像门控时钟,但实际上会有毛刺问题! assign gated_clk = enable ? clk : 1'b0;

这种组合逻辑实现的"门控时钟"简直是功耗和时序的双重噩梦。毛刺会在时钟上产生额外的窄脉冲,导致寄存器行为不可预测,而且这些窄脉冲也会消耗额外的动态功耗。

正确做法是用器件提供的专用时钟门控单元(ICG, Integrated Clock Gating)或者时钟使能信号(Clock Enable)。在Xilinx的FPGA里,可以这样写:

// 推荐写法:使用时钟使能 always @(posedge clk or negedge rst_n) begin if (!rst_n) data_reg <= 8'b0; else if (enable_signal) // 只有使能有效时才翻转 data_reg <= data_in; end

现代综合工具会自动识别这种模式,并利用芯片内置的ICG单元来实现低功耗门控。这种方式不会产生毛刺,时序也更安全。

还有一个细节:时钟使能阻止的是寄存器的翻转,但时钟树本身还在跑。对于一些需要彻底关闭的场景(比如某个模块长时间不用),可以考虑使用BUFGMUX来直接切断时钟树,这能把该区域的时钟功耗直接降到接近零。

实战技巧三:操作数隔离,防止"无效忙碌"

这个问题可能很多人没注意到:当某个模块处于空闲状态时,它的输入端可能还在接收数据或者受到噪声干扰,导致内部逻辑持续在做无意义的翻转。

举个例子,你有一个乘法器模块,只有当valid信号为高时才应该工作。但如果没有做操作数隔离,当valid为低时,乘法器的输入端可能还是随机变化,导致它白做功。

解决方案是在模块空闲时锁定输入信号:

// 操作数隔离示例 wire [7:0] a_safe = module_enable ? a : 8'b0; wire [7:0] b_safe = module_enable ? b : 8'b0; // 只有使能时才让乘法器工作 assign result = module_enable ? (a_safe * b_safe) : 32'b0;

这样一来,当模块空闲时,输入端被固定在确定电平,不会产生无效翻转。

实战技巧四:总线数据编码的门道

对于数据总线,其实也有一些可以减少翻转的编码技巧。特别是当总线在相邻数据之间变化时,如果能预测这种变化模式并做一些处理,可以显著降低翻转率。

一个经典的做法是位反转编码:

// 简单示例:比较前后数据,如果翻转位超过一半就反转整个字 wire [7:0] data_xored = data ^ data_prev; wire [2:0] bit_count = count_bits(data_xored); // 如果翻转位超过4位,反转编码 wire need_invert = bit_count > 3'd4; wire [7:0] encoded_data = need_invert ? ~data : data; wire encoding_bit = need_invert;

这个技巧在高速SerDes接口或者存储器数据总线中用得比较多,能把有效翻转率降低30%~50%。

怎么验证优化效果?

说了这么多技巧,大家肯定关心:怎么知道自己优化到位了?

这里给大家推荐几个方法:

1. Vivado/Xilinx平台:综合实现完成后,运行report_power命令生成功耗报告。重点关注这几个指标:

| 指标 | 关注原因 |

|---|---|

| Clocking功耗占比 | >40%说明时钟树过大,优化空间大 |

| Top Switching Nets | 找出翻转率异常高的信号 |

| Power by Resource Type | Logic/BRAM/DSP/IO的功耗分布 |

2. 仿真加翻转率注解:在Vivado里可以对仿真生成的SAIF文件进行功耗估算,这样能得到更接近实际工作场景的翻转率数据。

3. 功耗优化前后对比:这个最直接。我一般会记录优化前后的功耗数据,做成表格,这样能清楚地看到每项优化的实际贡献。

一个真实的优化案例

给大家分享一个我之前做的项目:图像处理流水线,里面有个状态机控制LED指示灯。

优化前后实测数据对比

原始设计:

| 指标 | 优化前 | 优化后 | 提升 |

| 状态翻转位数 | 平均1.5位/次 | 1位/次 | ↓33% |

| 无效时钟翻转 | 100% | 空闲时0翻转 | 显著下降 |

| 实测总功耗 | 120mW | 82mW | ↓31.6% |

其实改动不大:状态机从二进制改成格雷码,加了时钟使能控制。就这两招,功耗降了将近三分之一。

总结一下

翻转率优化要点

理解公式 :P = α × C × V² × f,翻转率α跟功耗成正比

状态机编码 :优先考虑格雷码或独热码,减少状态跳转时的翻转

时钟门控 :用ICG/CE等硬件机制,不要用组合逻辑直接门控

操作数隔离 :让空闲模块的输入固定,避免无效翻转

善用工具 :功耗报告是优化的指南针,看懂它才能精准发力

最后说一句,功耗优化不是一蹴而就的事,也不是单靠某个技巧就能搞定。它需要咱们在设计早期就有低功耗的意识,然后在RTL编码、约束设置、实现优化这几个环节都把好关。

希望今天分享的这些心得对大家有帮助。如果你们在实际项目里有什么好的优化经验或者踩过的坑,欢迎在评论区聊聊~

—— 专注FPGA,分享实战经验

-

FPGA

+关注

关注

1663文章

22493浏览量

638939 -

功耗

+关注

关注

1文章

844浏览量

33335 -

状态机

+关注

关注

2文章

501浏览量

29315

原文标题:FPGA功耗优化新思路,从翻转率入手能省多少电

文章出处:【微信号:FPGA研究院,微信公众号:FPGA研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

面对竞争 Lattice持续优化FPGA成本和功耗

单粒子翻转引起SRAM型FPGA的故障机理阐述

从翻转率入手优化FPGA功耗

从翻转率入手优化FPGA功耗

评论