CDCE62005:高性能时钟发生器与分配器的深度剖析

在电子设计领域,时钟发生器和分配器的性能对系统的稳定性和可靠性起着关键作用。今天,我们就来深入探讨德州仪器(TI)的CDCE62005,一款高性能的时钟发生器和分配器,看看它在实际应用中能为我们带来哪些优势。

文件下载:cdce62005.pdf

产品概述

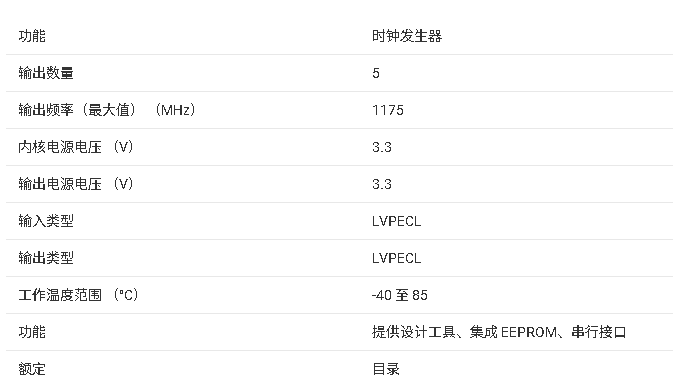

CDCE62005是一款具备低输出抖动特性的时钟发生器和分配器,它通过SPI接口实现高度可配置性,并借助片上EEPROM确定可编程启动模式。该器件特别适用于为数据转换器和高速数字信号提供时钟,在10 kHz至20 MHz的积分带宽内,抖动性能可轻松低于1 ps RMS。

产品特性亮点

卓越性能

- 低噪声时钟发生器:在10 kHz至20 MHz的积分带宽内,典型值为550 fs rms((F_{C}=100 MHz)),为系统提供了极为稳定的时钟信号。

- 低噪声抖动清洁器:同样在10 kHz至20 MHz的积分带宽内,典型值为2.6 ps rms((F_{C}=100 MHz)),有效降低了时钟信号中的抖动,提高了系统的稳定性。

灵活的频率规划

- 5个完全可配置的输出:支持LVPECL、LVDS、LVCMOS和特殊高摆幅输出模式,满足不同应用场景的需求。

- 独特的双VCO架构:支持1.750 GHz至2.356 GHz的宽调谐范围,输出频率在合成器模式下为4.25 MHz至1.175 GHz,扇出模式下可达1.5 GHz。

- 独立的粗斜控制:所有输出都具备独立的粗斜控制功能,方便工程师进行精确的时钟信号调整。

高度灵活性

应用领域广泛

CDCE62005的应用领域十分广泛,涵盖了无线基础设施、交换机和路由器、医疗电子、军事和航空航天以及工业等多个领域。在这些领域中,它能够为系统提供稳定、低抖动的时钟信号,确保系统的正常运行。

详细功能解析

功能模块组成

CDCE62005主要由接口和控制块、输入块、输出块和合成器块四个主要模块组成。

- 接口和控制块:基于片上EEPROM的内容确定设备在电源启动时的状态,同时提供SPI端口,允许在电源启动后直接写入设备寄存器进行配置。

- 输入块:选择三个输入端口中的一个供合成器块使用,并对所有时钟输入进行缓冲。

- 输出块:提供五个独立的时钟通道,可完全编程和配置,以选择和调节四个内部时钟源之一。

- 合成器块:对输入块选择的输入时钟进行乘法和滤波处理。

关键特性分析

相位噪声分析

文档中给出了不同参考输入下的设备输出相位噪声数据,如在30.72 MHz外部参考和25 MHz晶体参考下的相位噪声表现。这些数据对于评估设备在不同应用场景下的性能至关重要,工程师可以根据实际需求选择合适的参考输入。

输出到输出隔离

通过测试不同频率下的输出到输出隔离度,确保了各个输出之间的独立性,减少了相互干扰,提高了系统的稳定性。

设备控制

CDCE62005具有多种操作状态,如电源复位、校准保持、VCO校准、活动模式、电源关闭、睡眠和同步等。每个状态都有明确的进入和退出条件,工程师可以根据实际需求进行灵活控制。

外部控制引脚

REF_SEL、Power_Down和SYNC等外部控制引脚为工程师提供了方便的控制手段。REF_SEL可通过外部信号在主参考输入和次参考输入之间切换;Power_Down引脚可将设备置于电源关闭状态,并在释放后将EEPROM内容加载到RAM中;SYNC引脚可同步所有输出分频器,确保输出时钟的同步性。

输入块

输入块包括两个通用输入缓冲器、一个辅助输入和一个智能多路复用器。通用输入缓冲器支持多种格式和不同的终端和耦合方案,智能多路复用器可实现可编程的切换机制,提高了系统的容错能力。

输出块

输出块包含五个相同的输出通道,每个通道由输出多路复用器、时钟分频器模块和通用输出缓冲器组成。输出多路复用器可选择四个时钟源之一,时钟分频器模块支持多种分频比,通用输出缓冲器支持LVPECL、LVDS和LVCMOS模式。

合成器块

合成器块提供了锁相环、部分集成的可编程环路滤波器和两个压控振荡器(VCO)。通过合理配置输入分频器、反馈分频器和预分频器等参数,可以实现不同的输出频率。

编程与配置

SPI接口

CDCE62005通过SPI接口进行编程和配置。SPI接口由SPI_CLK、SPI_MOSI、SPI_MISO和SPI_LE四个信号组成,支持写RAM、读命令、将RAM复制到EEPROM(解锁)和将RAM复制到EEPROM(锁定)等命令。

寄存器映射

文档详细介绍了9个28位宽的寄存器的功能和配置方法,包括输出多路复用器选择、输出分频器比率选择、粗相位调整等。工程师可以根据实际需求对这些寄存器进行配置,以实现所需的功能。

应用与实现

频率合成器

CDCE62005内部的PLL结构使得VCO时钟能够与参考时钟输入同步,从而实现所有时钟输出的同步。通过合理配置输入分频器、预分频器、反馈分频器和输出分频器等参数,可以实现多种频率的合成。

典型应用

以一个典型的应用为例,需要产生两个156.25-MHz的LVPECL时钟、两个125-MHz的LVDS时钟和两个25-MHz的LVCMOS时钟,并与25 MHz的背板输入参考时钟锁相。通过详细的设计步骤,我们可以确定输入、预分频器、反馈和输出分频器的值,以及VCO的锁定频率和其他相关PLL设置。

电源供应与布局建议

电源供应

CDCE62005是一款高性能设备,因此在电源配置和PCB布局方面需要特别注意。文档提供了各个内部模块的功耗数据,工程师可以根据实际使用的模块数量计算总功耗,从而确定所需的热管理措施。

布局建议

为了确保设备的性能,文档给出了电源旁路电容器的推荐布局,建议将电容器与设备的电源连接尽可能短,并使用低阻抗连接将电容器的另一侧接地。同时,采用7×7填充过孔模式的PCB布局可以提高热性能和电源连接的稳定性。

总结

CDCE62005作为一款高性能的时钟发生器和分配器,凭借其卓越的性能、灵活的频率规划和高度的可配置性,在多个应用领域中具有广泛的应用前景。通过深入了解其功能和特性,工程师可以更好地利用这款设备,为系统设计提供稳定、可靠的时钟解决方案。在实际应用中,我们还需要根据具体需求进行合理的配置和布局,以充分发挥其优势。你在使用CDCE62005或类似设备时遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

时钟发生器

+关注

关注

1文章

358浏览量

70163

发布评论请先 登录

CDCE62005:高性能时钟发生器与分配器的深度剖析

CDCE62005:高性能时钟发生器与分配器的深度剖析

评论