CDCE18005:高性能可编程时钟缓冲器的深度剖析

在电子设计领域,时钟信号的稳定性和灵活性对于系统的性能至关重要。TI的CDCE18005作为一款五/十输出时钟可编程缓冲器,为我们提供了出色的解决方案。下面将对其进行详细解读,希望能为各位工程师在实际设计中提供有价值的参考。

文件下载:cdce18005.pdf

1. 产品概述

CDCE18005是一款适用于数据转换器和高速数字信号时钟缓冲的高性能时钟分配器。它通过SPI接口实现高度可配置性,并由片上EEPROM确定可编程启动模式,能实现低至50 fs RMS的低附加抖动。该器件可配置为提供不同输出格式(LVPECL、LVDS、LVCMOS)的组合,每个输出还能编程为独特的输出频率(最高达1.5 GHz)和偏斜关系。

2. 关键特性分析

2.1 输入灵活性

- 通用输入缓冲器:可接受LVPECL、LVDS或LVCMOS电平信号,支持高达1500 MHz(LVPECL)、800 MHz(LVDS)或250 MHz(LVCMOS)的频率,为不同信号源提供了广泛的兼容性。

- 辅助输入:可连接2 MHz - 42 MHz的晶体,支持时钟生成模式,为系统提供稳定的时钟源。

2.2 输出可配置性

- 输出格式多样:支持LVPECL、LVDS、LVCMOS和特殊高输出摆幅模式,可根据不同的应用需求灵活选择。

- 独立输出分频器:支持1 - 80的分频比,每个输出都能实现独立的频率配置,非常适合对时钟频率要求各异的系统。

- 输出偏斜控制:所有输出都具备独立的粗偏斜控制功能,能够满足对时钟相位要求严格的设计。

2.3 低抖动性能

CDCE18005具有低附加抖动性能,能够有效减少时钟信号的抖动,提高系统的稳定性和可靠性,这在高速数据传输和处理系统中尤为重要。

2.4 集成EEPROM

集成的EEPROM可在电源启动时确定设备配置,方便用户进行预先设置,减少系统启动时间,提高系统的自动化程度。

3. 功能模块详解

3.1 接口和控制模块

该模块主要包括SPI接口、两个控制引脚、非易失性存储器阵列(EEPROM)和静态RAM(设备寄存器)。其中,SPI接口是一个简单的双向接口,用于与设备寄存器进行读写操作。EEPROM用于存储默认配置数据,在设备启动时,其内容会被复制到设备寄存器中。通过SPI接口,用户可以在设备启动后对寄存器进行配置,从而改变设备的工作模式。

3.2 输入模块

输入模块包含两个通用输入缓冲器和一个辅助输入。它的主要作用是缓冲三个时钟信号,并将它们转换为差分信号,然后驱动到内部时钟分配总线上。这样,内部时钟分配总线上的时钟信号可以出现在设备的任何或所有输出上,为输出模块提供了丰富的时钟源选择。

3.3 输出模块

输出模块由五个相同的输出通道组成,每个通道包括一个输出多路复用器、一个时钟分频模块和一个通用输出缓冲区。

- 输出多路复用器:从内部时钟分配总线上的四个时钟源中选择一个提供给时钟分频模块,为每个输出通道提供灵活的时钟源选择。

- 时钟分频模块:每个通道都有一个7位的分频器和数字相位调整块,可实现1 - 80的分频比,并能对输出时钟的相位进行调整。通过数字相位调整功能,可以根据需要精确调整输出时钟的相位,满足不同系统对时钟相位的要求。

- 通用输出缓冲区:支持LVPECL、LVDS和LVCMOS三种输出模式,可根据具体需求进行配置。

4. 电气特性与性能指标

4.1 绝对最大额定值

了解器件的绝对最大额定值对于正确使用和保护器件至关重要。CDCE18005的电源电压范围为 -0.5 to 4.6 V,输入和输出电压范围为 –0.5 to VCC + 0.5 V,最大结温为125°C等。在设计过程中,必须确保器件的工作条件在这些额定值范围内,以避免器件损坏。

4.2 热特性

对于QFN(RGZ)封装,其热阻特性与气流和布局有关。在静止空气和100 LFM气流环境下,不同布局的热阻有所不同。合理的PCB布局可以有效降低器件的热阻,提高器件的散热性能,从而保证器件在高温环境下的稳定工作。

4.3 电气特性

在不同的输出模式(LVPECL、LVDS、LVCMOS)下,CDCE18005具有不同的电气特性,如输出频率、输出摆幅、传播延迟、偏斜等。这些特性会影响时钟信号的质量和系统的性能,在设计中需要根据具体应用进行合理配置。例如,在高速数据传输系统中,需要选择较低的传播延迟和偏斜的输出模式,以确保数据的准确传输。

5. 配置与使用技巧

5.1 SPI接口操作

CDCE18005的SPI接口用于配置设备寄存器,实现对设备的各种功能配置。SPI接口包括SPI_CLK、SPI_MOSI、SPI_MISO和SPI_LE四个信号。在进行读写操作时,需要注意信号的时序关系,确保数据的正确传输。例如,SPI_LE的下降沿会启动一次传输,数据在SPI_CLK的上升沿进行采样,而数据的转换则发生在SPI_CLK的下降沿。

5.2 设备寄存器配置

设备寄存器共有九个28位宽的寄存器,它们决定了设备的配置。每个寄存器的不同位对应着不同的功能,如输出多路复用器选择、分频比设置、输出模式选择等。在配置寄存器时,需要仔细参考数据手册,确保每个位的设置符合设计要求。例如,如果需要将某个输出通道的时钟源设置为PRI_REF,则需要在相应的寄存器中设置OUTMUXnSELX和OUTMUXnSELY位为“00”。

5.3 晶振输入接口

CDCE18005支持晶振输入,推荐使用基模振荡模式和并联谐振电路。在计算晶振的负载电容时,需要考虑片上负载电容、晶振杂散电容和电路板寄生电容等因素,以确保晶振能够在预期参数范围内正常振荡。同时,良好的PCB布局对于晶振的稳定工作也非常重要,应尽量减少晶振与AUX_IN引脚之间的布线距离,避免其他信号穿过振荡器电路,以减少干扰和杂散电容的影响。

6. 应用案例分享

6.1 扇出缓冲器模式

在这种模式下,每个输出可以配置为扇出缓冲器(分频器旁路)或具有分频和偏斜控制功能的扇出缓冲器。当分频器旁路时,输出频率最高可达1500 MHz;否则,最高可达1175 MHz。这种模式适用于需要将一个时钟信号分配到多个负载的应用场景,如数据采集系统中的多个ADC模块。

6.2 晶振输入时钟缓冲模式

CDCE18005可以通过晶振输入生成5 - 10个低噪声时钟信号,为系统提供稳定的时钟源。这种模式在对时钟稳定性要求较高的应用中非常有用,如通信基站中的时钟分配系统。

6.3 混合模式时钟分配

CDCE18005可以作为时钟开关,接受LVDS和晶振输入,并驱动LVDS、LVPECL和LVCMOS输出。例如,在一个复杂的通信系统中,它可以同时为不同的模块提供不同类型和频率的时钟信号,实现时钟的高效分配。

7. 总结与建议

CDCE18005作为一款高性能的时钟可编程缓冲器,具有输入灵活、输出可配置、低抖动等优点,适用于各种对时钟信号要求较高的应用场景。在实际设计过程中,需要充分考虑器件的电气特性、热特性和配置方法,合理进行PCB布局和电源旁路设计,以确保器件的性能和可靠性。同时,对于一些关键参数,如晶振负载电容、输出分频比和相位调整等,需要进行精确计算和调试,以满足系统的具体需求。希望各位工程师在使用CDCE18005时能够充分发挥其优势,设计出更加优秀的电子系统。

大家在使用CDCE18005的过程中遇到过哪些有趣的问题或者有什么独特的应用经验呢?欢迎在评论区分享交流!

-

时钟缓冲器

+关注

关注

2文章

273浏览量

51954 -

可编程

+关注

关注

2文章

1332浏览量

41540

发布评论请先 登录

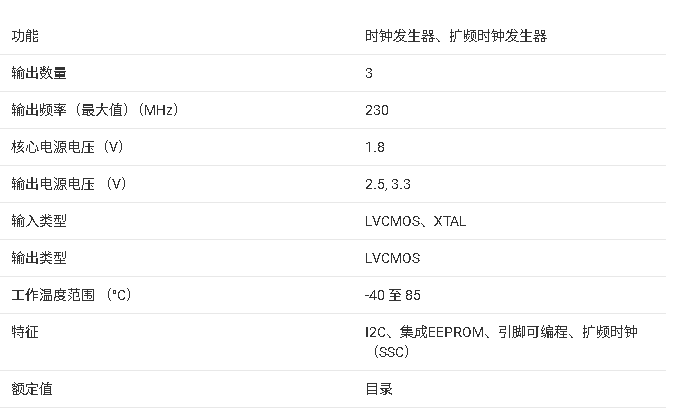

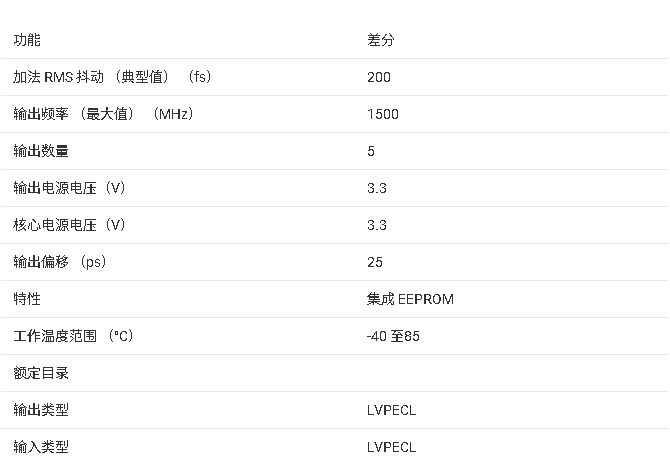

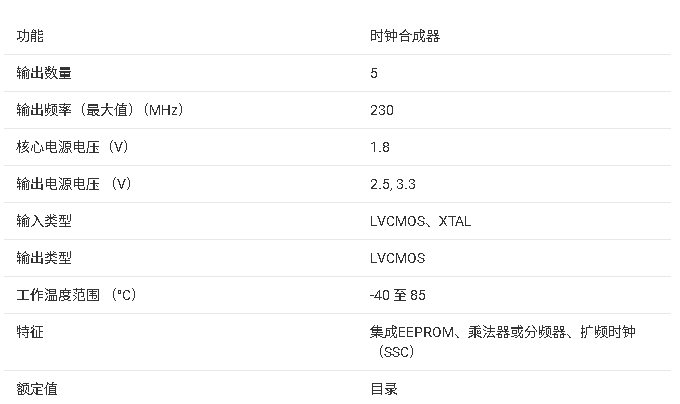

CDCE913 可编程1PLL VCXO时钟合成器技术手册

CDCE18005:高性能可编程时钟缓冲器的深度剖析

CDCE18005:高性能可编程时钟缓冲器的深度剖析

评论