深入解析LMK1C110x系列LVCMOS时钟缓冲器

在电子设计的领域中,时钟缓冲器扮演着至关重要的角色,它能够确保时钟信号的稳定传输和分配。今天,我们就来深入探讨德州仪器(Texas Instruments)推出的LMK1C110x系列1.8 - V、2.5 - V和3.3 - V LVCMOS时钟缓冲器。

文件下载:lmk1c1102.pdf

一、产品特性亮点

高性能与低抖动

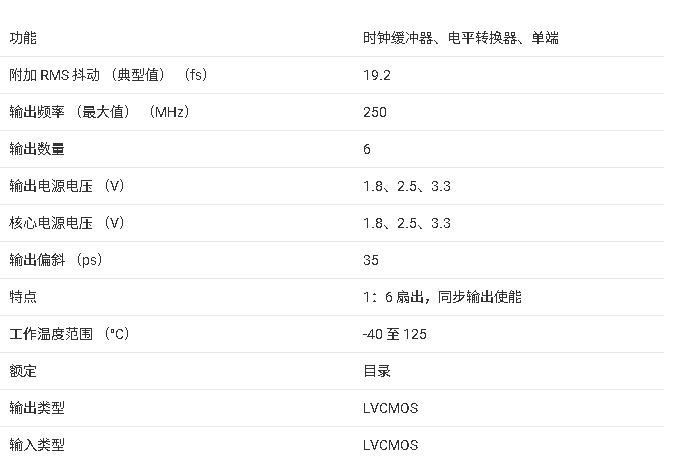

LMK1C110x系列提供了1:2、1:3或1:4的LVCMOS时钟缓冲功能。其输出偏斜极低,小于50 ps,能够有效保证多个输出时钟信号之间的同步性。同时,它的附加抖动也极低,最大小于50 fs。在不同电源电压下,典型附加抖动表现出色:3.3 V时为7.5 fs,2.5 V时为10 fs,1.8 V时为19.2 fs。这种低抖动特性对于对时钟信号质量要求较高的应用来说至关重要。

低延迟与同步控制

该系列的传播延迟小于3 ns,能够快速响应输入时钟信号。此外,它支持同步输出使能控制(1G),当1G为低电平时,输出会切换到低状态,方便用户对输出进行灵活控制。

宽电压范围与高兼容性

LMK1C110x支持3.3 V、2.5 V或1.8 V的电源电压,并且在所有电源电压下输入都能耐受3.3 V。它还具备故障安全输入功能,即使在没有输入信号的情况下也能防止输出振荡,并且允许在VDD供电之前提供输入信号。所有器件引脚相互兼容,并且与CDCLVC110x系列向后兼容,方便工程师进行设计和升级。

温度与封装优势

其工作温度范围为 -40°C至125°C,能够适应各种恶劣的工作环境。同时,该系列提供8引脚TSSOP和8引脚WSON封装,用户可以根据实际需求进行选择。

二、应用领域广泛

LMK1C110x系列时钟缓冲器凭借其高性能和稳定性,在多个领域得到了广泛应用:

- 工厂自动化与控制:确保工业设备中时钟信号的稳定传输,提高设备的运行精度和可靠性。

- 电信设备:为通信系统提供高质量的时钟信号,保障信号的准确传输和处理。

- 数据中心与企业计算:满足高速数据处理和传输对时钟信号的严格要求。

- 电网基础设施:在电力系统中保证时钟同步,提高电网的稳定性和可靠性。

- 电机驱动:为电机控制系统提供精确的时钟信号,实现电机的精准控制。

- 医疗成像:保证医疗设备中图像采集和处理的准确性和实时性。

三、详细参数解析

电气特性

不同电源电压下,该系列时钟缓冲器的电气特性有所不同。例如,在VDD = 3.3 V时,输入频率最大值为250 MHz;而在VDD = 2.5 V和1.8 V时,输入频率最大值为200 MHz。输出频率也遵循相同的规律。其输出占空比在输入为50%占空比时,能保持在45% - 55%之间,保证了时钟信号的质量。

绝对最大额定值与ESD防护

为了保证器件的正常工作和寿命,需要注意其绝对最大额定值。例如,电源电压范围为 -0.5 V至一定值,输入电流范围为 -20 mA至20 mA等。同时,该系列器件具备良好的静电放电(ESD)防护能力,人体模型(HBM)可达±9000 V,带电设备模型(CDM)可达±1500 V,有效保护器件免受静电损害。

热性能参数

热性能也是电子设计中需要考虑的重要因素。LMK1C110x系列给出了不同封装下的热性能参数,如结到环境的热阻、结到外壳(顶部)的热阻等。通过这些参数,工程师可以合理设计散热方案,确保器件在正常温度范围内工作。

四、应用设计实例

设计要求

在一个系统配置示例中,我们将LMK1C110x配置为从本地LVCMOS振荡器扇出100 - MHz信号。CPU通过1G控制输出状态,为三个LVCMOS接收器提供时钟信号。其中,CPU时钟可接受全摆幅直流耦合LVCMOS信号,通过在LMK1C110x附近放置串联电阻来匹配走线特性阻抗,减少反射;FPGA时钟采用类似的直流耦合方式,并在附近放置合适的串联电阻;PLL可接受较低幅度的信号,采用了戴维宁等效端接,并且当共模电压不匹配时可使用交流耦合。

设计步骤

在设计过程中,未使用的输出可以浮空,以降低系统成本。同时,要根据电源供应建议采用合适的滤波技术,选择合适的滤波电容和旁路电容,并将其靠近电源端子放置,确保短回路布局以减小电感。还可以考虑在板级电源和芯片电源之间插入铁氧体磁珠,隔离高频开关噪声。

性能表现

从应用曲线可以看出,LMK1C110x具有极低的附加抖动。例如,在3.3 V电源下,一个低噪声156.25 - MHz参考源(25.6 - fs RMS抖动)驱动该器件,积分范围从12 kHz到20 MHz时,输出抖动为26.7 - fs RMS,测量得到的附加抖动仅为7.6 - fs RMS。在不同电源电压下都有类似的低抖动表现,充分证明了其高性能。

五、布局与电源建议

布局指南

在PCB布局方面,要注意电源旁路电容的放置。对于元件侧安装,建议使用0402尺寸的电容,方便信号布线。要尽量缩短旁路电容与器件电源之间的连接,将电容的另一侧通过低阻抗连接到接地平面。对于WSON封装的器件,要特别注意其无引脚的特点进行布局设计。

电源建议

高性能时钟缓冲器对电源噪声比较敏感,因此需要对电源进行有效的管理。使用滤波电容消除低频噪声,旁路电容为高频噪声提供低阻抗路径,并且要选择低等效串联电阻(ESR)的旁路电容。同时,建议在板级电源和芯片电源之间插入铁氧体磁珠,隔离高频开关噪声,但要注意选择直流电阻低的磁珠,以保证器件正常工作所需的电压。

六、总结

LMK1C110x系列LVCMOS时钟缓冲器以其高性能、低抖动、宽电压范围和良好的兼容性,在众多应用领域展现出了强大的优势。电子工程师在设计过程中,要充分了解其特性和参数,根据实际需求进行合理的应用设计和布局布线,以发挥其最大性能。同时,要注意遵循相关的电源和ESD防护建议,确保器件的可靠性和稳定性。大家在实际应用中是否遇到过类似时钟缓冲器的设计挑战呢?欢迎在评论区分享你的经验和见解。

-

低抖动

+关注

关注

0文章

76浏览量

6124

发布评论请先 登录

LMK1C110x 1.8V、2.5V和3.3V LVCMOS时钟缓冲器系列数据表

LMK1C1108低附加相位噪声LVCMOS时钟缓冲器评估板

LMK1C1104DQF低加法、相位噪声LVCMOS时钟缓冲器评估板

LMK1C1106 6通道输出LVCMOS 1.8V缓冲器技术手册

深入解析LMK1C110x系列LVCMOS时钟缓冲器

深入解析LMK1C110x系列LVCMOS时钟缓冲器

评论