探索LMKDB11xx:PCIe时钟缓冲器的卓越之选

在当今高速发展的电子领域,PCIe技术的应用日益广泛,对于时钟缓冲器的性能要求也越来越高。TI推出的LMKDB11xx系列PCIe Gen 1至Gen 7超低抖动LP - HCSL时钟缓冲器,以其卓越的性能和丰富的特性,为工程师们提供了理想的解决方案。

文件下载:lmkdb1102.pdf

一、产品概述

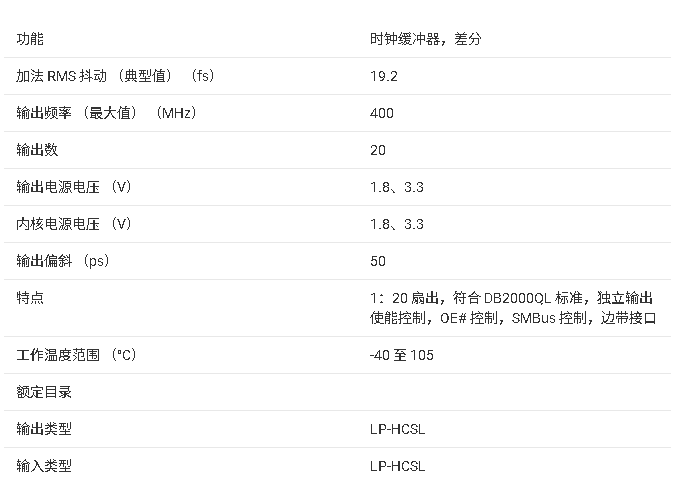

LMKDB11xx系列包括LMKDB1102、LMKDB1104、LMKDB1104FS、LMKDB1108、LMKDB1108FS、LMKDB1112、LMKDB1120和LMKDB1120FS等型号。这些设备是DB2000QL兼容的时钟缓冲器,专为PCIe Gen 1到Gen 7应用设计,具备超低附加抖动和超低传播延迟的特点,能为整个时钟路径提供足够的抖动余量,尤其适用于PCIe Gen 5、Gen 6和Gen 7的缓冲级联以及以太网扇出应用。同时,该系列支持1.8V和3.3V两种电源电压,提供了更高的设计灵活性。

二、产品特性亮点

(一)超低附加抖动

在高速数据传输中,抖动是影响信号质量的关键因素。LMKDB11xx系列在这方面表现出色,以156.25MHz为例,其最大12kHz至20MHz RMS附加抖动仅为31fs。对于不同的PCIe世代,附加抖动也极低,如PCIe Gen 4最大附加抖动为13fs,Gen 5为5fs,Gen 6为3fs,Gen 7为2.1fs。如此低的附加抖动,能有效保证信号的稳定性和准确性,减少数据传输中的错误。

(二)灵活的输入输出特性

- 输入特性

- 输出特性

- 可编程输出摆率:通过SMBus和引脚模式提供摆率控制选项。引脚模式可实现全局摆率控制,而SMBus则支持为每个输出单独编程摆率。摆率设置经过PCIe测试负载验证,能根据实际需求灵活调整信号的上升和下降时间。

- 可编程输出幅度摆幅:支持在600mV至975mV范围内可编程的LP - HCSL摆幅,所有输出可通过寄存器AMP和AMP_BANKX编程为相同的输出摆幅。

- 精确的输出阻抗:支持100Ω或85Ω的LP - HCSL输出阻抗,且输出阻抗精确调整至±5%,有助于提高阻抗匹配和时钟信号完整性。

- 故障安全输出:带有“FS”后缀的型号(如LMKDB1120FS、LMKDB1108FS和LMKDB1104FS)具有故障安全输出功能,当设备电源关闭时,输出可驱动到VDD,而不会产生泄漏或可靠性问题。

(三)灵活的电源序列

- PWRDN#断言和取消断言:在推荐的电源关闭序列中,PWRDN#在输入时钟有效时断言,并保持低电平两个连续的输入时钟周期上升沿,可确保所有时钟输出无毛刺地静音到低/低状态。

- OE#断言和取消断言:OE#引脚可在任何时候断言和取消断言,但只有在时钟输入有效、PWRGD/PWRDN#引脚为高电平且设备电源开启的条件下才会生效。当这些条件满足时,输出可无毛刺地启用或禁用。

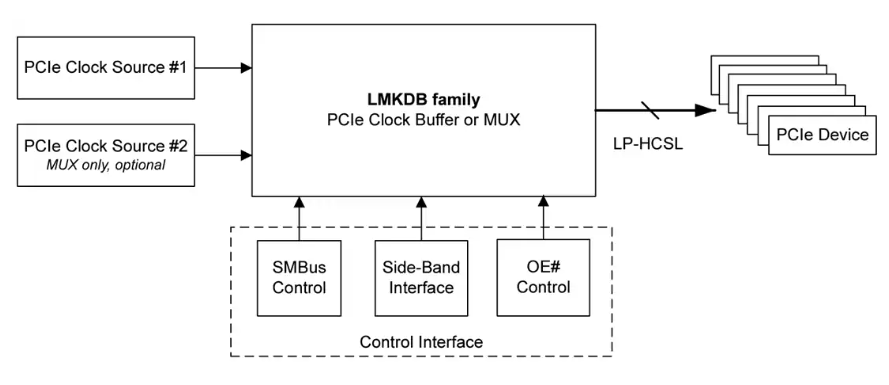

(四)多种控制模式

设备具有引脚模式、SMBus模式和边带接口(SBI)模式,且三种模式可同时使用。SBI模式能以高达25MHz的速度启用或禁用输出时钟,比SMBus更快。而SMBus则可在设备上电后接管设备控制并读取状态。

三、应用实例

(一)典型应用场景

以PCIe和以太网时钟分配为例,该系列设备可根据给定的源提供多个PCIe时钟(100MHz)或以太网时钟(156.25MHz)的副本。在设计中,需根据具体需求选择合适的缓冲器,如为满足PCIe时钟扇出和以太网时钟扇出的要求,可分别选择LMKDB1120和LMKDB1108。

(二)设计步骤

- 计算抖动预算:使用RMS加法计算时钟缓冲器的抖动预算,通过参考时钟抖动和总时钟抖动的平方差的平方根来确定时钟缓冲器允许的最大附加抖动。

- 选择合适的缓冲器:根据计算结果和设备的抖动规格,选择满足要求的缓冲器。如在PCIe Gen 5时钟分配中,LMKDB1120的附加抖动远低于允许值;在以太网时钟分配中,LMKDB1108也能满足抖动要求。

四、设计建议

(一)电源供应

为减少电源噪声,建议在每个电源引脚附近放置0.1μF的电容器。对于VDDA、VDD_IN0和VDD_IN1引脚,可放置2.2Ω的电阻。整个芯片可使用铁氧体磁珠和10µF的电容器接地。对于MUX设备,若两个输入使用不同频率,需通过添加更多铁氧体磁珠来隔离输入和相应的输出组。

(二)布局设计

- 接地连接:使用低电感的接地连接,确保设备DAP与PCB之间的良好接地。

- 阻抗匹配:匹配PCB走线阻抗与设备输出阻抗(85Ω或100Ω差分阻抗),消除走线中的短截线,减少传输线上的不连续性。

五、总结

LMKDB11xx系列PCIe时钟缓冲器凭借其超低附加抖动、灵活的输入输出特性、灵活的电源序列以及多种控制模式等优势,为PCIe和以太网时钟分配等应用提供了可靠的解决方案。在实际设计中,工程师们需根据具体需求,合理选择设备,并遵循电源供应和布局设计的建议,以充分发挥该系列设备的性能优势。你在使用这类时钟缓冲器时遇到过哪些挑战呢?欢迎在评论区分享你的经验和想法。

-

PCIe时钟缓冲器

+关注

关注

0文章

20浏览量

6748

发布评论请先 登录

LMKDB1120和LMKDB1108超低抖动PCIe第1代到第6代LP-HCSL时钟缓冲器数据表

LMKDB11xx系列PCIe时钟缓冲器技术文档总结

探索LMKDB11xx:PCIe时钟缓冲器的卓越之选

探索LMKDB11xx:PCIe时钟缓冲器的卓越之选

评论