CDCLVC11xx系列LVCMOS时钟缓冲器:高性能设计的理想之选

在电子设计领域,时钟缓冲器是保障信号稳定传输和系统精确运行的关键组件。德州仪器(TI)的CDCLVC11xx系列LVCMOS时钟缓冲器以其卓越的性能和灵活的配置,在通用通信、工业和消费应用等领域展现出强大的竞争力。今天,我们就来深入探讨这个系列的产品。

文件下载:cdclvc1102.pdf

产品特性:高性能与低误差的完美结合

多扇出比与高兼容性

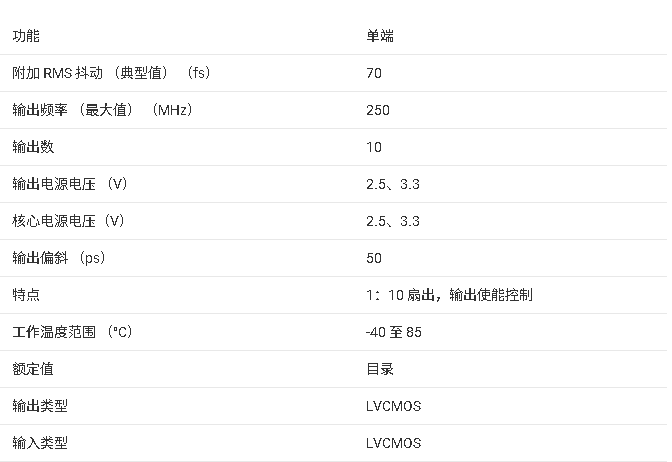

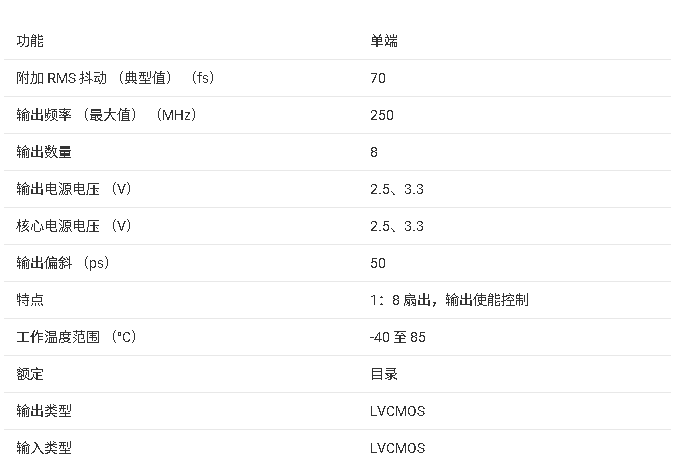

CDCLVC11xx系列提供了从1:2到1:12的七种不同扇出比选择,能满足多样化的设计需求。而且,所有器件引脚兼容,这使得在设计过程中更换不同扇出比的器件变得轻松自如,大大提高了设计的灵活性和可维护性。

超低偏差与抖动

在信号传输中,偏差和抖动是影响信号质量的重要因素。CDCLVC11xx系列表现出色,引脚间偏差(Skew)小于50 ps,附加抖动(Jitter)小于100 fs(3.3V供电,250 MHz时)。如此低的偏差和抖动,确保了信号的精确同步和稳定传输,为系统的高性能运行提供了有力保障。

宽电压与温度范围

该系列支持3.3V和2.5V两种供电电压,最大时钟频率分别可达250 MHz(3.3V)和180 MHz(2.5V)。同时,其工作温度范围为 -40°C至85°C,能适应各种复杂的工作环境,无论是高温的工业现场还是低温的户外设备,都能稳定工作。

异步输出使能控制

CDCLVC11xx系列支持异步输出使能控制(1G),当1G引脚为低电平时,输出将切换到低状态。这一特性使得在应用中可以根据需要灵活地启用或禁用缓冲时钟输出,提高了系统的控制灵活性。

产品规格:全面保障设计安全与性能

绝对最大额定值

在设计过程中,了解器件的绝对最大额定值至关重要。CDCLVC11xx系列的电源电压范围为 -0.5V至4.6V,输入和输出电压范围为 -0.5V至VDD + 0.5V(最大值限制为4.6V)。输入电流和连续输出电流分别限制在 -20 mA至20 mA和 -50 mA至50 mA之间。最大结温为125°C,存储温度范围为 -65°C至150°C。超出这些额定值可能会对器件造成永久性损坏,因此在设计时必须严格遵守。

ESD 评级

静电放电(ESD)是电子器件的潜在威胁。CDCLVC11xx系列具有良好的ESD防护能力,人体模型(HBM)静电放电评级为 ±4000V,带电设备模型(CDM)评级为 ±1500V。这使得器件在生产和使用过程中能更好地抵御静电干扰,提高了产品的可靠性。

推荐工作条件

为了确保器件的最佳性能,推荐的工作条件是电源电压在3.0V至3.6V(3.3V供电)或2.3V至2.7V(2.5V供电)之间。输入电压的低电平(VIL)和高电平(VIH)也有相应的要求,例如在3.0V至3.6V供电时,VIL为VDD / 2 - 600 mV,VIH为VDD / 2 + 600 mV。此外,输入阈值电压(Vth)为VDD / 2 mV,输入转换速率(tr/tf)为1V/ns至4V/ns,最小脉冲宽度(tw)和时钟输入频率(fCLK)也有明确的规定。

热性能与电气特性

热性能方面,不同封装的器件具有不同的热阻,如CDCLVC1102的结到环境热阻(RθJA)为149.4°C/W,结到外壳(顶部)热阻(RθJC(top))为69.4°C/W。电气特性上,静态器件电流(IDD)在不同供电电压下有所不同,例如在3.6V供电时典型值为6 mA,2.7V供电时典型值为3 mA。功率下降电流(IPD)最大为60 µA,输出阻抗(ROUT)在3.3V供电时为45Ω至60Ω。

开关特性

开关特性是衡量时钟缓冲器性能的重要指标。在3.3V ± 0.3V供电时,传播延迟(tPLH, tPHL)为0.8 ns至2.0 ns,输出偏差(tsk(o))小于50 ps,上升和下降时间(tr/tf)为0.3 ns至0.8 ns。在2.5V ± 0.2V供电时,传播延迟为1 ns至2.6 ns,上升和下降时间为0.3 ns至1.2 ns。这些特性确保了信号在传输过程中的快速响应和准确切换。

应用与设计:灵活配置满足多样需求

典型应用场景

以一个背板应用为例,CDCLVC11xx可以将100 MHz的信号从本地LVCMOS振荡器进行扇出,为CPU、FPGA和PLL等设备提供时钟信号。在这个应用中,CPU时钟可以接受全摆幅直流耦合的LVCMOS信号,通过在CDCLVC11xx附近放置串联电阻来匹配走线的特性阻抗,减少反射。FPGA时钟同样采用直流耦合,并在附近放置合适的串联电阻。而PLL可以接受较低幅度的信号,因此使用了戴维南等效终端,并且由于PLL接收器具有内部偏置,在共模电压不匹配时可以使用交流耦合。

详细设计步骤

在设计过程中,首先要根据图5和电气特性表来确定匹配CDCLVC11xx输出阻抗与传输线特性阻抗所需的串联电阻。对于未使用的输出引脚,可以将其悬空,以降低系统的组件成本。同时,要参考电源供应建议部分,采用合适的滤波技术来减少电源噪声对缓冲器的影响。

电源供应与布局:保障稳定运行的关键

电源供应建议

高性能时钟缓冲器对电源噪声非常敏感,电源噪声会显著增加缓冲器的附加抖动。因此,必须采取措施减少系统电源的噪声。可以使用滤波电容来消除电源中的低频噪声,旁路电容则为高频噪声提供低阻抗路径,保护电源系统免受感应波动的影响。旁路电容应选择低等效串联电阻(ESR)的类型,并尽可能靠近电源端子放置,以减少电感。此外,TI建议在板级电源和芯片电源之间插入铁氧体磁珠,以隔离时钟缓冲器产生的高频开关噪声,但要选择直流电阻非常低的磁珠,以确保电源端子的电压满足器件正常工作的要求。

布局指南

在PCB布局方面,要合理放置电源旁路电容。对于元件侧安装,建议使用0402尺寸的电容,方便信号布线。旁路电容与器件电源之间的连接应尽可能短,电容的另一侧应通过低阻抗连接接地平面。参考图14的概念布局,可以更好地实现这一要求。

文档支持与注意事项

相关链接与文档更新通知

TI为CDCLVC11xx系列提供了丰富的技术文档、支持和社区资源、工具和软件等相关链接,方便工程师快速获取所需信息。同时,工程师可以通过在ti.com上的设备产品文件夹中注册“Alert me”,接收文档更新的每周摘要通知,及时了解产品信息的变化。

静电放电注意事项

由于这些器件的内置ESD保护有限,在存储或处理时,应将引脚短接在一起或放置在导电泡沫中,以防止MOS栅极受到静电损坏。

CDCLVC11xx系列LVCMOS时钟缓冲器凭借其高性能、低误差、宽电压和温度范围等优点,为电子工程师提供了一个可靠的设计选择。在实际应用中,我们需要根据具体的设计需求,合理选择器件参数,严格遵循电源供应和布局建议,以确保系统的稳定运行。大家在使用CDCLVC11xx系列产品的过程中,有没有遇到过一些特别的设计挑战呢?欢迎在评论区分享你的经验和想法。

-

电子设计

+关注

关注

42文章

2870浏览量

49916

发布评论请先 登录

CDCLVC11xx 3.3V和2.5V LVCMOS高性能时钟缓冲器系列数据表

CDCLVC11xx系列LVCMOS时钟缓冲器:高性能设计的理想之选

CDCLVC11xx系列LVCMOS时钟缓冲器:高性能设计的理想之选

评论