探索LMKDB12xx:PCIe时钟复用器的卓越之选

在高速数据传输和处理的时代,PCIe技术的发展日新月异,从Gen 1到Gen 7,对时钟信号的质量和稳定性提出了越来越高的要求。今天,我们就来深入探讨一款专为PCIe Gen 1至Gen 7应用设计的超低抖动LP - HCSL时钟复用器——LMKDB12xx系列。

文件下载:lmkdb1204.pdf

1. 产品特性剖析

1.1 广泛的标准支持

LMKDB12xx支持PCIe Gen 1至Gen 7,无论是CC(Common Clock)还是IR(Independent Reference)PCIe架构,它都能完美适配。同时,所有设备均符合DB2000QL规范,为我们的设计提供了坚实的标准基础。

1.2 超低的附加抖动

抖动是衡量时钟信号质量的关键指标之一。LMKDB12xx在这方面表现卓越,在156.25MHz下,12kHz至20MHz RMS附加抖动最大仅为31fs。不同PCIe世代下的附加抖动更是低至令人惊叹的程度:PCIe Gen 4最大为13fs,Gen 5为5fs,Gen 6为3fs,Gen 7为2.1fs。如此低的抖动,为高速数据传输提供了稳定的时钟基础,大大降低了误码率。

1.3 丰富的功能特性

- 故障安全输入:确保在输入信号出现异常时,设备仍能稳定工作,提高了系统的可靠性。

- 灵活的上电顺序:设计人员可以根据实际需求灵活安排上电顺序,增强了设计的灵活性。

- 自动输出禁用:当输入信号无效时,输出时钟会自动静音,避免了无效信号的干扰。

- 独立输出使能:每个输出都可以独立控制,方便实现个性化的时钟分配方案。

- SBI(Side Band Interface)高速输出控制:能够以高达25MHz的速度快速启用或禁用输出时钟,比SMBus更快。

- LOS(Loss of Signal)输入检测:实时监测输入信号的状态,及时反馈信号丢失情况。

- 可选输出阻抗:支持85Ω或100Ω的输出阻抗,可根据实际应用需求进行选择。

- 宽电源电压和温度范围:支持1.8V / 3.3V ± 10%的电源电压,工作环境温度范围为 - 40°C至105°C,适应各种复杂的工作环境。

2. 应用领域拓展

LMKDB12xx凭借其卓越的性能,在多个领域都有广泛的应用:

- 高性能计算:为高性能计算系统提供稳定、低抖动的时钟信号,确保数据处理的高效性。

- 服务器主板:满足服务器对时钟信号质量和稳定性的严格要求,提高服务器的整体性能。

- NIC/SmartNIC:为网络接口卡和智能网卡提供可靠的时钟支持,保障网络通信的顺畅。

- 硬件加速器:在硬件加速领域,为加速器提供精准的时钟信号,提升加速效果。

3. 产品详细解读

3.1 功能框图与工作原理

从功能框图可以看出,LMKDB12xx通过对输入时钟的选择和处理,将合适的时钟信号分配到各个输出端。它具有多种控制模式,包括引脚模式、SMBus模式和SBI模式,这些模式可以同时使用,为设计人员提供了更多的控制选择。例如,通过vSMB_EN引脚可以选择引脚模式或SMBus模式,SBI则可以在更高的速度下实现输出时钟的启用或禁用。

3.2 输入特性分析

- 运行输入时钟:设备支持在电源关闭时输入时钟仍保持运行,这对于时钟输入在电源提供之前就已存在的情况非常有用。

- 故障安全输入:所有时钟输入引脚和数字输入引脚都具备故障安全功能,即使在设备电源关闭时,引脚也能被驱动到VDD,而不会导致泄漏或可靠性问题。

- 输入配置选项:输入缓冲级支持四种不同的配置,包括DC耦合HCSL输入、DC耦合LVDS输入、AC耦合输入和内部50Ω接地端接。对于不同的输入信号类型,我们可以根据实际情况进行选择和配置。例如,对于LP - HCSL输入,通常禁用内部端接;而对于HCSL输入,如果没有外部端接,则可以启用内部端接。

3.3 灵活的电源序列

在电源管理方面,LMKDB12xx有着严格的要求。例如,在推荐的电源关闭序列中,PWRDN#必须在输入时钟有效时被断言,并且要保持低电平两个连续的输入时钟周期上升沿,以确保所有时钟输出静音且无毛刺。OE#引脚的断言和去断言则相对灵活,但只有在时钟输入有效、PWRGD/PWRDN#引脚为高电平且设备电源开启的条件下才会生效。

3.4 LOS和OE控制

- 同步OE:输出的启用和禁用是同步的,确保在输出状态切换时不会出现毛刺或脉冲。

- OE控制方式:支持三种OE控制方式,即OE引脚、通过SMBus的OE寄存器位和通过SBI的OE控制。这三种控制方式遵循与逻辑,只有当所有控制都启用输出时,输出才会被启用。

3.5 输出特性亮点

- 输出银行:LMKDB12xx复用器有两个输出银行,可以作为双银行缓冲模式使用,每个银行都有独立的电源引脚,避免了不同频率下的串扰。

- 双端接支持:虽然在常规PCIe应用中,LP - HCSL输出通常不需要外部端接,但LMKDB系列支持双端接,不过这会增加额外的功耗。

- 可编程输出摆率:通过SMBus和引脚模式可以对输出摆率进行控制。引脚模式提供全局摆率控制,而SMBus则支持对每个输出的可编程摆率控制。摆率的设置与PCB走线特性密切相关,因此在设计时需要充分考虑。

- 可编程输出幅度摆幅:支持在600mV至975mV范围内对LP - HCSL摆幅进行编程,通过寄存器AMP和AMP_BANKX可以对所有输出进行统一编程。

- 精确的输出阻抗:支持100Ω或85Ω的LP - HCSL输出阻抗,并且输出阻抗可以精确调整到±5%,有助于提高阻抗匹配和时钟信号的完整性。

4. 寄存器映射与配置

寄存器映射是理解和配置LMKDB12xx的关键。通过对各个寄存器的操作,我们可以实现对设备功能的精细控制。例如,通过R0和R1寄存器可以控制CLK0 - CLK3的输出启用;通过R4和R36寄存器可以分别启用CLKIN1和CLKIN0的自动输出禁用功能。在实际应用中,我们需要根据具体的设计需求,合理配置这些寄存器的值。

5. 应用设计实例

5.1 典型应用场景

以PCIe和以太网时钟分配为例,LMKDB12xx可以根据给定的时钟源,提供多个PCIe时钟(100MHz)或以太网时钟(156.25MHz)的副本。在设计过程中,我们需要考虑多个因素,如抖动要求、空间限制等。

5.2 设计步骤与计算

首先,我们需要根据设计参数计算时钟缓冲器的抖动预算。例如,对于PCIe Gen 5,根据参考时钟抖动和总时钟抖动的要求,通过RMS加法计算出时钟缓冲器允许的最大附加抖动。然后,根据规格书中的电气特性表,选择满足要求的设备。在这个例子中,PCIe Gen 5允许的最大附加抖动为21fs,而LMKDB12xx在相应条件下的附加抖动远低于这个值,完全满足设计要求。

6. 注意事项与支持资源

6.1 电源供应与布局

在电源供应方面,建议在每个电源引脚附近放置0.1μF的电容,并在VDDA引脚旁边放置2.2Ω的电阻,以减少噪声。所有电源引脚可以连接到一个电源轨上,同时推荐使用铁氧体磁珠和10µF的电容接地。在布局方面,要使用低电感的接地连接,匹配PCB走线阻抗与设备输出阻抗,消除走线中的短截线和不连续性。

6.2 文档与支持

TI提供了丰富的文档和支持资源,包括相关的评估模块用户指南、博客文章等。通过TI E2E™支持论坛,我们可以快速获得专家的帮助和解答。同时,要注意静电放电的防护,避免对集成电路造成损坏。

LMKDB12xx系列时钟复用器以其超低的抖动、丰富的功能和灵活的配置,为PCIe和以太网时钟分配提供了一个优秀的解决方案。在实际设计中,我们需要充分理解其特性和应用要求,合理进行设计和配置,以实现最佳的性能和稳定性。你在使用类似时钟复用器的过程中遇到过哪些挑战呢?欢迎在评论区分享你的经验和想法。

-

低抖动

+关注

关注

0文章

76浏览量

6124

发布评论请先 登录

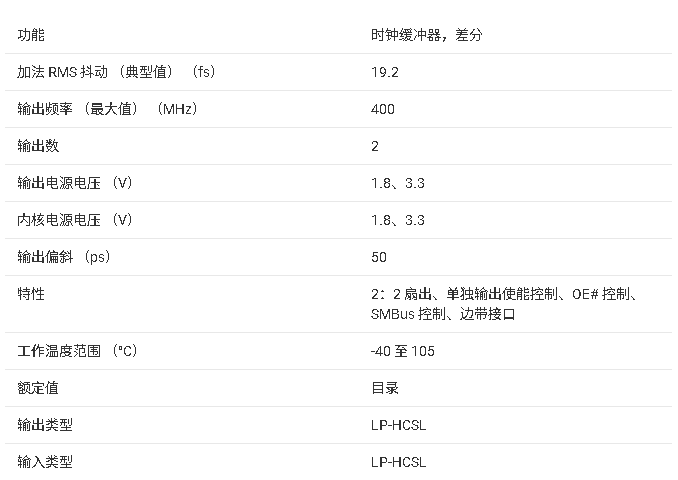

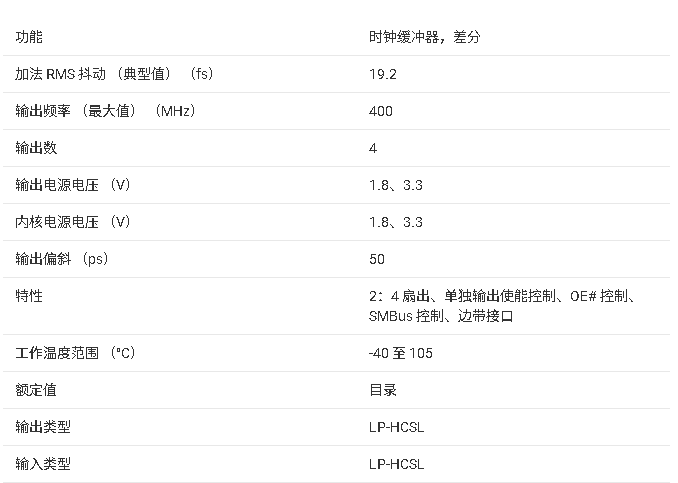

LMKDB1202 PCIe时钟多路复用器技术文档总结

LMKDB1202/LMKDB1204 PCIe时钟多路复用器技术文档总结

探索LMKDB12xx:PCIe时钟复用器的卓越之选

探索LMKDB12xx:PCIe时钟复用器的卓越之选

评论