UCC2154x:隔离式双通道栅极驱动器的卓越之选

在电子设计领域,栅极驱动器是驱动功率晶体管的关键组件,对于提高开关速度、降低开关损耗起着至关重要的作用。德州仪器(TI)推出的 UCC2154x 系列隔离式双通道栅极驱动器,凭借其丰富的特性和出色的性能,成为了众多应用场景中的理想选择。今天,我们就来深入了解一下 UCC2154x 系列栅极驱动器。

文件下载:ucc21542.pdf

一、UCC2154x 简介

UCC2154x 是一系列隔离式双通道栅极驱动器,旨在提供高达 4A/6A 的峰值源/灌电流,可用于驱动功率 MOSFET、IGBT 和 GaN 晶体管。该系列产品具有多种宽体封装选项,如 DW SOIC - 16 和 DWK SOIC - 14,其中 DWK 封装还提供 3.3mm 的最小通道间间距,有助于实现更高的总线电压。

1.1 主要特性

- 宽体封装选择:提供 DW SOIC - 16 和 DWK SOIC - 14 两种封装,满足不同应用需求。

- 高输出电流:高达 4A 峰值源电流和 6A 峰值灌电流,能够为功率晶体管提供强大的驱动能力。

- 宽输出电源电压范围:输出驱动电源 VDD 最高可达 18V,同时提供 5V 和 8V VDD UVLO 选项。

- 高共模瞬态抗扰度(CMTI):CMTI 大于 125V/ns,能够有效抵抗共模干扰,确保在复杂电磁环境下的稳定工作。

- 快速开关参数:典型传播延迟 33ns,最大脉冲宽度失真 6ns,最大 VDD 上电延迟 10µs,能够实现快速而准确的开关控制。

- 可编程死区时间:通过电阻可编程死区时间,可有效防止半桥应用中的直通现象。

- 兼容多种输入:TTL 和 CMOS 兼容输入,方便与各种数字和模拟功率控制器接口。

- 安全认证:计划获得多项安全相关认证,如 DIN EN IEC 60747 - 17(VDE 0884 - 17)的 8000 VPK 加强隔离、UL 1577 的 5700 VRMS 1 分钟隔离以及 GB4943.1 - 2022 的 CQC 认证。

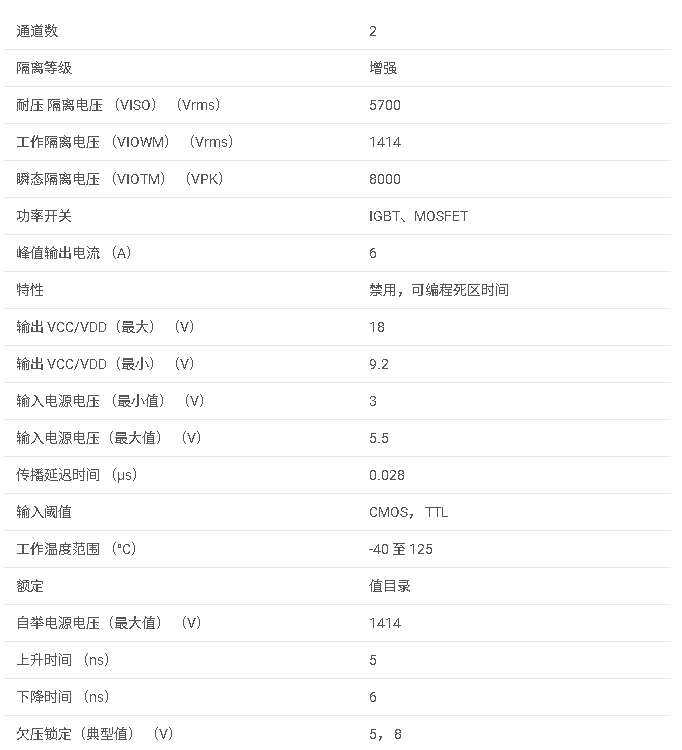

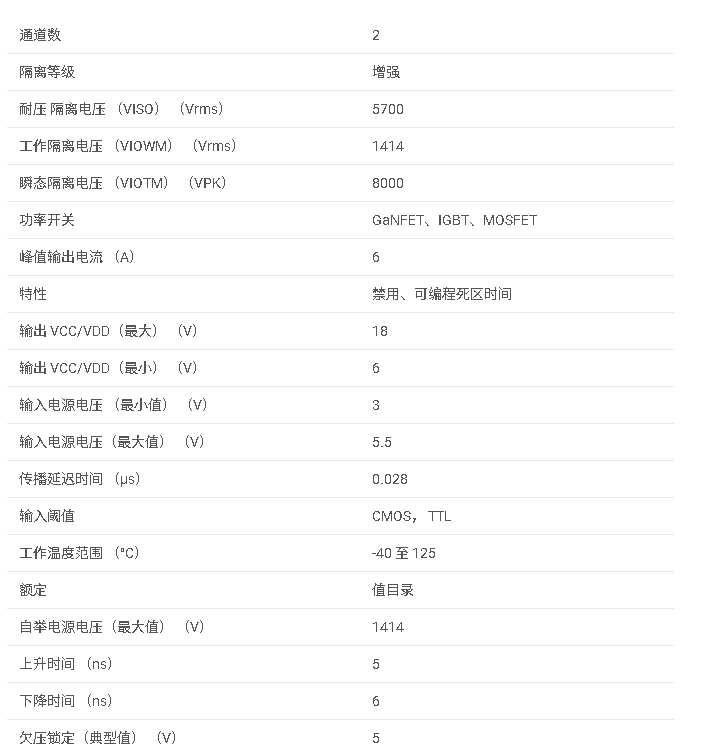

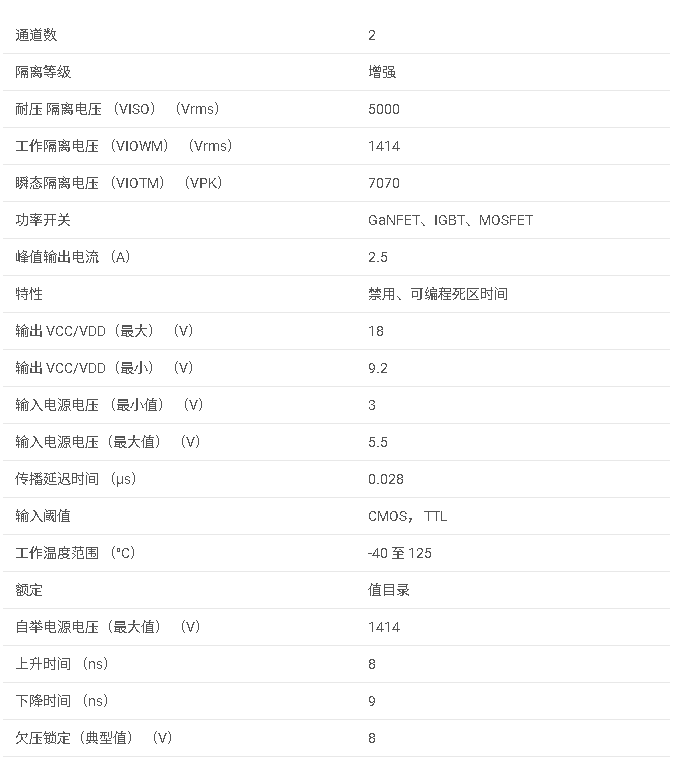

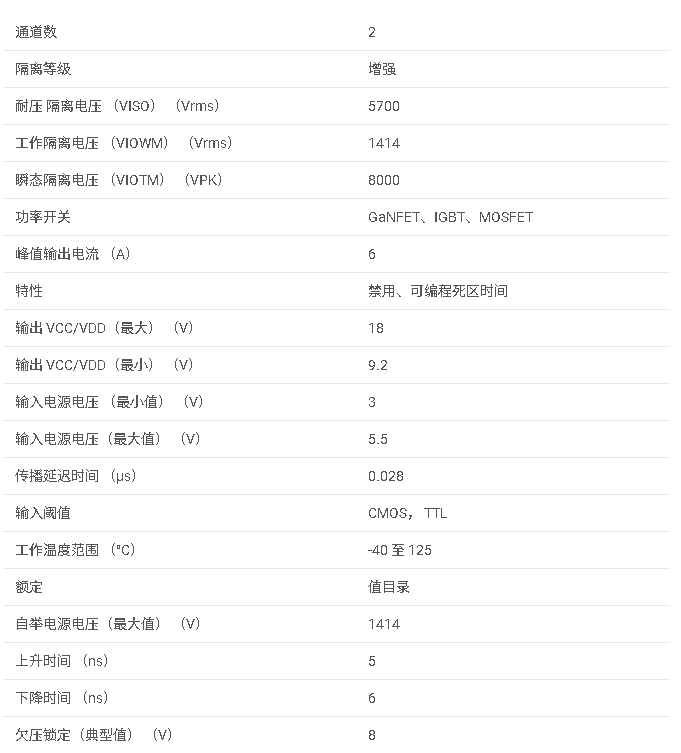

1.2 产品选型

UCC2154x 系列包括 UCC21540、UCC21540A、UCC21541 和 UCC21542 等不同型号,其主要区别在于 UVLO 电压、峰值电流和死区时间功能等方面。具体选型可参考以下表格:

| DEVICE OPTIONS | UVLO | PEAK CURRENT | DEADTIME FUNCTION | PACKAGE |

|---|---|---|---|---|

| UCC21540DW | 8.0 - V | 4 - A Source, 6 - A Sink | Yes | SOIC - 16 |

| UCC21540ADW | 5.0 - V | 4 - A Source, 6 - A Sink | Yes | SOIC - 16 |

| UCC21540DWK | 8.0 - V | 4 - A Source, 6 - A Sink | Yes | SOIC - 14 |

| UCC21540ADWK | 5.0 - V | 4 - A Source, 6 - A Sink | Yes | SOIC - 14 |

| UCC21541DW | 8.0 - V | 1.5 - A Source, 2.5 - A Sink | Yes | SOIC - 16 |

| UCC21542DW | 8.0 - V | 4 - A Source, 6 - A Sink | No | SOIC - 16 |

| UCC21542DWK | 8.0 - V | 4 - A Source, 6 - A Sink | No | SOIC - 14 |

| UCC21542ADWK | 5.0 - V | 4 - A Source, 6 - A Sink | No | SOIC - 14 |

二、UCC2154x 的详细特性

2.1 欠压锁定(UVLO)保护

UCC2154x 在 VDD 和 VCCI 电源上均具有内部欠压锁定(UVLO)保护功能。当 VDD 偏置电压低于启动时的 VVDD_ON 或启动后的 VVDD_OFF 时,VDD UVLO 功能会将通道输出拉低,无论输入引脚状态如何。同样,当 VCCI 电源电压在启动时低于 VCCI_ON 或启动后低于 VCCI_OFF 时,输入无法影响输出,输出将被拉低。UVLO 保护还具有迟滞特性,可防止因电源地噪声引起的抖动,确保设备在电源电压波动时的稳定工作。

2.2 输入和输出逻辑

UCC2154x 的输入引脚(INA、INB 和 DIS)基于 TTL 和 CMOS 兼容的输入阈值逻辑,与输出通道的 VDD 电源电压完全隔离。输入引脚易于由逻辑电平控制信号驱动,具有典型的高阈值(VINAH)为 1.8V 和低阈值为 1V,且受温度影响较小。宽滞后(VINA_HYS)为 0.8V,提供了良好的抗噪声能力和稳定的操作。如果任何输入引脚悬空,内部下拉电阻会将其拉低。

输出级采用独特的上拉和下拉结构。上拉结构由一个 P 沟道 MOSFET 和一个额外的 N 沟道 MOSFET 并联组成,在功率开关开启过渡的米勒平台区域,能够提供更高的峰值源电流,实现快速开启。下拉结构由一个 N 沟道 MOSFET 组成,输出电压在 VDD 和 VSS 之间摆动,实现轨到轨操作。

2.3 可编程死区时间

UCC21540/A 和 UCC21541 允许用户通过两种方式调整死区时间:

- DT 引脚连接到 VCCI:输出完全匹配输入,不强制设置最小死区时间,允许输出重叠。为提高抗噪声能力,建议将该引脚直接连接到 VCCI。

- 在 DT 引脚和 GND 之间连接编程电阻:通过在 DT 引脚和 GND 之间放置电阻 RDT 来编程死区时间 tDT,计算公式为 tDT ≈ 10 × RDT (tDT 单位为纳秒,RDT 单位为千欧)。为提高抗噪声能力,建议在 DT 引脚附近并联一个 ≤1nF 的陶瓷电容器。

可编程死区时间功能可有效防止半桥应用中的直通现象,确保系统的安全可靠运行。

2.4 禁用引脚功能

当 DIS 引脚置高时,两个输出将同时关闭;当 DIS 引脚置低时,UCC2154x 正常运行。在与远距离微控制器连接时,建议在 DIS 引脚附近使用一个 ≈1 - nF 的低 ESR/ESL 电容器进行旁路。为提高抗噪声能力,若不使用 DIS 引脚,建议将其连接到 GND。

三、应用与设计

3.1 应用场景

UCC2154x 具有灵活的通用性,可作为 MOSFET、IGBT 或 GaN 晶体管的低侧、高侧、高侧/低侧或半桥驱动器,适用于多种应用场景,包括隔离式 AC - DC 和 DC - DC 电源、服务器、电信、IT 和工业基础设施、电机驱动和太阳能逆变器以及工业运输等领域。

3.2 典型应用设计

以 UCC2154x 驱动 650 - V MOSFETs 的高低侧配置为例,下面介绍详细的设计步骤:

3.2.1 设计 INA/INB 输入滤波器

为滤除不理想布局或长 PCB 走线引入的振铃,可使用一个小的输入 RIN - CIN 滤波器。建议 RIN 在 0 Ω 到 100 Ω 之间,CIN 在 10 pF 到 100 pF 之间。例如,选择 RIN = 51 Ω 和 CIN = 33 pF,截止频率约为 100 MHz。在选择这些组件时,需注意良好的抗噪声能力和传播延迟之间的权衡。

3.2.2 选择死区时间电阻和电容器

根据死区时间计算公式 tDT ≈ 10 × RDT,选择 20 - kΩ 的电阻将死区时间设置为 200 ns。在 DT 引脚附近并联一个 ≤1nF 的电容器,以提高抗噪声能力。

3.2.3 选择外部自举二极管及其串联电阻

自举电容器在低侧晶体管导通时,通过外部自举二极管由 VDD 充电。为减少反向恢复损耗和相关接地噪声反弹,建议选择高压、快速恢复二极管或具有低正向压降和低结电容的 SiC 肖特基二极管。例如,在 DC - 链路电压为 400 VDC 的情况下,选择 600 - V 超快二极管 MURA160T3G。

同时,使用自举电阻 RBOOT 来限制 DBOOT 中的浪涌电流,并限制每个开关周期内 VDDA - VSSA 电压的上升斜率。建议 RBOOT 的值在 1 Ω 到 20 Ω 之间,例如选择 2.7 Ω 的限流电阻,可将自举二极管的估计最坏情况峰值电流限制在约 4 A。

3.2.4 栅极驱动器输出电阻

外部栅极驱动器电阻 RON / ROFF 用于限制寄生电感/电容引起的振铃、高压/电流开关 dv/dt、di/dt 和体二极管反向恢复引起的振铃、微调栅极驱动强度以优化开关损耗以及减少电磁干扰(EMI)。

根据相关公式可计算出高侧和低侧的峰值源电流和峰值灌电流。同时,需注意 PCB 布局和负载电容会影响估计的峰值电流,建议尽量减小栅极驱动器回路的长度。为减少过度的栅极振铃,可在 FET 栅极附近使用铁氧体磁珠,必要时添加外部钳位二极管。

3.2.5 栅极到源极电阻选择

建议在栅极驱动器输出未供电且处于不确定状态时,使用栅极到源极电阻 RGS 将栅极电压下拉至源极电压。该电阻还可帮助减轻在栅极驱动器能够开启并主动拉低之前,由于米勒电流引起的 dv/dt 诱导导通风险。RGS 的阻值通常在 5.1kΩ 到 20kΩ 之间,具体取决于功率器件的 Vth 和 CGD 与 CGS 的比值。

3.2.6 估算栅极驱动器功耗

栅极驱动器子系统的总损耗 PG 包括 UCC2154x 的功率损耗 PGD 和外围电路的功率损耗。PGD 可通过计算静态功率损耗 PGDQ 和开关操作损耗 PGDO 来估算。

静态功率损耗 PGDQ 包括驱动器的静态功耗以及在一定开关频率下的自功耗,可通过测量给定 VCCI、VDD、开关频率和环境温度下,OUTA 和 OUTB 无负载时的电流来计算。

开关操作损耗 PGDO 取决于负载电容,在每个开关周期内驱动器对负载进行充电和放电。根据不同的情况,PGDO 有不同的计算方法,具体可参考文档中的公式。

3.2.7 估算结温

UCC2154x 的结温 TJ 可通过公式 TJ = TC + ΨJT × PGD 估算,其中 TC 是通过热电偶或其他仪器测量的 UCC2154x 外壳顶部温度,ΨJT 是结到顶部的特征参数。使用 ΨJT 而不是结到外壳的热阻 RΘJC 可以大大提高结温估算的准确性。

3.2.8 选择 VCCI、VDDA/B 电容器

- VCCI 电容器:连接到 VCCI 的旁路电容器支持初级逻辑所需的瞬态电流和总电流消耗,建议使用电压额定值足够、温度系数和电容公差合适的低 ESR 和低 ESL 表面贴装多层陶瓷电容器(MLCC),如 25 - V、电容大于 100 nF 的 MLCC。如果偏置电源输出与 VCCI 引脚距离较远,应并联一个电容大于 1 µF 的钽或电解电容器。

- VDDA (自举)电容器:VDD 电容器(自举电容器)需要提供高达 4 - A 的源峰值电流,并为功率晶体管保持稳定的栅极驱动电压。根据总电荷需求和电压纹波要求,可计算出所需的最小电容值。例如,在给定条件下,计算出最小 CBOOT 要求为 230 nF,但实际应用中应考虑一定的裕量,选择 50 - V、1 - µF 的电容器,并将其放置在尽可能靠近 VDD 和 VSS 引脚的位置。为进一步降低宽频率范围内的交流阻抗,可在 VDDx - VSSx 引脚附近并联一个 100 nF 的 X7R 陶瓷电容器。

- VDDB 电容器:通道 B 的电流要求与通道 A 相同,因此需要一个 VDDB 电容器。在自举配置中,该电容器还需通过自举二极管为 VDDA 提供电流。例如,可选择 50 - V、10 - µF 的 MLCC 和 50 - V、220 - nF 的 MLCC。如果偏置电源输出与 VDDB 引脚距离较远,应并联一个电容大于 10 µF 的钽或电解电容器。

3.3 输出级负偏置应用电路

当非理想 PCB 布局和长封装引脚引入寄生电感时,功率晶体管的栅极 - 源极驱动电压在高 di/dt 和 dv/dt 开关期间可能会出现振铃。为避免振铃超过阈值电压导致意外导通甚至直通,可在栅极驱动上施加负偏置。文档中介绍了三种实现负栅极驱动偏置的示例电路:

- 使用齐纳二极管的隔离电源输出级负偏置:通过在隔离电源输出级使用齐纳二极管设置负偏置,该配置需要两个电源,且存在来自 Rz 的稳态功耗。

- 使用两个电源的负偏置:该解决方案使用两个电源(或单输入双输出电源),可更灵活地设置正负轨电压,但需要更多的电源。

- 使用单个电源和齐纳二极管的负偏置:该方案仅使用一个电源,自举电源可用于高侧驱动,成本和设计工作量较低。但负栅极驱动偏置不仅取决于齐纳二极管,还与占空比有关,且高侧 VDDA - VSSA 必须保持足够的电压以维持在推荐的电源范围内,因此不适用于高侧 100% 占空比的情况。

四、布局指南

为了实现 UCC2154x 的最佳性能,在 PCB 布局时需要考虑以下几个方面:

4.1 组件放置

- 在 VCCI 和 GND 引脚之间以及 VDD 和 VSS 引脚之间连接低 ESR 和低 ESL 电容器,以支持外部功率晶体管开启时的高峰值电流。

- 在桥接配置中,尽量减小顶部晶体管源极和底部晶体管源极之间的寄生电感,以避免开关节点 VSSA(HS)引脚上出现大的负瞬变。

- 如果从远距离微控制器或高阻抗源驱动 DIS 引脚,建议在 DIS 引脚和 GND 之间添加一个 ≥1000 pF 的小旁路电容器,以提高抗噪声能力。

- 如果使用死区时间功能,建议将编程电阻 RDT 和旁路电容器放置在靠近 UCC2154x 的 DT 引脚处,以防止噪声意外耦合到内部死区时间电路,电容器应 ≤1 nF。

4.2 接地考虑

- 确保对晶体管栅极进行充电和放电的高峰值电流限制在最小的物理回路面积内,以降低回路电感并最小化晶体管栅极端子上的噪声。栅极驱动器应尽可能靠近晶体管放置。

- 注意包括自举电容器、自举二极管、局部 VSSB 参考旁路电容器和低侧晶体管体/反并联二极管的高电流路径。自举电容器通过自举二极管由 VDD 旁路电容器逐周期充电,充电过程涉及高峰值电流,因此在电路板上最小化该回路的长度和面积对于确保可靠运行至关重要。

4.3 高压考虑

- 为确保初级和次级侧之间的隔离性能,避免在驱动器设备下方放置任何 PCB 走线或铜箔,建议使用 PCB 切口以防止可能影响隔离性能的污染。

- 对于半桥或高低侧配置,最大化高低侧 PCB 走线之间的 PCB 布局间隙距离。DWK 封装移除了引脚 12 和 13,具有最小 3.3mm 的爬电距离,允许更高的总线电压。

4.4 热考虑

如果驱动电压高、负载重或开关频率高,UCC2154x 可能会消耗大量功率。合理的 PCB 布局有助于将热量从设备散发到 PCB,并最小化结到电路板的热阻抗(θJB)。建议增加连接到 VDDA、VDDB、VSSA 和 VSSB 引脚的 PCB 铜箔面积,优先考虑最大化与 VSSA 和 VSSB 的连接。如果系统中有多层,则

-

应用设计

+关注

关注

0文章

371浏览量

8663

发布评论请先 登录

UCC2154x:隔离式双通道栅极驱动器的卓越之选

UCC2154x:隔离式双通道栅极驱动器的卓越之选

评论