作为半导体器件的潜在致命隐患,Latch Up(闩锁效应)一直是电子行业可靠性测试的重点。今天,SGS带你深入揭秘这个“隐形杀手”,并详解国际权威标准JEDEC JESD78F.02如何通过科学的测试方法,为芯片安全筑起坚固防线。

闩锁效应(Latch Up):芯片内部的“雪崩”

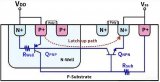

Latch Up是指集成电路在异常电压或电流触发下,内部寄生结构(如晶闸管PNPN、双极晶体管BJT或ESD保护元件)被激活,形成持续低阻抗路径,导致异常大电流(可达数百毫安)从电源流向地。即使触发条件移除,电流仍持续,直至器件过热或物理损坏。

典型触发场景:

●信号引脚注入过流/过压(如静电放电、电源浪涌);

●电源引脚电压瞬变超过器件耐受极限;

●高温环境下寄生结构阈值降低(如结温接近最大工作温度Tjmax)。

危害有多严重?

●物理损坏:硅片熔融、金属互连熔断、封装材料热损伤(EIPD,电诱导物理损坏);

●系统级故障:引发设备死机、数据丢失,甚至引发汽车电子、医疗设备等关键领域的安全事故;

●可靠性风险:导致 “无故障发现(NTF)” 问题,增加售后维修成本和品牌声誉损失。

破解之道——

JEDEC JESD78F.02标准的两大核心测试

为了有效评估芯片抗Latch Up的能力,JEDEC制定了全球通用的测试标准JESD78F.02。该标准定义了两种核心测试方法,覆盖芯片所有引脚类型,模拟真实应用中的极端应力场景。

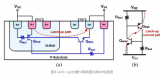

目标:验证信号引脚(输入/输出/双向引脚)对过流 / 过压的免疫能力。

●I-Test(电流注入法):

强制注入正/负电流脉冲 (如±100mA),同时限制电压在1.5×VmaxOP和MSV(最大应力电压)中的较小值以下,避免非闩锁损伤。

●E-Test(电压注入法):

施加正/负电压脉冲 (如1.5×VmaxOP),限制电流在预设阈值(如100mA),适用于高阻抗输入或低电压器件。

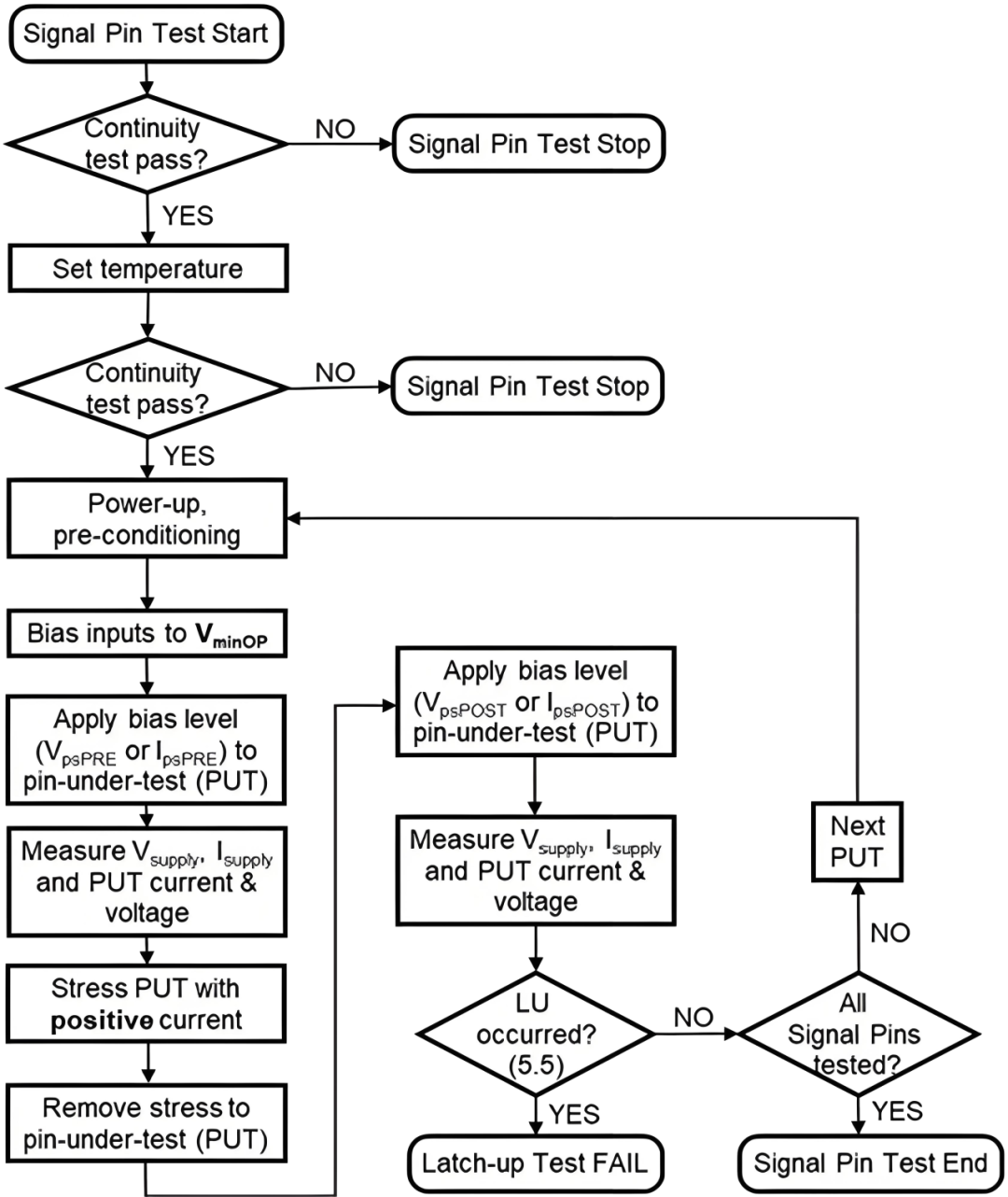

测试流程:

1.引脚分组(输入/输出),预处理至逻辑高/低状态(VmaxOP/VminOP);

2.施加脉冲;

3.监测电源电流,达到以下条件则判定闩锁触发:

a.测试后电流值超出测试前电流值10mA;

b.测试后电流值超过测试前电流值的1.4倍。

信号引脚测试流程图

02电源引脚测试(Supply Test)

目标:评估电源引脚对过电压的耐受能力。

●方法:

对电源引脚施加1.5×VmaxSUP或MSV的电压脉冲(哪个更低),同时限流设置为Ilimit=100mA+Inom(Inom为标称电流)或1.5倍Inom(哪个更高)。

●关键参数:

避免电源因过流崩溃,需设置合理电流限制,确保测试有效性。

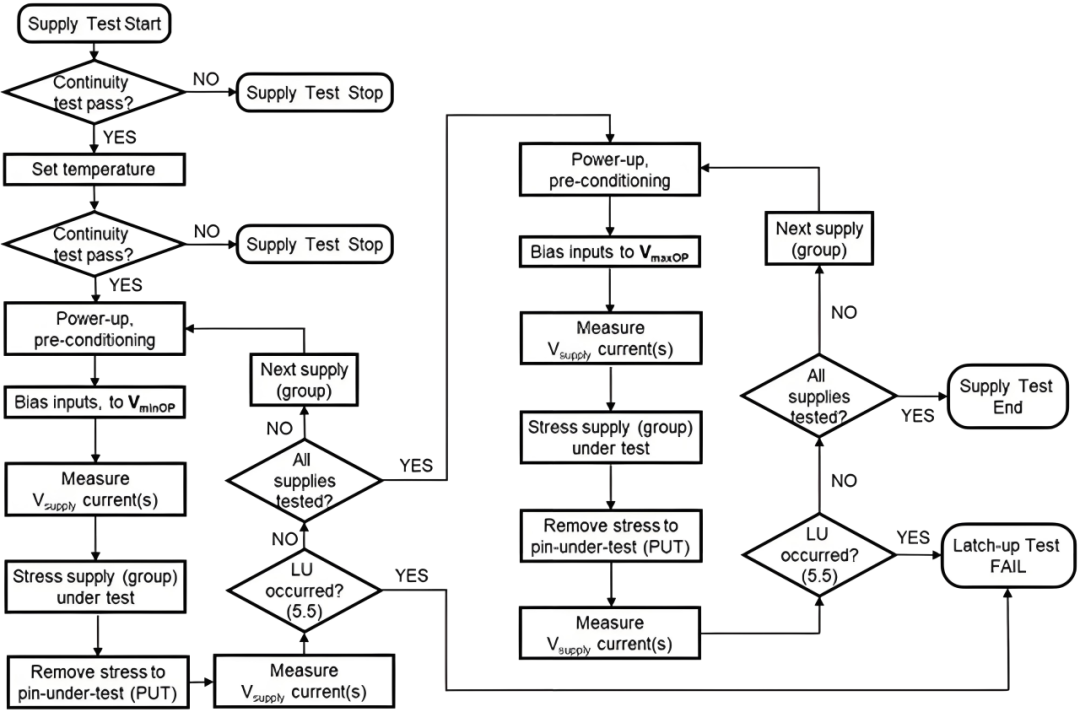

测试流程:

1.上电:按照指定的上电顺序给设备上电;

2.测量标称供电电流:在最大供电电压VmaxSUP下测量每个供电引脚(或供电引脚组)的Isupply;

3.施加触发电压,并在此期间量测应力电源(Stress Supply)的电流、电压,以及相关电源引脚的电压(Vsupply(s));

4.监测电源电流,达到以下条件则判定闩锁触发:

a.测试后电流值超出测试前电流值10mA;

b.测试后电流值超过测试前电流值的1.4倍。

电源引脚测试流程图

为什么Latch Up测试是非做不可的 “防线”?

进行符合JEDEC JESD78F.02标准的Latch Up测试,绝非可有可无,而是贯穿芯片研发、量产到市场准入的核心环节。

01可靠性认证的 “准入门槛”

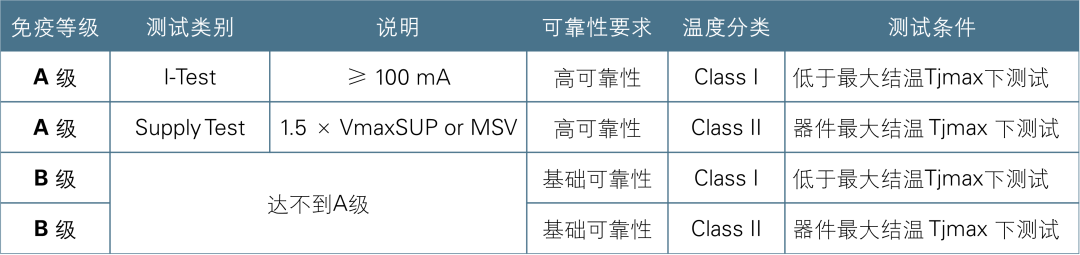

●等级划分:

根据测试结果,器件可划分为免疫等级A(高可靠性)或B(基础等级),并标注温度分类(Class I/II,Class II需在Tjmax下测试)。

●行业合规:

满足汽车电子(如AEC-Q100)、工业控制等领域对器件抗干扰能力的强制要求。

Latch Up免疫等级划分

点击查看大图

注:如有特殊需求,可以采取更严苛条件执行测试。

02研发与量产的 “质量防线”

●设计优化:

在芯片研发阶段定位寄生结构缺陷,指导版图优化(如增加保护环、调整阱结构);

●量产管控:

通过抽样测试(最小3件样品)筛查工艺波动导致的闩锁风险,避免批量缺陷;

●失效分析:

结合脉冲源验证和热成像技术,精准定位失效引脚或结构。

03成本与风险的 “平衡点”

●早期测试成本仅为现场失效维修成本的1/100,尤其对复杂SoC、功率器件等高价值产品至关重要;

●符合JEDEC标准的测试报告可直接用于客户审核,缩短产品上市周期。

SGS专业服务:从标准到落地的全流程支持

作为国际公认的测试、检验和认证机构,SGS依据JEDEC JESD78F.02标准,可为你提供:

●定制化测试方案

针对特殊引脚设计专属测试流程,规避误判风险;

●高精度测试设备

配备带温度控制的闩锁测试仪,支持宽温域测试,满足Class II严苛要求;

●权威合规报告

出具含免疫等级、温度分类及失效分析的中英文报告,助力产品全球市场准入。

-

芯片

+关注

关注

463文章

54438浏览量

469400 -

集成电路

+关注

关注

5464文章

12686浏览量

375742 -

半导体

+关注

关注

339文章

31245浏览量

266589

原文标题:干货分享 | 半导体良率提升关键:基于JEDEC标准的Latch Up测试

文章出处:【微信号:SGS半导体服务,微信公众号:SGS半导体服务】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高低温试验是什么?测试标准有哪些?

HDMI接口的ESD器件选择(二):闩锁效应的防范及解除

时识科技牵头制定动态视觉传感器性能测试方法国家标准

基于JEDEC JEP183A标准的SiC MOSFET阈值电压精确测量方法

开关电源有哪些测试流程和方法?

CMOS集成电路中闩锁效应的产生与防护

PCBA应力测试:从标准方法到产业实践的可靠性守护

汽车充电桩出厂要做哪些标准的测试

医疗设备泄漏电流测试全:IEC 60601标准解读与德国GMC测试方案

静电的起因与静电效应:技术分析与应用摘要

基于JEDEC标准的闩锁效应测试方法

基于JEDEC标准的闩锁效应测试方法

评论