前言: 当业界为2纳米之后的物理极限未雨绸缪,一条名为“Chiplet”(芯粒)的技术路径正将半导体创新从晶圆厂引向封装厂。它允许多个采用不同工艺、来自不同厂商的芯粒,像组建“联盟”一样通过先进封装(如CoWoS)集成在一起,共同构成一个更强大的系统级芯片。然而,当这个功能强大、成员各异的“芯片联盟”被密封在同一个封装体内,一个前所未有的挑战随之浮现:我们该如何为这个高度异构、内部紧密协作的“微系统”,进行一次确保其长期稳定运行的“终极体检”? 传统的单体芯片测试方法,在这个联盟面前已经彻底失效。

一、 趋势洞察:从“单体检测”到“系统级验证”的范式革命

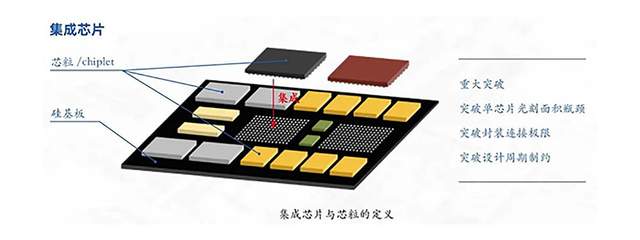

Chiplet技术被视为延续摩尔定律经济效益的关键,其核心优势在于通过异构集成提升性能、降低成本和加速上市。然而,这也从根本上改变了芯片测试的范式和对象。测试的目标不再是单个、均质的硅片,而是一个在封装后才首次形成的完整电子系统。

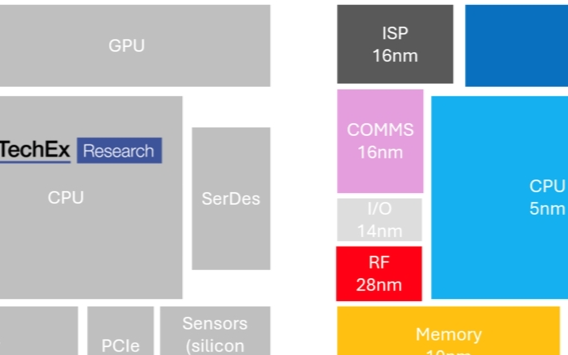

这个“系统”的复杂性体现在:它可能包含采用5纳米工艺的计算芯粒、12纳米工艺的I/O芯粒、以及来自第三方的存储芯粒或模拟芯粒。它们通过硅中介层或基板上的高密度互连线(如UCIe标准)通信,共享电源和散热路径。因此,传统的在晶圆测试(CP)和最终测试(FT)之间清晰的职责划分被打破,测试重心必须后移,聚焦于封装完成后的 “系统级测试(System Level Test, SLT)” 与 “互连及协同功能验证” 。这不仅是测试地点的变化,更是测试哲学、技术和工具的全面升级。

二、 技术挑战:“芯片联盟”体检的三大难关

为这样一个异构“联盟”提供可靠的“体检”报告,需要攻克三大核心难关,它们共同定义了Chiplet时代测试的复杂性:

1.互连通道的“信号完整性”极限测试

芯粒间互连(如UCIe)的数据速率已步入数十Gbps的超高速领域。在封装后,微米级的走线长度差异、中介层的材质缺陷、或热应力引起的形变,都可能导致信号完整性(SI)的劣化,引发间歇性的高误码率。测试必须在实际工作频率下,对每一条关键高速通道进行误码率(BER)扫描、眼图分析和串扰评估,而这在封装后有限的可访问性下极为困难。

2.系统级的“功耗与热”协同管理验证

不同芯粒的功耗特性、工作状态(激活/休眠)可能差异巨大,它们被紧密封装后,会产生复杂的相互热影响和电源噪声耦合。测试需要模拟真实应用场景,验证在最坏情况功耗负载下,电源配送网络(PDN)能否稳定供电,局部热点是否会导致某个芯粒降频或失效,以及整个系统的热管理方案是否有效。

3.异构系统的“协同配置”与烧录

Chiplet系统在启动前,需要为各个芯粒分别载入正确的固件、微码、驱动程序和特定的协同配置参数(如互连训练参数、功耗管理策略)。这个过程(烧录)变得异常复杂:它本质上是为多个独立的“大脑”同时、有序地安装操作系统和协作协议。 必须确保多源头、多协议的数据流能准确、同步地注入,并能在系统启动时被正确读取和识别。

三、 解决方案:构建面向“系统联盟”的智能体检中心

应对上述挑战,需要构建一套全新的、能够理解并验证“芯片联盟”整体健康的智能测试与配置体系:

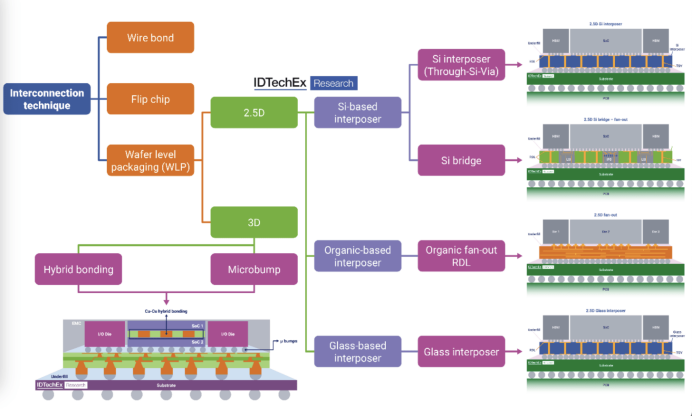

基于硅基板的“内窥镜”式测试访问:为了在封装后仍能对内部互连进行高精度测试,需要借助硅转接板(Interposer)上预留的专用测试通道或先进的可测试性设计(DFT),如边界扫描(JTAG)链的增强版本,以实现对关键节点的可控与可观。这如同为封装体安装了“内窥镜”。

仿真驱动的系统级测试(SLT)与监控:在接近最终使用环境的板卡上,运行真实的操作系统和应用软件,进行长时间、高负载的系统级压力测试。同时,集成先进的功耗与热监控传感器,实时采集并关联分析每个芯粒乃至关键模块的功耗、温度与性能数据,绘制出系统的“协同工作健康图谱”。

支持多协议、多任务的协同烧录引擎:烧录设备需进化成为一个 “协同配置管理器” 。它需要具备同时处理多种底层通信协议(如PCIe, I2C, SPI, 专用Die-to-Die协议)的能力,并能根据预设的“配置剧本”,有序地向不同芯粒分发数据、验证回读,并最终生成一份涵盖所有成员的、统一的烧录与配置完成报告。

结语:

Chiplet将半导体的创新从单一的硅片,拓展到了整个封装系统。这场“超越摩尔”的征程,成功与否不仅取决于设计和封装的能力,更取决于我们能否在最后关头,为这个精密的“芯片联盟”提供一份令人信服的、关于其长期协同作战能力的“健康证明”。

在您看来,推动Chiplet大规模落地的最大测试障碍是什么?是缺乏统一的可测试性标准,是系统级测试的过高成本,还是协同烧录的工程复杂度? 欢迎在评论区分享您的洞察与挑战。当芯片学会“团队作战”,我们的检验技术,也必须跟上这场进化。在这一前沿领域,与具备系统级验证视野和深度协议整合能力的伙伴合作,正成为将Chiplet蓝图转化为可靠产品的关键路径。

审核编辑 黄宇

-

芯片测试

+关注

关注

6文章

161浏览量

21085 -

chiplet

+关注

关注

6文章

485浏览量

13508

发布评论请先 登录

探秘半导体“体检中心”:如何为一颗芯片做静态参数测试?

Chiplet核心挑战破解之道:瑞沃微先进封装技术新思路

Chiplet封装设计中的信号与电源完整性挑战

Chiplet,改变了芯片

CMOS 2.0与Chiplet两种创新技术的区别

临港汽车软件联盟首场技术沙龙来袭!共探“AI如何为OS赋能”|活动预告

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

奇异摩尔受邀出席第三届HiPi Chiplet论坛

Chiplet 颠覆芯片创新,一文看懂计算平台大厂 Arm 的布局蓝图

2.5D集成电路的Chiplet布局设计

解锁Chiplet潜力:封装技术是关键

超越摩尔:Chiplet时代如何为“芯片联盟”进行终极体检?

超越摩尔:Chiplet时代如何为“芯片联盟”进行终极体检?

评论