一、Chiplet技术的定义与背景

Chiplet技术,也被称为小芯片或芯粒技术,是一种创新的芯片设计理念。它将传统的大型系统级芯片(SoC)分解成多个小型、功能化的芯片模块(Chiplet),然后通过先进的封装技术将这些模块连接在一起,形成一个完整的系统。这一技术的出现,源于对摩尔定律放缓的应对以及对芯片设计复杂性和成本控制的追求。

随着半导体技术的不断发展,芯片集成度不断提高,单片SoC的设计难度和成本也随之增加。同时,不同功能模块对工艺制程的需求差异,使得单片SoC难以满足所有性能要求。Chiplet技术通过模块化设计,允许设计师根据实际需求选择不同工艺制程的芯粒进行组合,从而有效解决了这些问题。

二、Chiplet技术的优势

(一)提高设计灵活性和可扩展性

模块化设计

Chiplet技术采用模块化设计思想,将芯片功能分解成多个独立的芯粒。这种设计方式使得设计师可以根据实际需求,灵活选择和组合不同的芯粒,从而快速实现不同功能的产品。例如,对于需要高性能计算的应用,可以选择高性能的CPU芯粒和GPU芯粒进行组合;对于需要低功耗的应用,则可以选择低功耗的芯粒进行组合。

可扩展性

Chiplet技术的可扩展性体现在多个方面。首先,它允许设计师通过增加或减少芯粒的数量,轻松调整芯片的性能和功耗。其次,随着新技术的不断出现,设计师可以很方便地将新的芯粒集成到现有系统中,实现产品的快速升级和迭代。这种可扩展性使得Chiplet技术在应对快速变化的市场需求时具有显著优势。

(二)降低设计成本和制造成本

设计成本

Chiplet技术通过模块化设计,降低了芯片设计的复杂度。设计师可以将复杂的SoC设计分解成多个相对简单的芯粒设计,从而降低设计难度和成本。此外,由于芯粒可以独立设计和验证,因此可以并行开展多个芯粒的设计工作,进一步缩短设计周期。

制造成本

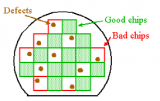

Chiplet技术通过优化工艺流程和减少浪费,降低了芯片的制造成本。首先,由于芯粒尺寸较小,因此可以在同一晶圆上制造更多的芯粒,提高晶圆利用率。其次,由于芯粒可以独立制造和测试,因此可以在制造过程中及时发现和修复缺陷,减少废品率。最后,由于Chiplet技术允许使用不同工艺制程的芯粒进行组合,因此可以选择成本更低的工艺制程来制造非关键性能的芯粒,从而降低整体制造成本。

(三)提高芯片良率和可靠性

提高良率

Chiplet技术通过将大型SoC分解成多个小型芯粒,降低了每个芯粒的制造难度和缺陷率。由于芯粒尺寸较小,因此更容易实现高质量的制造过程。此外,由于芯粒可以独立测试和筛选,因此可以在制造过程中及时发现和剔除缺陷芯粒,提高整体良率。

提高可靠性

Chiplet技术通过优化封装设计和散热设计,提高了芯片的可靠性。首先,先进的封装技术可以实现芯粒之间的高密度、低延迟互连,减少信号传输过程中的损耗和干扰。其次,通过合理的散热设计,可以有效降低芯片的工作温度,提高芯片的长期可靠性。

(四)加速产品上市时间和创新速度

加速上市时间

Chiplet技术通过模块化设计和并行开发,显著缩短了产品的上市时间。设计师可以独立设计和验证每个芯粒,然后将其组合成完整的芯片系统。这种并行开发方式使得设计师可以更快地响应市场需求和变化,推出更具竞争力的产品。

加速创新速度

Chiplet技术为芯片创新提供了新的思路和方向。设计师可以根据实际需求,灵活选择和组合不同的芯粒,实现新的功能和应用。此外,由于Chiplet技术允许使用不同工艺制程的芯粒进行组合,因此可以更容易地实现跨代工艺的创新和融合。

三、Chiplet技术的挑战

(一)互连技术的挑战

高速互连需求

Chiplet技术需要实现芯粒之间的高速互连,以满足高性能计算和低延迟通信的需求。然而,随着芯粒数量的增加和互连距离的延长,互连带宽和延迟成为制约Chiplet技术发展的关键因素。因此,如何开发高效、可靠的互连技术成为Chiplet技术面临的重要挑战。

信号完整性问题

在Chiplet系统中,由于芯粒之间互连密度高、距离短,信号完整性问题变得尤为突出。信号反射、串扰和抖动等问题可能导致信号失真和传输错误,影响芯片的性能和可靠性。因此,如何确保信号在互连过程中的完整性和稳定性成为Chiplet技术需要解决的关键问题。

(二)封装技术的挑战

先进封装技术需求

Chiplet技术需要采用先进的封装技术来实现芯粒之间的高密度、低延迟互连。然而,先进封装技术的研发和制造成本较高,且技术难度较大。因此,如何降低先进封装技术的成本和提高其可靠性成为Chiplet技术面临的重要挑战。

封装热管理问题

在Chiplet系统中,由于芯粒数量多、功耗大,封装热管理问题变得尤为突出。高温可能导致芯片性能下降和可靠性降低,甚至引发封装失效。因此,如何有效散热和降低封装温度成为Chiplet技术需要解决的关键问题。

(三)测试与验证的挑战

测试复杂度增加

Chiplet技术将传统的大型SoC分解成多个小型芯粒,增加了测试的复杂度。每个芯粒都需要进行独立测试和验证,以确保其功能和性能符合要求。此外,在将芯粒组合成完整的芯片系统后,还需要进行整体测试和验证,以确保系统的稳定性和可靠性。因此,如何降低测试复杂度和提高测试效率成为Chiplet技术面临的重要挑战。

测试标准缺失

目前,Chiplet技术缺乏统一的测试标准和规范。不同制造商和设计师采用不同的测试方法和工具进行测试和验证,导致测试结果的可比性和可信度降低。因此,如何制定统一的测试标准和规范成为Chiplet技术需要解决的关键问题。

(四)生态系统建设的挑战

生态系统不完善

Chiplet技术需要一个完整的生态系统来支持其发展和应用。然而,目前Chiplet技术的生态系统还不完善,缺乏统一的设计工具、制造工艺和测试平台等。这导致Chiplet技术的研发和应用受到一定限制。因此,如何完善Chiplet技术的生态系统成为其面临的重要挑战。

产业链协同问题

Chiplet技术涉及多个产业链环节,包括设计、制造、封装和测试等。这些环节之间需要紧密协同和合作,才能实现Chiplet技术的有效应用和发展。然而,目前产业链各环节之间的协同和合作还存在一定问题,导致Chiplet技术的推广和应用受到一定阻碍。因此,如何加强产业链协同和合作成为Chiplet技术需要解决的关键问题。

四、Chiplet技术的发展趋势与展望

(一)技术发展趋势

互连技术不断创新

随着Chiplet技术的不断发展,互连技术将不断创新和完善。未来,将出现更多高效、可靠的互连技术,以满足Chiplet系统对高速互连和低延迟通信的需求。

封装技术持续进步

封装技术作为Chiplet技术的关键支撑之一,将持续进步和发展。未来,将出现更多先进、可靠的封装技术,以实现Chiplet系统的高密度、低延迟互连和有效散热。

测试与验证技术不断完善

随着Chiplet技术的不断发展和应用,测试与验证技术将不断完善和提高。未来,将出现更多高效、准确的测试方法和工具,以降低测试复杂度和提高测试效率。

(二)市场前景展望

市场需求不断增长

随着人工智能、物联网、5G通信等新兴技术的快速发展,对高性能、低功耗芯片的需求不断增长。Chiplet技术凭借其独特优势,将在这些领域发挥重要作用,并迎来广阔的市场前景。

产业链协同发展

未来,随着Chiplet技术的不断发展和应用,产业链各环节之间的协同和合作将不断加强。这将有助于推动Chiplet技术的创新和发展,并促进整个半导体产业的进步和升级。

国际合作与竞争并存

在全球化背景下,Chiplet技术的国际合作与竞争将并存。一方面,各国将加强在Chiplet技术研发、制造和应用等方面的合作与交流;另一方面,各国也将在Chiplet技术市场上展开激烈竞争。这种国际合作与竞争并存的局面将有助于推动Chiplet技术的快速发展和应用。

五、结语

Chiplet技术作为一种创新的芯片设计理念,凭借其提高设计灵活性和可扩展性、降低设计成本和制造成本、提高芯片良率和可靠性以及加速产品上市时间和创新速度等优势,在半导体领域展现出巨大的潜力和广阔的前景。然而,Chiplet技术也面临着互连技术、封装技术、测试与验证以及生态系统建设等方面的挑战。未来,随着技术的不断创新和完善以及市场需求的不断增长,Chiplet技术有望克服这些挑战并实现快速发展。同时,国际合作与竞争也将推动Chiplet技术的不断进步和应用拓展。

-

芯片

+关注

关注

462文章

53539浏览量

459168 -

soc

+关注

关注

38文章

4514浏览量

227631 -

chiplet

+关注

关注

6文章

482浏览量

13504

发布评论请先 登录

KLA发布全新汽车产品组合以提高芯片良率及可靠性

芯片IC可靠性测试、静电测试、失效分析

【PCB】什么是高可靠性?

什么是高可靠性?

单片机应用系统的可靠性与可靠性设计

单片机应用系统的可靠性特点

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

Chiplet:芯片良率与可靠性的新保障!

Chiplet:芯片良率与可靠性的新保障!

评论