在电子工程领域,A/D转换器一直是连接模拟世界和数字世界的关键桥梁。今天,我们将深入探讨德州仪器(TI)的一款高性能、低功耗8位、500 MSPS A/D转换器——ADC08500,了解它的特性、应用以及设计要点。

文件下载:adc08500.pdf

一、ADC08500特性概览

1. 高性能与低功耗

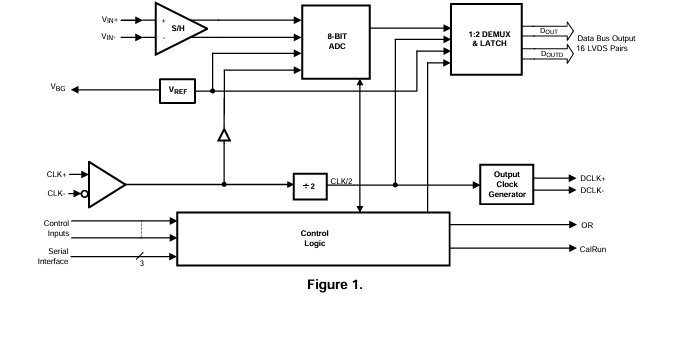

ADC08500采用独特的折叠和内插架构,在实现7.5有效位数的同时,大大降低了比较器数量和功耗。它在500 MSPS的采样率下,仅消耗0.8W的典型功率,而在掉电模式下,功耗可降至3.5mW。

2. 灵活的输出时钟选项

提供单数据速率(SDR)或双数据速率(DDR)输出时钟选择,用户可以根据实际需求灵活配置。同时,输出数据可以选择在DCLK的上升沿或下降沿转换,方便数据捕获。

3. 多ADC同步能力

通过DCLK_RST脉冲,ADC08500能够精确重置采样时钟输入与DCLK输出的关系,实现多个ADC的同步,确保多个ADC的DCLK和数据输出在共享CLK输入下同时转换。

4. 扩展控制模式

支持扩展控制模式,通过串行接口访问基于寄存器的控制,提供更多的配置和控制选项,如输入满量程范围调整、输入偏移调整等。

5. 自校准功能

上电时自动进行自校准,也可由用户按需触发。校准过程可以微调100Ω模拟输入差分终端电阻,最小化满量程误差、偏移误差、DNL和INL,提高SNR、THD、SINAD和ENOB。

二、关键规格参数

1. 分辨率与转换速率

分辨率为8位,最大转换速率可达500 MSPS,位错误率低至10⁻¹⁸(典型值)。

2. 动态性能

在250 MHz输入时,有效位数(ENOB)可达7.5位(典型值),具有良好的信号噪声比(SNR)、总谐波失真(THD)和无杂散动态范围(SFDR)。

3. 功耗

工作时功耗为0.8W(典型值),掉电模式下功耗为3.5mW(典型值)。

三、功能描述与设计要点

1. 自校准

自校准是ADC08500的重要功能之一。上电时,校准过程会自动启动,也可以通过将CAL引脚拉低至少tCAL_L个时钟周期,然后拉高至少tCAL_H个时钟周期来手动触发。校准过程中,所有时钟会暂停,以减少噪声。需要注意的是,校准期间输出数据无效,且不能在掉电模式下进行校准。

2. 输入采集

数据在CLK+引脚的下降沿采集,D输出总线在13个时钟周期后、Dd输出总线在14个时钟周期后可获得数字等效数据。ADC08500采用全差分比较器设计和创新的采样保持放大器,结合自校准功能,实现了超过500 MHz的平坦SINAD/ENOB响应。

3. 控制模式

ADC08500支持正常控制模式和扩展控制模式。在正常控制模式下,通过控制引脚实现基本的配置和控制;在扩展控制模式下,通过串行接口访问寄存器,提供更多高级功能。两种模式的选择通过FSR/ECE引脚确定,且不建议在设备运行时动态切换。

4. 模拟输入

ADC08500必须使用差分输入信号,推荐采用交流耦合或直流耦合方式。在正常模式下,通过FSR引脚选择输入满量程范围;在扩展控制模式下,通过编程输入满量程电压调整寄存器进行调整。同时,输入共模电压必须保持在VCMO±50 mV范围内,以确保最佳性能。

5. 时钟

ADC08500需要交流耦合的差分时钟信号驱动。时钟输入内部有终端和偏置,时钟信号必须电容耦合到时钟引脚。时钟频率应在规定范围内,以确保设备的可靠性和性能。此外,ADC08500还提供了占空比校正时钟接收器,提高时钟稳定性。

6. LVDS输出

数据输出、超出范围(OR)和DCLK均采用LVDS接口。输出电流源根据OutV引脚的状态提供不同的输出电流,用户可以根据系统需求选择正常或降低的输出电平。同时,通过连接VBG引脚到电源,可以提高LVDS输出的共模电压。

7. 掉电模式

当PD引脚为高电平时,ADC08500进入掉电模式,输出引脚进入高阻态,功耗降至最低。在掉电模式下,手动校准输入将被忽略,且返回正常操作时,流水线中的数据无效。

四、应用信息与注意事项

1. 参考电压

ADC08500的参考电压来自1.254V的带隙参考,通过VBG引脚提供给用户。该输出具有±100 μA的输出电流能力,如需更多电流,应进行缓冲。内部带隙参考电压的标称值由FSR引脚确定,不支持外部参考电压,但可以在扩展控制模式下通过配置寄存器调整输入满量程电压。

2. 模拟输入处理

处理单端输入信号时,建议将其转换为差分信号后再输入到ADC08500。对于交流耦合输入,可以使用合适的巴伦进行转换;对于直流耦合输入,可以使用LMH6555等放大器实现单端到差分的转换。同时,要注意输入共模电压的稳定性,确保其在VCMO±50 mV范围内。

3. 时钟输入

时钟输入对ADC08500的性能至关重要。时钟信号必须是交流耦合的差分信号,且频率应在规定范围内。为了避免抖动引起的噪声,时钟源应具有低均方根抖动。同时,时钟线应尽量短,远离其他信号,并作为传输线处理。

4. 控制引脚

六个控制引脚(FSR、CAL、CalDly、OutEdge、OutV和PD)提供了丰富的控制功能,如输入满量程范围设置、自校准、校准延迟、输出边缘同步、LVDS输出电平选择和掉电功能。在使用这些引脚时,要注意避免在校准过程中进行不必要的数字活动,以免影响校准结果。

5. 数字输出

ADC08500将输出数据解复用至两个LVDS输出总线,每个总线的字速率为ADC输入时钟速率的一半。用户需要将两个总线的数据进行复用,以获得完整的转换结果。同时,可以选择SDR或DDR时钟模式,根据OutEdge引脚确定数据在DCLK的上升沿或下降沿输出。

6. 电源考虑

A/D转换器需要良好的电源旁路,以避免瞬态电流对电源的干扰。建议在ADC电源引脚附近放置33 μF和0.1 μF的电容,并使用铁氧体磁珠隔离VA和VDR电源引脚。同时,应选择低噪声的电源,避免使用开关电源,或在使用时注意其布局和放置。

7. 热管理

尽管ADC08500在低功耗下实现了高性能,但仍需要注意热管理。为了确保设备的可靠性,芯片温度应控制在130°C以下。可以通过将封装背面的暴露焊盘连接到PCB的热焊盘,并使用热过孔和散热片来提高散热效率。

8. 布局与接地

正确的布局和接地对于确保ADC08500的准确转换至关重要。建议使用单一接地平面,避免将接地平面分割为模拟和数字区域。同时,要将模拟电路和数字电路分开,避免数字噪声对模拟信号的干扰。

五、常见应用陷阱与避免方法

1. 扩展控制模式下的寄存器写入

在使用扩展控制模式时,必须先将三个用户寄存器至少写入一次默认值或所需值,然后才能进行校准和后续使用。

2. 输入电压限制

为了确保设备的可靠性,输入电压不应超过电源引脚150 mV或低于接地引脚150 mV。在设计高速数字电路时,要注意控制信号的过冲和下冲。

3. 模拟输入共模电压

在直流耦合模式下,输入共模电压必须保持在VCMO±50 mV范围内,以避免失真性能下降。

4. 放大器选择

选择驱动ADC08500的放大器时,要确保其具有足够的噪声和失真性能,以及在应用频率下的增益。

5. 时钟信号处理

时钟信号应具有低抖动,时钟线应尽量短,远离其他信号。避免使用过长的时钟信号走线或与其他信号耦合。

6. 散热问题

要提供足够的散热措施,确保设备的可靠性。可以通过良好的空气流动或在PCB中内置散热片来实现。

六、总结

ADC08500是一款高性能、低功耗的A/D转换器,具有丰富的功能和灵活的配置选项。在设计应用时,需要充分了解其特性和规格参数,注意各个环节的设计要点,避免常见的应用陷阱。只有这样,才能充分发挥ADC08500的性能优势,实现高质量的模拟到数字转换。希望本文能为电子工程师在使用ADC08500时提供有价值的参考。你在使用ADC08500的过程中遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

MSPS

+关注

关注

0文章

562浏览量

28770 -

数据输出

+关注

关注

0文章

19浏览量

9340 -

数据速率

+关注

关注

0文章

53浏览量

12243

发布评论请先 登录

ADC08500,pdf datasheet (High P

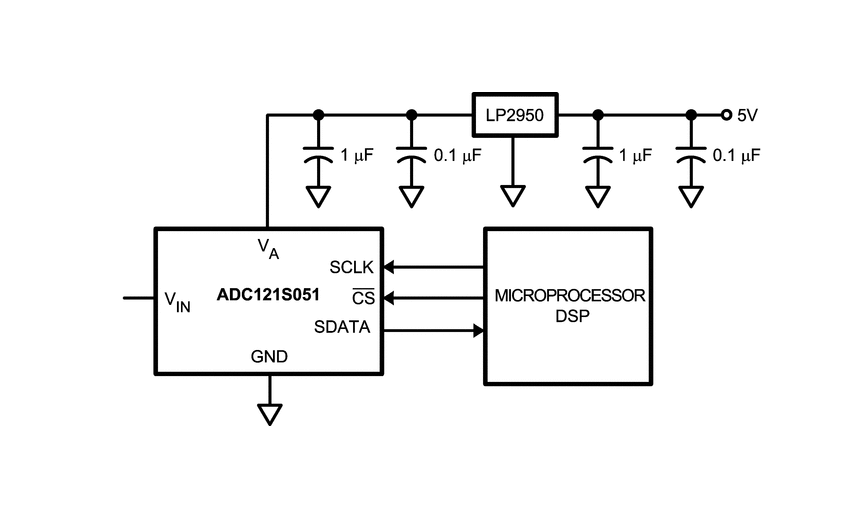

深入剖析ADC121S051:高性能单通道12位A/D转换器的设计与应用

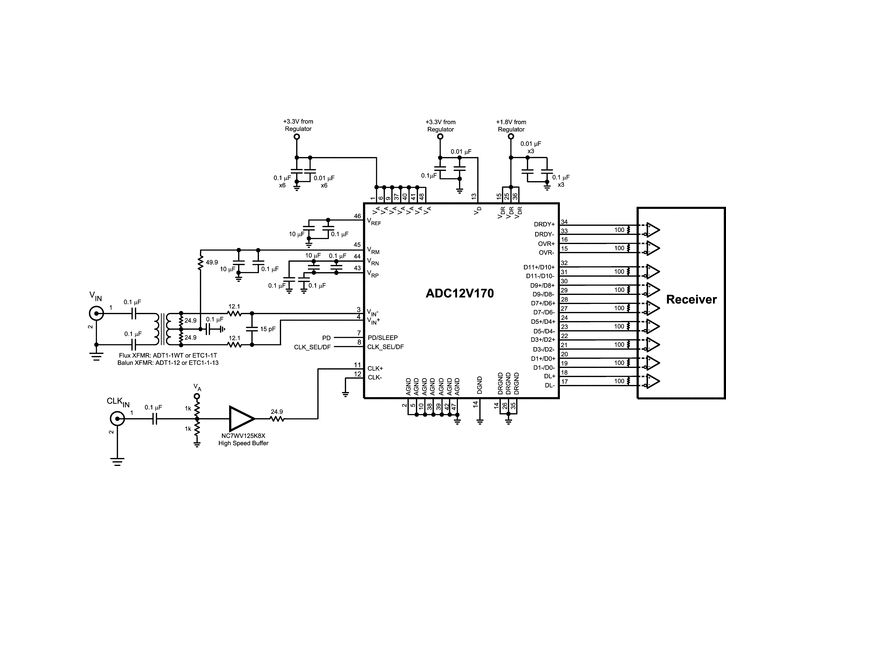

深入解析ADC08D500:高性能低功耗8位500 MSPS A/D转换器

深入剖析ADC124S101:高性能12位A/D转换器的卓越之选

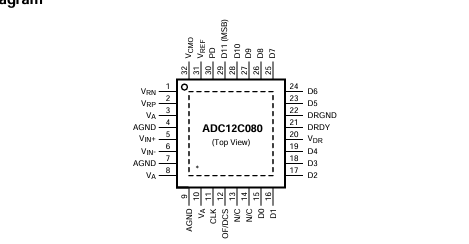

深入剖析ADC12DL080:高性能12位A/D转换器的设计与应用

深入解析ADC081S101:高性能8位单通道A/D转换器

深入剖析ADC08500:高性能8位500 MSPS A/D转换器的设计与应用

深入剖析ADC08500:高性能8位500 MSPS A/D转换器的设计与应用

评论